# TIMING MODELS FOR MOS CIRCUITS

By Mark Alan Horowitz

January 1984

Prepared under

US Army Research Office

Contract No. DAAG-29-80-K-0046

Integrated Circuits Laboratory

Stanford Electronics Laboratories

Stanford University, Stanford, California

© Copyright 1984 by Mark Alan Horowitz

# Abstract

Performance is an important aspect of integrated circuit design, and depends in part on the speed of the underlying circuits. This thesis presents a new method of analyzing MOS circuit delay, based on a single-time-constant approximation. The timing models characterize the circuit by a single parameter, which depends on the resistance and capacitance of the circuit elements. To ensure the **single**-time-constant approximation is valid for a particular circuit, the timing models provide both an estimate and bounds for the output waveform. For circuits where the bounds are poor, an improved timing model is derived. These simple models provide insight about circuit performance issues, as well as determining the circuit delay.

The timing models are first developed for linear networks and then are extended to model MOS circuits driven by a step input. By using the single-time-constant approximation, the output waveform of a complex MOS circuit can be modelled by the output of a circuit consisting of a single MOS transistor and a single capacitor.

Finally, a new circuit model of a gate is used to derive the output waveform of a circuit driven by an arbitrary input. The resulting timing model does not depend strongly on the shape of the input: the output waveform only depends on the input's slope at the gate's switching voltage.

|  |  |  | • |

|--|--|--|---|

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

# **Table of Contents**

| 1 | INTRODUCTION                                                                                                                                                                 |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1 Delay Estimation                                                                                                                                                         |

|   | 1.2 Organization                                                                                                                                                             |

| 2 | DELAY ESTIMATION TECHNIQUES                                                                                                                                                  |

|   | 2.1 Linear System Analysis                                                                                                                                                   |

|   | 2.2 Circuit Simulation                                                                                                                                                       |

|   | 2.3 System Timing Analysis                                                                                                                                                   |

|   | 2.4 MOS Gate Delay Models                                                                                                                                                    |

|   | 2.5 Summary                                                                                                                                                                  |

|   |                                                                                                                                                                              |

| 3 | LINEAR NETWORKS                                                                                                                                                              |

|   | 3.1 Overview                                                                                                                                                                 |

|   | 3.2 Modelling Transistor Clusters                                                                                                                                            |

|   | 3.3 Qualitative Analysis                                                                                                                                                     |

|   | 3.4       Single-Time-Constant Model                                                                                                                                         |

|   | 3.4.3 Computational Requirements                                                                                                                                             |

|   | 3.4.4 Time Constant Interpretation                                                                                                                                           |

|   | 3.4.5 Improved $\tau_{Re}$                                                                                                                                                   |

|   | 3.5Two-Time-Constant Model303.5.1 Waveform Estimate313.5.2 Physical Interpretation343.5.3 Bounds Improvement when $\tau_P >> \tau_{De}$ 353.5.4 Computational Requirements36 |

|   | 3.6 Connecting Two RC Trees                                                                                                                                                  |

|   |     | 3.6.2 Two-Time-Constant Model                                                                                                                                                                                          |

|---|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.7 | Summary                                                                                                                                                                                                                |

| 4 | NON | NLINEAR NETWORKS                                                                                                                                                                                                       |

|   | 4.1 | Overview                                                                                                                                                                                                               |

|   | 4.2 | Problems with Linear Models                                                                                                                                                                                            |

|   | 4.3 | Qualitative Analysis                                                                                                                                                                                                   |

|   | 4.4 | Single-Time-Constant Model464.4.1 Nonlinear Circuit Transformation474.4.2 Waveform Estimate484.4.3 Waveform Bounds494.4.4 Computational Requirements51                                                                 |

|   | 4.5 | MOS Circuits       52         4.5.1 MOS Transistors       52         4.5.2 Falling Transient       54         4.5.3 Rising Transient       55         4.5.4 Comparison with Timing Models for Linear Networks       57 |

|   | 4.6 | Two-Time-Constant Model584.6.1 Waveform Estimate594.6.2 Bounds Improvement62                                                                                                                                           |

|   | 4.7 | Mixed Nonlinear Elements                                                                                                                                                                                               |

|   | 4.8 | Summary                                                                                                                                                                                                                |

| 5 | SLC | OWINPUTS ,                                                                                                                                                                                                             |

|   | 5.1 | Introduction                                                                                                                                                                                                           |

|   | 5.2 | Gate Models                                                                                                                                                                                                            |

|   | 5.3 | Simple Gates                                                                                                                                                                                                           |

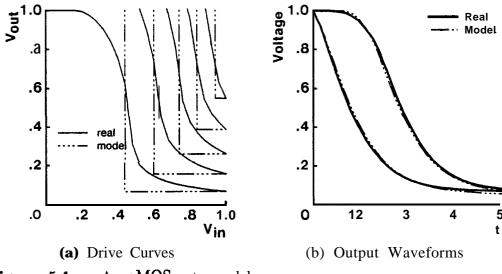

|   | 5.3.4 MOS Gates            | 83  |

|---|----------------------------|-----|

|   | 5.4 Complex Gates          | 87  |

|   | 5.5 Summary                | 93  |

| 6 | CONCLUSIONS                | 97  |

|   | 6.1 Future Work            |     |

| Α | VOLTAGE BOUNDS IN RC TREES | 01  |

|   | A.1 Simple Bounds          |     |

| В | RCMESHES                   | 105 |

| С | BOUNDS IMPROVEMENT         | 07  |

| D | MOS BOUNDS DERIVATION , ,  | 113 |

|   | D.1 Falling Transient      |     |

|   | DEEEDENICES                | 117 |

|  |  | <u>.</u> |

|--|--|----------|

|  |  |          |

|  |  |          |

|  |  |          |

|  |  |          |

|  |  |          |

|  |  |          |

|  |  |          |

|  |  |          |

|  |  |          |

|  |  |          |

|  |  |          |

|  |  |          |

|  |  |          |

|  |  |          |

# List of Figures

| 2.1  | An nMOS transistor cluster                                          |

|------|---------------------------------------------------------------------|

| 3.1  | A nMOS transistor cluster                                           |

| 3.2  | An RC tree                                                          |

| 3.3  | Output of a uniform RC line                                         |

| 3.4  | Output waveform of a circuit with three coincident poles            |

| 3.5  | Output waveform of a circuit with a low-frequency pole-zero pair 21 |

| 3.6  | Output bounds for a circuit with a low-frequency pole-zero pair 26  |

| 3.7  | Output bounds for a distributed RC line                             |

| 3.8  | Algorithm to find $\tau_{De}$ in linear time                        |

| 3.9  | Circuit with a poor $\tau_{Re}$                                     |

| 3.10 | Improved output bounds using $\hat{	au}_{Re}$                       |

| 3.11 | Two-time-constant Estimate                                          |

| 3.12 | Output from the begining of a long RC line                          |

| 3.13 | Two- tree model                                                     |

| 3.14 | Single-time-constant two-tree output                                |

| 3.15 | Two-tree output with a low-frequency pole-zero pair                 |

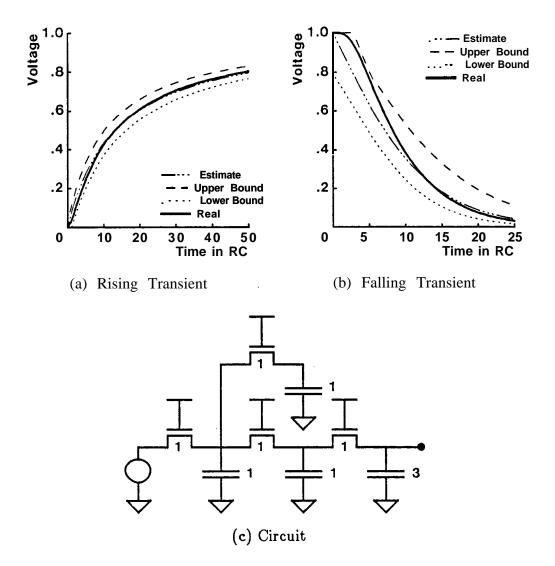

| 4.1  | MOS pass net output waveforms                                       |

| 4.2  | A nonlinear RC tree                                                 |

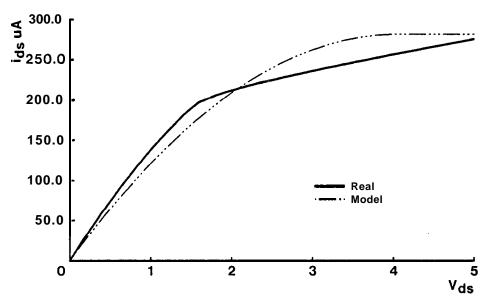

| 4.3  | $4\mu$ nMOS transistor i-V curve                                    |

| 4.4  | Transient output waveform for a simple pass network                 |

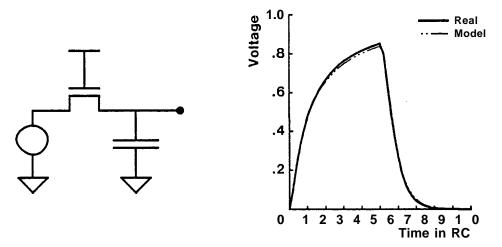

| 4.5  | Pass transistor estimate and bounds                                 |

| 4.6  | Two-time-constant output waveform 61                                |

| 4.7  | Circuit for a rising transient in nMOS                              |

| 4.8  | A mixed nonlinear circuit                                           |

| 4.9  | Output for a mixed nonlinear circuit                                |

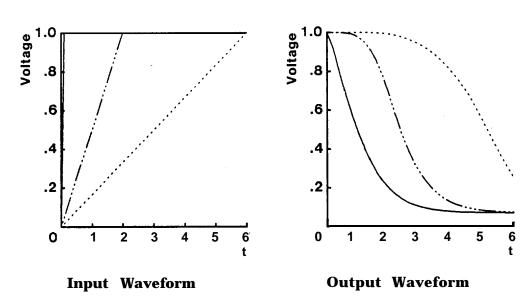

| 5.1  | Gate output waveform for different input waveforms      |

|------|---------------------------------------------------------|

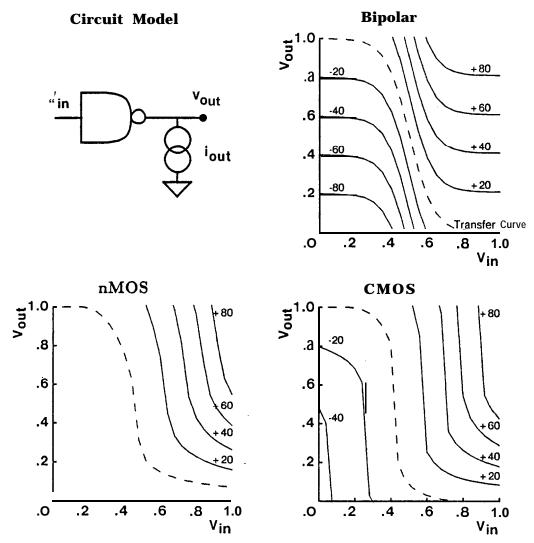

| 5.2  | Drive Curves for different types of gates               |

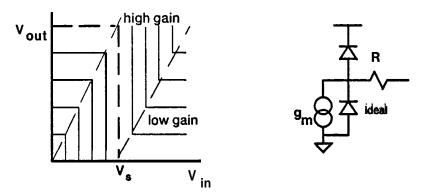

| 5.3  | Idealized drive curve and resulting gate model          |

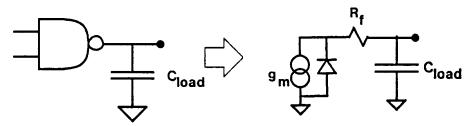

| 5.4  | An nMOS gate model                                      |

| 5.5  | A simple gate                                           |

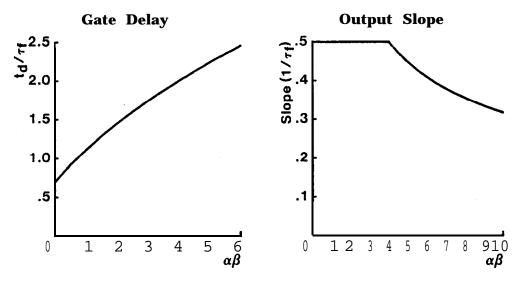

| 5.6  | Gate delay and output slope versus input ramp rise time |

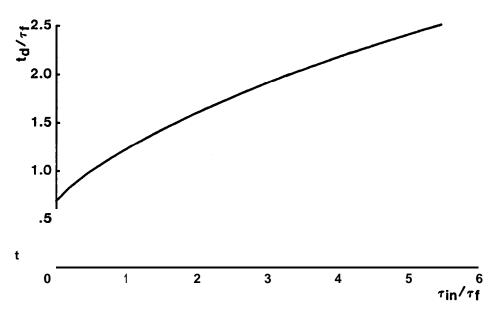

| 5.7  | Gate delay for an exponential input                     |

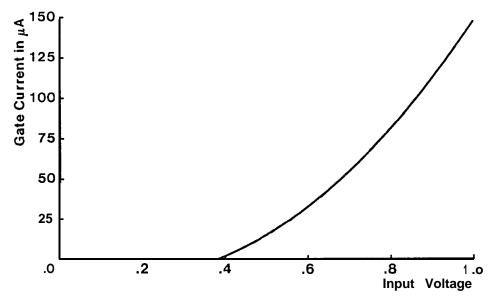

| 5.8  | Output current vs. input voltage for an nMOS gate       |

| 5.9  | Circuit model for a complex gate                        |

| 5.10 | Conversion from a complex gate into a simple gate       |

| 5.11 | Output of a complex gate for different input slopes     |

| 6.1  | Output estimates of the timing models                   |

| B.l  | Two simple RC meshes                                    |

| c.1  | Replacing a capacitor with a voltage source             |

| c.2  | Improved bounds for an RC tree with a pole-zero pair    |

|      |                                                         |

# List of Symbols

- $\alpha$  The rise time of the input normalized to the time constant of the gate; the input takes  $\alpha \tau_f$  to ramp from 0 to full scale.

- $\alpha_{ke}$  A lower bound on  $V_k/V_e$  for two nodes in an RC tree.

- $\beta_{ke}$  An upper bound on  $V_k/V_e$  for two nodes in an RC tree.

- $C_k$  The capacitance at node k in an RC tree. For two-tree circuits, a second subscript indicates which tree the capacitor is in:  $C_{k_1}$  is in tree 1.

- $C_T$  Total capacitance of the output network of a logic gate.

- e A node in an RC tree, usually an output node.

- f(V) A transformation of variables that converts a nonlinear resistor into one that is pseudo-linear.

- $\tau_{De}$  minus the integral of  $U_e$  ( $V_e$  for a linear network).

- $g_m$  The forward transconductance of a logic gate evaluated at the gate's switching voltage.

- k A node in an RC tree, usually used as a summing index.

- $R_{ke}$  In an RC tree, the resistance from the root to the last node on the path to both node e and node k. Thus,  $R_{kk}$  is simply the total resistance from node k to the root. In two-tree circuits, a second subscript indicates which tree is being referenced.

- $R_r(R_f)$  The effective resistance of a logic gate in the low-gain region for a rising (falling) transient.

- t<sub>d</sub> The time required for the output of a transistor cluster to reach the switching point of the next gate after the gate's input crosses its switching voltage.

- The time when a logic gate enters the low-gain region of its drive curves. For bounds, a second subscript is used to indicate whether this time is an upper (u) or lower (1) bound.

- T(t) The output waveform for a single- time-constant nonlinear circuit.

- $au_{\alpha e}$  A lower bound on the time constant of output e's slow mode in a nonlinear circuit.

- $au_{m{eta e}}$  An upper bound on the time constant of output e's slow mode in a non-linear circuit.

- $au_{De}$  An estimate of the output's time constant. A ' superscript indicates the time constant is for a two-tree circuit.

- $\tau_f$  The time constant of a logic gate driven by a step input.

- $au_{in}$  Time constant of the input waveform. For a ramp input,  $au_{in}$  is the inverse slope; for an exponential input, it is the exponential's time constant.

- An estimate of the coefficient of the  $s^2$  term in node e's frequency response divided by  $\tau_P$ .

- $au_P$  An upper bound on the lowest frequency time constant of any output in a linear network, and is equal to the sum of the open circuit time constants. A ' indicates the time constant is for a two-tree circuit.

- $au_{Re}$  A lower bound on the lowest frequency time constant of output e in a linear network. A  $\hat{}$  superscript indicates an improved bound; ' indicates the time constant is for a two-tree circuit.

- $au_1$  An estimate of the time constant caused by the first resistor in a mixed nonlinear circuit.

- $\tau_1, \tau_2$  An estimate of the lowest two poles of node e's frequency response.

- $\tau_z$  An estimate of the lowest frequency zero of node e's frequency response.

- $V_e$  The voltage at node e, usually an output voltage of the tree.

- $V_e^*$  An estimate of the voltage at node e.

- $V_k$  The voltage at node k.

- $V_{\bullet}$  The switching voltage of a logic gate.

- $U_e$  The transformed voltage at node e,  $f(V_e)$ .

- $U_{\bullet}^{*}$  An estimate of the transformed voltage at node e.

# Acknowledgments

Without the help of many people, this thesis would not have been possible; even with their help, there were times when I still had my doubts. First and foremost, I would like to thank my parents and my friends Tom and Jeannie Blank, and Barbara Lee for keeping me going even when I thought the situation was dismal.

This thesis has benefitted from many helpful discussions I have had during my stay at Stanford. Tom Blank, Robert White, Paul Penfield, Chuck Seitz, Robert Mathews, John Newkirk, and Robert Dutton deserve special mention for reading drafts of this work and providing valuable feedback. I would like to thank John Newkirk and Robert Mathews for asking me a question about MOS circuit delay that eventually lead to the work presented in this thesis, and for their helpful discussions throughout. I am also grateful for the opportunity to work with Paul Penfield. He is still the only person I know who, after a 2 minute conversation, can point out the mistakes in my arguments. Finally, I would like to thank my advisor, Robert Dutton, who has patiently watched, supported, and guided me on my trek to find a thesis topic, and then helped refine the material into its present form.

This work was supported in part by the ARO under research contract DAAG-29-80-K-0046. The author's support by an IBM Fellowship during the 1981-1982 school year is also gratefully acknowledged.

### INTRODUCTION

**A** million-transistor integrated circuit (IC) may sound impressive, but if it cannot out-perform a thousand-transistor integrated circuit, what use is it? Performance is an important aspect of an IC and depends on two factors: the chip's micro-architecture and the speed of the underlying circuits. To develop a successful chip, the designers must consider both factors. The best micro-architecture can be made ineffectual by slow circuits, and fast circuits are wasted in a poor architecture.

Integrated circuit designers have many tools at their disposal to help them estimate the performance of a chip. At an architectural level, the tools determine how many primitive operations (clock cycles) the IC requires to complete a desired task. At a circuit level, the tools numerically estimate the delay through the internal gates. Unfortunately these circuit-level tools only can analyze small designs. They cannot simulate the entire chip to determine the time needed to perform a primitive operation at an architectural level. This thesis bridges the gap between architectural tools and circuit tools by providing a conceptually and computationally simple method of modelling the delay through Metal Oxide Semiconductor (MOS) integrated circuits.

### 1.1 Delay Estimation

Determining a chip's performance directly is difficult because it is a large, nonlinear circuit; an IC can contain tens of thousands of signals and hundreds of thousands of devices. However, the limited interactions in a digital system allow the IC to be partitioned into many smaller subcircuits. The chip delay then can be determined by estimating the delay through the subcircuits. Partitioning the circuit

#### 2 Introduction

converts the chip performance estimation problem into many simpler subcircuit problems.

Currently, designers use empirical models to estimate subcircuit delays. They determine the delay's dependence on the circuit parameters by numerically simulating many circuits and performing curve fitting on the results. The disadvantages of this technique are lack of error control in the resulting models and difficulty in relating the delay back to the circuit elements.

This thesis describes a single- time-constant approximation for generating **sub**-circuit timing models. This approximation allows the output waveform to be characterized by a simple sum of resistances and capacitances. The timing model is **computationally** simple, making it attractive for large MOS circuits. More importantly, the close relationship between device parameters and the timing model makes it easier **for** a designer to determine a component's effect on the total delay. Thus, the timing models not only estimate how fast a circuit will operate, when necessary they also can help designers determine how to speed up the circuit.

Most subcircuit outputs can be approximated by single-time-constant estimates. To ensure the validity of this approximation, bounds on the output waveform also are derived. When the bounds are poor, the estimate is not a good model of the output, and an improved estimate and bounds are derived by using a more complex model of the output waveform. The use of bounds removes the biggest limitation of simple timing models — the uncertainty in the overall accuracy.

# 1.2 Organization

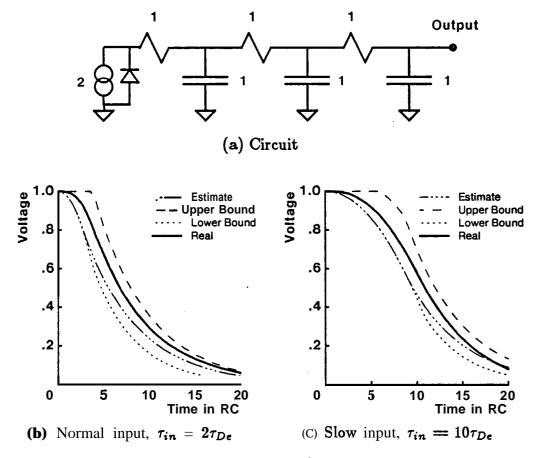

The next chapter describes earlier work in delay modelling. To apply systemanalysis techniques to MOS integrated circuits, the chip must be partitioned into transistor *clusters*, sub-circuits that can be viewed as digital logic blocks. From transistor cluster delays, the chip delay can be easily determined. Chapter 3 introduces a timing model for transistor clusters based on a linear transistor model. By approximating transistors by linear resistors, transistor clusters become linear RC trees. A timing model using the single-time-constant approximation, and following the derivation of Rubinstein, Penfield, and Horowitz [RP83] yields an estimate and bounds on the output waveform. These models are then extended to include systems without a single, dominant, time constant.

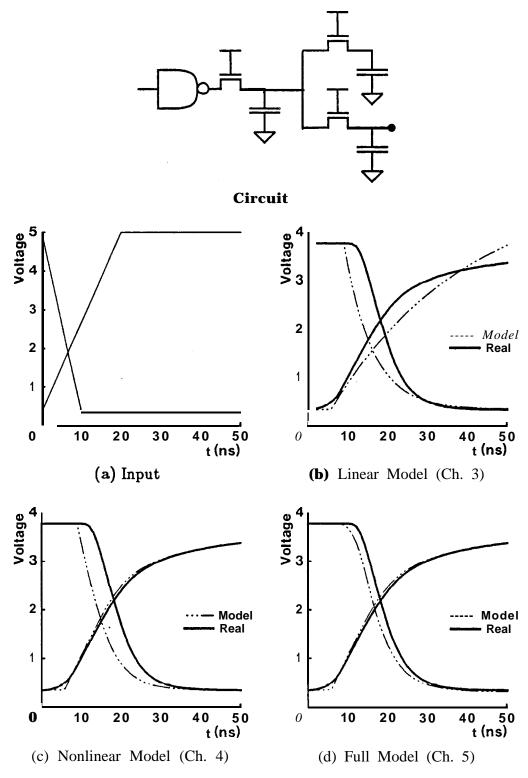

Chapter 4 removes the restriction that MOS transistors be modelled as linear resistors. By looking at MOS transistors in a new way, the response of the nonlinear network can be found using techniques analogous to the linear derivation. Again, a single-time-constant model (both estimate and bounds) for MOS transistor clusters is derived, which is similar, but not identical, to those for linear networks. The similarity explains why the linear models work well; the differences show where they will fail to be accurate. For circuits with multiple time constants, an improved timing model is generated, again using the same basic technique as was used to improve the linear models.

Chapter 5 describes the effect the input waveform has on the output of a transistor cluster. When the input changes gradually with time, to determine the output voltage requires modelling the output current of a logic gate versus input and output voltages. The resulting model is quite simple and can be used to show why certain gates are more sensitive to input slope than others. It leads to improved timing models for transistor clusters. For fast input waveforms, these models reduce to those derived in Chapter 3 and 4. For slow inputs, the delay through the transistor cluster increases but it is only weakly coupled to the shape of the input waveform. The input's slope at the gate's switching voltage is sufficient to predict the output waveform.

Finally, Chapter 6 presents a synopsis of delay modelling and summarizes the contributions of this thesis. Areas for further investigations are also described.

# **DELAY ESTIMATION TECHNIQUES**

Historically, tools for designing integrated circuit logic components **have been** very different from the tools for constructing systems from these integrated circuits. The design of a logic component is an analog design problem. Tools must model the electrical elements used to determine the circuit's digital characteristics: its delay, noise margins, and power dissipation. On the other hand, in large system design, the models of the underlying building blocks are digital. The system design tools use a simplified model of logic components. The digital model hides the analog aspects of the problem from the designer and the tools, allowing larger systems to be designed.

As the complexity of integrated circuits increases, the line between component and system design becomes increasingly fuzzy. Delay analysis tools for these complex circuits must merge component-analysis techniques, to determine the subcircuit delays, with system-analysis techniques, to compose subcircuit delays to yield the chip delay.

# 2.1 Linear System Analysis

In the 1940s, systems were neither digital nor integrated; they were multi-stage, analog, tube amplifiers. Although design techniques for these analog amplifiers might seem outdated compared to digital MOS VLSI design, the basis of the old analog analysis techniques — the single-time-constant approximation — can be used to generate MOS timing models.

### 6 Delay Estimation Techniques

Prior to the late 1960s, performance estimation techniques were computationally simple, since all calculations were done by hand. To simplify the analysis problem, all nonlinear elements were approximated by linear models. By looking at small voltage excursions around an operating point (small-signal analysis), each nonlinear element could be replaced by an effective linear element [GS69]. The response of this linearized circuit was obtained using frequency-domain analysis, since the circuit's frequency response H(s), the Laplace transform of the system's impulse response h(t), could be determined directly from the circuit schematic [TA65].

The performance of an amplifier can be estimated from the low frequency terms of H(s), since they dominate the output waveform. The single-time-constant approximation models the response of the amplifier by a system with a single pole [TA65]. In 1948, Elmore reported that, for a step input, the delay through a linear amplifier was roughly equal to the first moment of its impulse response and that the output rise time was approximately  $\sqrt{2\pi}$  times the second moment of the impulse response minus the first moment squared [El48]. Based on the relationship between the moments of h(t) and the derivatives of H(s), the delay and rise time can be found from the frequency response. More sophisticated estimates for the output waveform have subsequently been developed, including output bounds; however, the basic approach, using the low frequency terms to estimate the output, has remained the same.

Unfortunately, frequency domain analysis is valid only for linear networks. When nonlinear elements are present, superposition, and therefore Laplace transform techniques, do not apply. The growth of digital integrated circuits provided both the impetus for nonlinear analysis techniques — the circuits are intrinsically nonlinear — and an inexpensive method of performing the required computation

$<sup>^{\</sup>dagger}A$  good review of this work is in [TA65], especially Chapter 8.

digital computers. Circuit simulation programs developed during the late 1960s

provided a method to estimate the performance of nonlinear circuits.

#### 2.2 Circuit Simulation

A circuit simulation program computes output waveforms from a description of the circuit and its input waveforms. Second-generation programs, like SPICE2 [Na75] and ASTAP-II [WJ73], have become an essential tool for integrated circuit designers. The simulator makes finding circuit delays easy. The delay is simply the amount of time between an input change and the corresponding change in the simulated output voltage. For circuits with multiple inputs and outputs, the only additional difficulty is choosing the input combination that gives the longest delay.

A circuit simulator uses numerical methods to solve the set of coupled nonlinear differential equations that define the time dependence of the nodal voltages [CL75]. The program generates the equations by first using device models to relate device currents to terminal voltages and then applying Kirchhoff's current law to obtain each capacitor current in terms of the other device currents. The net result is a set of equations relating the change in nodal voltages to the nodal voltages. Using vector notation, this set of equations can be written as

$$\mathbf{v}' = f(\mathbf{v}),\tag{2.1}$$

where v is the vector of dependent nodal voltages — nodes not driven by a voltage source.

Numerically integrating these equations provides an estimate of the output waveform. Explicit integration methods are computational simple, but cannot be

<sup>&</sup>lt;sup>†</sup>Assuming that the circuit and devices are modelled accurately, and that the simulation converges [Pe82]. Simulators must solve a large set of coupled nonlinear equations to generate the initial dc solution. This task is very difficult, especially for complex circuits.

used in a general program because they have poor numerical stability. Implicit integration methods are more complex because finding the output voltages at each time step requires solving a set of nonlinear algebraic equations:

$$\mathbf{v}_{n+1} = \mathbf{v}_{n+1} f(\mathbf{v}_{n+1})(t_{n+1} - t_n), \tag{2.2}$$

Circuit simulators solve Eq. (2.2) by using Newton's method. The  $m^{th}$  Newton-Raphson interation involves finding the Jacobian of  $f(\mathbf{v}_{n+1}^m)$  and then solving the resulting set of linear equations to generate  $\mathbf{v}_{n+1}^{m+1}$ , the new estimate. When the difference between the new estimate and the old estimate is smaller than a set tolerance, the simulator increments the time point and the process is repeated.

Since simulators use an implicit integration method, the maximum error in the voltage estimates can be controlled by the user. Obtaining this error control, however, requires evaluating every device model at each time step and then solving a large set of nonlinear equations. As a result, circuit simulators work best with relatively small circuits.

Macro-modelling is a technique developed in the mid 1970s to help simulators analyze large circuits [RR78]. For MOS designs, the strategy was to reduce the number of nodes required to represent a circuit by eliminating all nodes internal to a logic gate [Ra73]. This simplification is possible because the internal dynamics of a gate are normally not important. Although simulators could analyze larger circuits using macro-models, simulation of the entire chip was still impossible.

To estimate the performance of MOS circuits too large for circuit simulators, a faster technique, timing simulation, was developed. The programs MOTIS [CG75] and MOTIS-C [FH77] are similar to circuit simulators in that they numerically integrate nonlinear differential equations, but they use a simplified set of equations and a simplified solution method to speed program execution. An undesirable effect of these simplifications is an increase in the uncertainty of the result; the output error can be bounded only for a limited class of circuits.

Timing simulation is based on a gate-level, rather than a transistor-level, description of the circuit. Gate macro-models lower the number of nodal voltages which must be determined. To reduce program execution time further, timing simulation only evaluates changing nodes. It updates gates with changing inputs; gates with stable inputs are ignored. Since at any particular time, most of the nodes have a stable voltage, i.e. are latent, only a small fraction of the circuit needs to be evaluated at each time step. Exploiting circuit latency together with the other simplifications make timing simulation about two orders of magnitude faster than circuit simulation.

Recently there has been work on third generation circuit simulators [HS81, LS82, SK83]. These programs are roughly the same speed as timing simulation, but maintain the accuracy and error control of circuit simulation. Although these new programs hold great promise as circuit analysis tools, they do not solve the delay modelling problem. The new programs still suffer from two problems fundamental to all numerical simulators: slow execution speed — the programs are still orders of magnitude too slow to use to analyze an entire MOS IC — and an inability to provide information on what causes the circuit delay.

Although a simulation program can determine the delay, it cannot diagnose why the circuit is slower than expected or indicate how the delay can be reduced. Solving the numerical equation yields the correct. answer but does not find the right question. This information can be obtained only when the analysis tool understands the circuits being evaluated. The result of this limitation is that experienced MOS designers use SPICE to get a feel for the technology — to calibrate their internal models — in addition to using it to analyze a particular circuit.

As the next section will show, for digital systems, the problem of estimating the delay through a large circuit can be transformed into a problem of estimating the delay through thousands of subcircuits. However, this transformation only is useful if a good subcircuit timing model exists.

# 2.3 System Timing Analysis

Even in the 1960s, digital systems were large and, as a result, complexity was a major issue. The controlled interactions in such a system was used to limit the complexity of simulation. Because these systems are constructed from digital circuit blocks (logic gates) the analog nature of the circuits are hidden by the external digital model. A simulator for logic need only model the delay and logical function of each block.

The controlled interaction of digital gates also enables logic simulation programs to exploit circuit latency. Since a gate is unidirectional, its output can change only if one of its inputs change. Evaluating only gates that have changing inputs (selective trace), rather than all possible gates, greatly reduces the number of evaluations at each time step.

Unfortunately, logic simulation only gives the delay for the input changes that are tested. Unless all possible machine states are tested, there is no guarantee that the longest delay found during logic simulation is the longest delay for the system. To remove this limitation, value-independent timing analysis or timing verification was developed in 1966 [KC66], butwas not applied to system design until the early 1980s, for example [McW80, Mo82]. This timing analysis uses only the timing portion of the logic specification. Without the logical description, the timing specification becomes a signal flow graph; signals flow into gates, experience some delay, and then leave. The delay through any path from an input to an output is simply the sum of the delays of the gates on that path. More important, the worst-case delay through the logic can be determined by using a PERT scheduling algorithm, whose time complexity is linear in the number of gates.

In the early 1970s IC designers began putting large systems onto a single MOS chip. Since these circuits were too complex for circuit simulation tools, the designers turned to logic simulation and timing analysis to estimate the circuit delay. Before

these tools could be applied to MOS designs, two questions needed to be answered: what are the <code>logic</code> blocks for MOS circuits, and what are the delays through these logic blocks? When systems were built from bipolar SSI and MSI integrated circuits, the answers to these questions were obvious; the logic blocks were the <code>ICs</code>, and the delays were published as part of the IC specification. For large integrated circuits, the answers were no longer as clear.

# 2.4 MOS Gate Delay Models

The digital model is an abstraction that suppresses the analog nature of the input and output waveforms, and represents the circuit by a boolean function. Another constraint of digital circuits is unidirectionality: a block's input is not affected by its output. Both logic simulation and timing analysis use this constraint when they assume changes only propagate from the inputs of a block to its output.

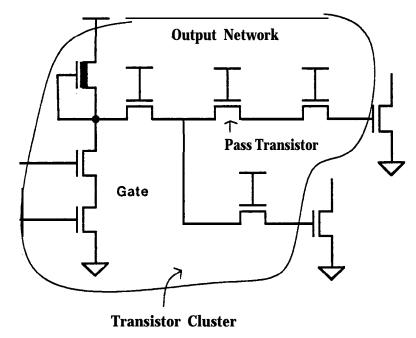

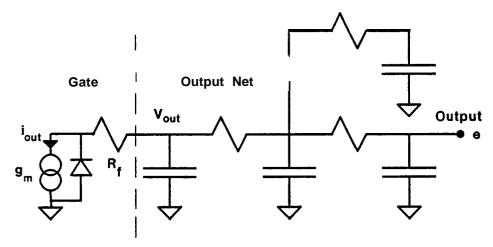

A logic block is any subcircuit that can be accurately represented by a digital model. In MOS circuits, MOS transistors provide unidirectional coupling. The transistor's gate voltage affects its source and drain voltages, but the reverse coupling is small and can be ignored. † The MOS transistors also provide gain, so the details of their gate voltages has a minor affect on their outputs. Thus a MOS logic block is a subcircuit whose inputs and outputs are all connected to the gates of MOS transistors. Logic blocks that cannot be subdivided into smaller logic blocks are referred to as transistor clusters; see Figure 2.1.

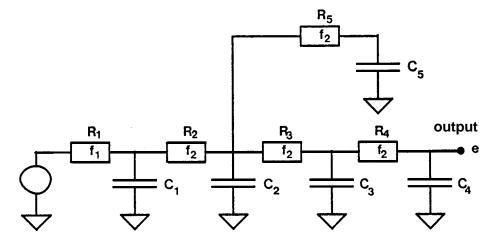

**A** transistor cluster can be viewed as an MOS logic gate and its associated output network. The output network includes any pass transistor network connected to the gate's output as well as the parasitic resistance and capacitance of the

<sup>&</sup>lt;sup>†</sup>The reverse coupling is capacitive coupling between the source and drain and the gate. For most timing questions this coupling is small enough that it can be ignored; an effective grounded capacitor can be used instead.

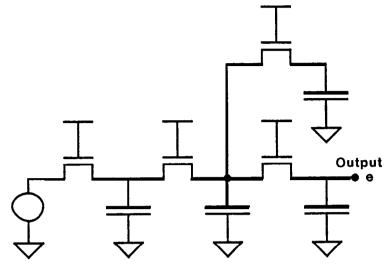

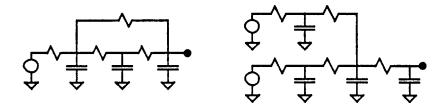

Figure 2.1 An nMOS transistor cluster

output wires. Both the gate and output network can be quite complex. The gate can be **a** large AND-OR-Invert structure and the output network can include **a** large pass network, or a complex wire tree. Wire **parasitics**, especially the wire capacitance, are an important component of the transistor cluster, and must be included for an accurate timing model. Fortunately, programs are available to extract parasitic capacitance [SA78] and resistance [HD83] from a layout description.

Initial attempts to create delay models for transistor clusters used circuit simulators to generate empirical timing models. Such empirical models limit the kinds of transistor clusters that can be modelled — a simple gate with a capacitor load is typical [PS72]. Although recent timing models can accommodate more complex transistor clusters [AD82, OM83], the models are still very limited.

These empirical MOS timing models are more complex than the bipolar gate models. In addition to having different rise and fall delays, the delay through a MOS transistor cluster depends on the slope of the input waveform. For accurate

timing analysis, this dependence means the shape of the signal during the transition is important; the timing models must determine both the delay and the slope of the output waveform.

In 1981, Penfield and Rubinstein presented a technique to bound the output waveform of a linear RC tree, based on a single-time-constant approximation [PR81]. This method can be applied to generate delay models for MOS transistor clusters by making two approximations: (1) modelling the input of the clusters by step waveforms, and (2) modelling conducting transistors by linear resistors. This technique has two advantages over empirical models. First, it can be applied to any type of transistor cluster, so a separate model for each type of cluster is no longer needed. In addition, it can relate the delay back to the circuit, showing which portions need improvement. As a result of its generality, this model was quickly incorporated into many MOS timing-analysis programs, for example, TV [Jo83] and Auto-Delay[Pu82].

The linear RC tree model has many limitations. Since transistors are not linear devices, their effective resistance values must be determined empirically. Although the timing model produces bounds, these waveforms only bound the output of the ideal linear model, not the output of the nonlinear circuit. The relationship between the model and the actual MOS circuit remains unchecked. The error in the estimated delay can be large even when the bounds are good because of the approximations used to derive the linear circuit model. Since the model provides no method to estimate or bound its error, the accuracy of results cannot be quantified.

This thesis generalizes the concepts used in finding bounds for RC trees — using the single-time-constant approximation — to generate improved timing models for MOS transistor clusters. In particular, the new models remove the need to model transistors as linear resistors and inputs as step waveforms. Thus, the waveform bounds of the new model provide a valid accuracy check on the timing estimate.

# 14 Delay Estimation Techniques

The next chapter begins by describing linear timing models for transistor clusters, since they form the foundation of the more advanced timing models.

# 2.5 Summary

The complexity of current MOS integrated circuits makes it infeasible to estimate a chip's delay directly using a circuit simulator. **A** chip contains too many nodes, even considering circuit latency, to numerically solve for the voltage at each node. Instead, the circuit must be viewed as a large digital system. The delay can then be estimated from the delays of its transistor clusters, the logic blocks for MOS circuits. Currently, designers use simple empirical timing models to estimate a transistor cluster's delay. The uncertainty resulting from the inaccuracy of the models is the main limitation of this technique.

### LINEAR NETWORKS

### 3.1 Overview

This chapter derives timing models for linear networks. To apply these models to a transistor cluster, MOS transistors must be approximated by linear resistors. Although this is a crude approximation, the resulting model provides a first-order estimate to the cluster's output waveform. The advantage of this linear approximation is that linear network theory can be used to help derive the timing models. The insight gained from the linear derivation is used in later chapters to derive more accurate timing models.

When MOS transistors are approximated by linear resistors, a transistor cluster becomes a linear RC tree. Because the model is linear, a qualitative description of the output waveforms can be found using frequency domain analysis. The insight gained from this analysis will guide the development of a more formal timing model. The derivation follows that of Rubinstein et al. † The resulting model uses three easily computed time constants to produce an estimate of and bounds on the output waveform of a linear RC tree. Estimating the output waveform avoids the difficult question of defining the delay for a system with slow rise and fall times. From the output estimate, the approximate time required for the voltage to reach any level can be determined.

<sup>&</sup>lt;sup>†</sup>Penfield and Rubinstein [PR81] developed the initial method for bounding the delay in RC trees. After reading their work, this author developed a simpler derivation, which yielded slightly better bounds. This improved derivation is presented in [RP83] and is used in this chapter.

The bounds serve to check the single-time-constant approximation used to generate the estimate. For some outputs, the estimate matches the real output, yet the bounds are poor. The bounds for these circuits can be improved by simply improving  $\tau_{Re}$ , one of the time constants used to generate the bounds. For other outputs, both the estimate and bounds poorly match the real output, because the real output does not have a single dominant time constant. To better represent these outputs, a two-time-constant estimate is derived.

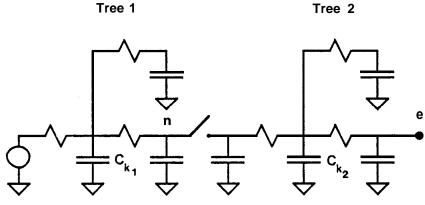

Finally, the timing models are extended to estimate the output of an RC tree driven by another RC tree. This situation occurs in MOS circuits when a pass transistor turns on, connecting a new network to the output of a previously settled gate. The extension also provides a method to estimate the output of a logic gate whose internal capacitance is not negligible.

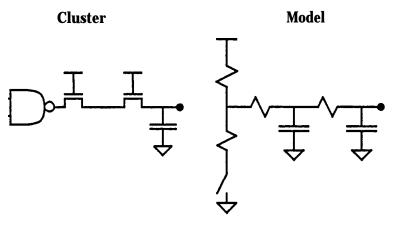

# 3.2 Modelling Transistor Clusters

A transistor cluster represents a logic gate and its associated output net; see Figure **3.1.** Although all the outputs of this cluster are logically equivalent, the voltages at the outputs need not be the same because of the resistance of the output net. Hence, a unique delay is needed for each physical output of the cluster. Both the gate and the output net must be characterized to generate a timing model for this structure. Two approximations simplify this task: the inputs to the cluster are modelled as step waveforms and conducting MOS transistors are modelled as linear resistors.

Transistors have only two possible states, if step inputs are assumed: fully conducting and not conducting. A transistor can be modelled as a non-linear resistor in series with a switch. The transistor's gate voltage controls the state of the switch. Using this model of a transistor, a resistor connected to ground models the logic gate for a low output; a resistor connected to the power supply models a high output.

Figure **3.1** A nMOS transistor cluster.

The value of the resistor is equal to the resistance through the pullup transistor(s) in the high state and is equal to the resistance through the pulldown transistor(s) in the low state. In nMOS, the pullup transistor is ignored in the low state since the resistance of the pulldown transistors is much less than the resistance of the pullup transistors. When the gate's output changes, the resistive path in the gate drives the output net, changing all the output capacitors from the old output value to the new value.

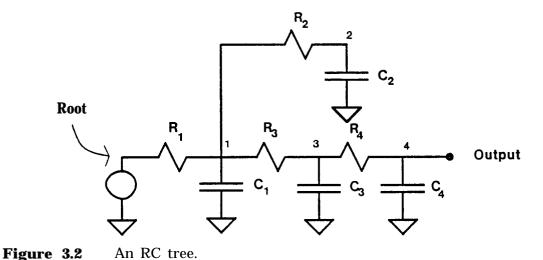

By using a linear resistor to model a conducting transistor, the circuit model of a transistor cluster becomes a linear RC tree: a network of floating resistors (possibly distributed RC lines) and grounded capacitors driven by a voltage source, where a unique resistive path exists from each capacitor to the voltage source.  $^{\dagger}$  Figure 3.2 shows an RC tree model of a transistor cluster. The node connected to the voltage source is called the root of the tree.

<sup>†</sup> This assumes there is a unique signal path from each capacitor in the output net to the gate's output. Although it is possible to have output nets with loops, these circuits are unusual. Rarely does a signal net split off only to recombine with itself. In the situation where loops are present, the model of a transistor cluster becomes an RC mesh: The timing mode is for these structures are very similar to models for RC trees; see Appendix B.

The voltage source and the first resistor  $(R_1)$  model the logic gate; the rest of the RC tree models the output network. When the logic gate changes state (because its inputs change), both the value of the voltage source and the first resistor  $(R_1)$  change. During a falling transition, the output of the voltage source is ground and the first resistor is equal to the resistance through the pulldown transistor; during a rising transition, the output of the voltage source is  $V_{power}$  and the first resistor is equal to the resistance through the pullup transistor. For determining the delay, the output network is assumed to have settled to the previous state before the new change occurs: output changes do not interact. Using this assumption, the output of a transistor cluster is equal to the output of an RC tree driven by a step voltage source. This assumption is quite good for digital circuits, but breaks down for circuits that use positive feedback in an attempt to improve circuit performance. This limitation is discussed further in Chapter 6.

## 3.3 Qualitative Analysis

Using the linear transistor model, a MOS logic gate driving a capacitor load is represented by a single-resistor, single-capacitor circuit; its output is a simple exponential. Surprisingly, the output of most complex transistor clusters can be

accurately approximated by an exponential waveform. To understand why the outputs are so simple requires looking at the frequency response of RC trees.

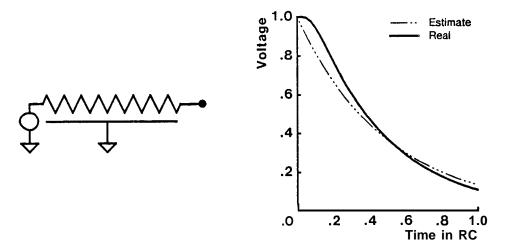

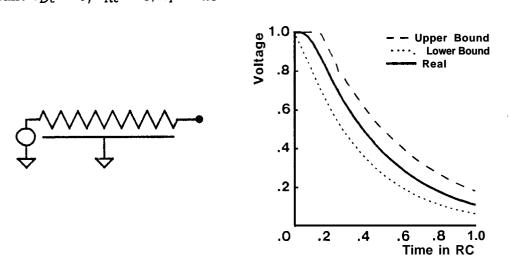

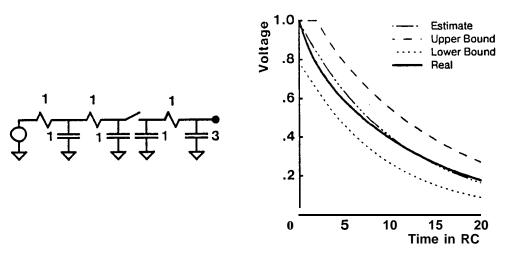

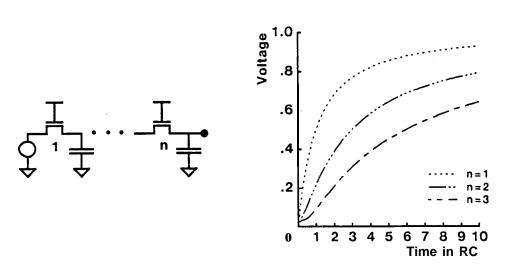

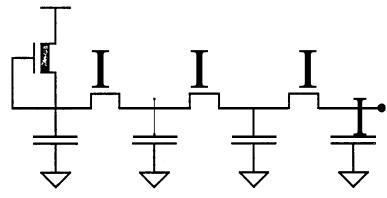

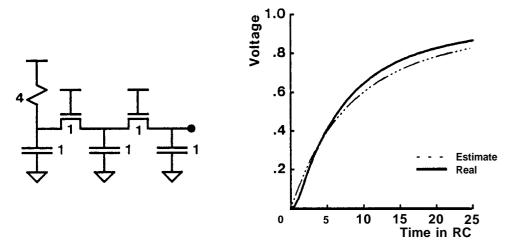

If an output can be well modelled by a single-resistor, single-capacitor circuit, then its frequency response must be dominated by a single pole. A dominant pole occurs when one pole is located at a much lower frequency than all the other poles and zeros.† In general, the output at the end of a series of identical elements has a single pole response. For example, the voltage at the end of a long polysilicon wire (modelled as a series of small RC sections) has a large number of poles, but is nicely approximated by an exponential; see Figure 3.3. The high frequency poles are most important during the initial transient, and here the approximation has its largest error. But even at its worst, the error is still small. Using a linear transistor model, the voltage at the end of a series of identical pass transistors resembles the output of an RC line and also can be approximated by an exponential. Adding a capacitive load at the end of an RC line (to model input or wire capacitance) lowers the frequency of the dominant pole, which means the single-pole estimate is an even better approximation to the real output.

There are two classes of linear networks that do not have a single-pole response. Circuits with coincident poles may have a group of low-frequency poles that dominate the output; circuits with a low-frequency pole-zero pair have a low-frequency zero that partially cancels the dominant pole, causing the output to have a two-time-constant behavior. Although these types of linear networks are easy to construct, they rarely arise as a model for a transistor cluster.

To understand why higher frequency poles are less important, consider a step traversing a series of filters. Each filter corresponds to a pole of the output's frequency response. If the lowest frequency pole is put first, then it will attenuate the input's high frequency components. Subsequent poles will have only a small effect, as all the high frequency components have already been attenuated. The larger the difference in pole frequencies the smaller the effect high frequency poles have on the output.

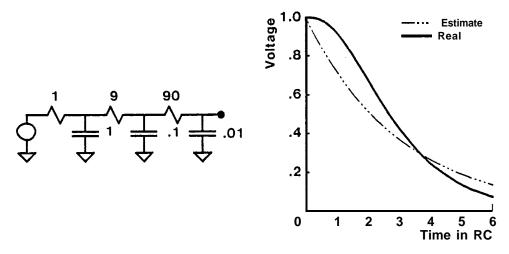

**Figure 3.3** Output of a uniform RC line.

**Figure 3.4** Output waveform of a circuit with three coincident poles.

Figure 3.4 shows a network with three closely spaced poles and its response. The large range in resistance and capacitance required to generate coincident poles means this type of circuit rarely occurs in MOS designs. The one exception is in modelling busses. Here the bus driver and the bus capacitance form the low impedance RC section, and the read circuitry form the high impedance section. If the time constants of the two sections are roughly equal, then the circuit will have two coincident poles.

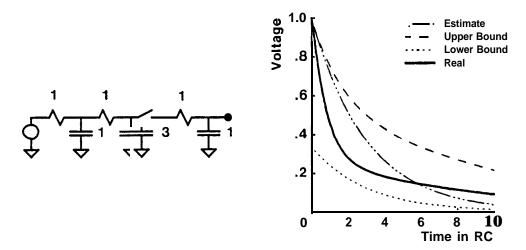

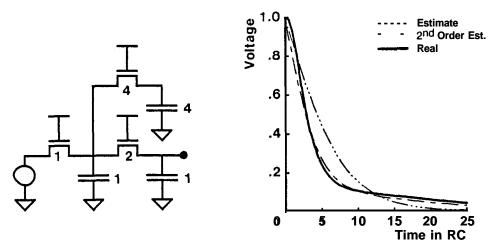

**Figure 3.5** Output waveform of a circuit with a low-frequency pole-zero pair.

An example of a network with a low-frequency pole-zero pair and its output waveform are shown in Figure 3.5. The presence of a low-frequency zero partially cancels the dominant pole, causing the output waveform to have a slowly decaying tail. Physically this type of output occurs when the dominate time constant in the circuit is caused by capacitance that is located on a side branch of the tree and not directly on the path from the root to the output. The voltage at the output initially decays quickly with a time constant caused by the local output capacitance, but eventually the voltage on the distant capacitance controls the output through a voltage divider. This type of circuit also is rare as a transistor cluster model because it requires one output of a gate to be much slower than another output of the same gate. Usually a designer creates a circuit so all the outputs have roughly the same timing. The one exception to this rule is in regular structures, where control wires run in polysilicon and drive many circuits. The output closest to the control driver will be much faster than the output at the end of the poly line and will have a slowly decaying tail. But this fast output is usually not on the critical path. The output of interest is normally the slowest one, the one at the end of the poly wire, which has a single-pole response.

# 3.4 Single-Time-Constant Model

The following derivation provides an approximate solution and bounds for each output in a linear RC tree. Voltages have been normalized to range between 0 and 1. Att = 0 the logic inputs change causing the output net to change from a one to a zero. For t < 0, all the nodes in the tree are 1 and at t = 0, the root of the tree is grounded. The derivation for the rising waveform is similar. Nodal voltages  $V_n$  simply are replaced by  $1 - V_n$ .

The voltage at an output node e,  $V_e$ , is equal to the voltage drop through the resistors between e and ground — the root of the tree. This voltage can be found by replacing each capacitor by its equivalent current source,  $i_n = -C_n dV_n/dt$ , and then using superposition. The output voltage is the sum of the contributions from each individual current source. The voltage at node e caused by a current at node k is just the current times the resistance of the path to ground (the driven input) shared by the two nodes. Defining this resistance to be  $R_{ke}$ , the voltage drop caused by current  $i_k$  becomes  $R_{ke}$   $i_k = -R_{ke}C_k \frac{dV_k}{dt}$ . Summing over all capacitor currents in the tree gives the output voltage:

$$V_{\epsilon} = -\sum_{k} R_{k\epsilon} C_k \frac{dV_k}{dt}.$$

(3.1)

# 3.4.1 Waveform Estimate

Equation (3.1) is difficult to solve exactly because it involves a set of coupled differential equations. The capacitors in the tree lead to many time constants. Since most output waveforms are dominated by a single pole, a single-time-constant estimate,  $V_e^*$ , is used to model output voltage at node e. Replacing  $dV_k/dt$  by

<sup>&</sup>lt;sup>†</sup>For example,  $R_{nn}$  is the total resistance from node n to ground. In Figure 3.2,  $R_{23}=R_1$  and  $R_{34}=R_1+R_3$ .

$\alpha_k dV_e/dt$ , where  $\alpha_k$  is an arbitrary constant, converts Eq. (3.1) into a single-time-constant equation. The value of  $\alpha_k$  that gives the best estimate is 1, since this value makes the integral of the error,  $\int (V_e - V_e^*) = \sum_k R_{ke} C_k \int (\frac{dV_k}{dt} - \frac{dV_e}{dt})$ , zero since  $V_k$  and  $V_e$  have the same starting and ending points. The estimated output waveform is a simple decaying exponential with a time constant  $\tau_{De}$ :

$$V_e^*(t) = \exp(-t/\tau_{De}); \qquad \tau_{De} = \sum_{k} R_{ke} C_k.$$

The time constant,  $\tau_{De}$ , is equal to the first moment of the circuit's impulse response, a quantity used to approximate the delay through linear amplifiers [El48]. The output estimates shown in Figures 3.3-3.5 were generated using this model.

In the frequency domain, the single-time-constant estimate is equivalent to modelling the output using a single-pole transfer function. The value of  $\tau_{De}$  matches the frequency response of the output and the estimate at low frequencies: to first-order terms in s.

### 3.4.2 Waveform Bounds

As we saw earlier, most transistor cluster outputs can be approximated by a single-time-constant estimate. Unfortunately, there are also outputs where this estimate is poor. To make the estimate more useful, waveform bounds are derived to provide error control. If the bounds are close to the estimate, then the maximum possible timing error is small: the real output is roughly exponential in shape. If the bounds are very different from the estimate, then a more complex model is required.

To bound the voltage at output e requires a bound on Eq. (3.1). There is no simple way to bound  $dV_k/dt$ , but it is possible to bound  $V_k$  in terms of  $V_e$ . Hence, integrating Eq. (3.1) yelds an equation for the integral of  $V_e$ , which can be bounded. The bounds on the integral of  $V_e$  then can be used to bound  $V_e$ .

Integrating Eq. (3.1) yields

$$\int_0^t V_e(\tau)d\tau = \sum_k R_{ke}C_k(1-V_k(t)).$$

Defining  $g_{\epsilon}(t)$  to be  $\tau_{D\epsilon} - \int V_{\epsilon}^{\dagger}$  simplifies the above equation:

$$g_{\epsilon} = \sum_{k} R_{k\epsilon} C_k V_k. \tag{3.2}$$

Bounding  $V_k$  in terms of  $V_e$  provides a method to bound Eq. (3.2). Since all voltages in an RC tree decrease monotonically with time, the follow bounds on  $V_k$  hold:

$$\frac{R_{ke}}{R_{ee}}V_e \le V_k \le \frac{R_{kk}}{R_{ke}}V_e. \tag{3.3}$$

Substituting the bounds into Eq. (3.2) bounds  $g_e$  in terms of  $V_e$ :

$$\tau_{Re}V_e \le g_e \le \tau_P V_e \tag{3.4}$$

where

$$V_{e} = -\frac{dg_{e}}{dt};$$

$\tau_{P} = \sum_{k} R_{kk} C_{k};$   $\tau_{Re} = \sum_{k} \frac{R_{ke}^{2} C_{k}}{R_{ee}}.$

Bounding  $V_k$  in terms of  $V_e$  causes the bounds on  $g_e$  to become single-time-constant equations. The time constant of the lower bound is  $\tau_{Re}$ ; the time constant of the upper bound is  $\tau_P$ . Both bounds on  $g_e$  are equal to  $\tau_{De}$  at t=0, and decay to zero. Using the  $g_e$  bounds in Eq. (3.4) provides bounds on the output voltage,  $V_e$ :

$$g_{e_{lower}} \leq g_{e} \leq \tau_{P} V_{e}, \qquad \Rightarrow \qquad \frac{\tau_{De}}{\tau_{P}} \exp(-t/\tau_{Re}) \leq V_{e}(t);$$

$$s_{eupper} \geq g_{e} \geq \tau_{Re} V_{e}, \qquad \Rightarrow \qquad \frac{\tau_{De}}{\tau_{Re}} \exp(-t/\tau_{P}) \geq \kappa_{(t)}. \tag{3.5}$$

$<sup>^{\</sup>dagger}$ Since voltages have been normalized,  $\int V$  has the dimensions of time

For a complete derivation see Appendix A.

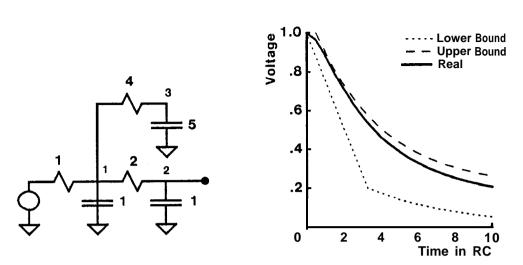

The bounds only depend on three time constants,  $\tau_{De}$ ,  $\tau_{Re}$ , and  $\tau_{P}$ .  $\tau_{Re}$  is a lower bound on the output's time constant;  $\tau_{P}$  is an upper bound. When all three time constants are similar in value, the estimate's maximum error is small. The error increases as the difference in the time constants increase.

The bounds on the output voltage in equation (3.5) can be improved by using the additional constraints that  $V_{\bf e}$  decreases monotonically with time and  $V_{\bf e} \leq 1$ . Using the monotonicity of  $V_{\bf e}$  gives

$$g_{e}(t) + (t - t')V_{e}(t) \leq g_{e}(t').$$

Replacing  $g_e(t)$  and  $g_e(t')$  with bounds,  $\tau_{Re}V_e$  and  $\tau_{De}\exp(-t/\tau_P)$  respectively, leads to the following improved upper bound on the output voltage:

$$V_{e}(t) \leq \begin{cases} 1, & 0 \leq t \leq \tau_{De} - \tau_{Re}; \\ \frac{\tau_{De}}{t + \tau_{Re}}, & \tau_{De} - \tau_{Re} \leq t \leq \tau_{P} - \tau_{Re}; \\ \frac{\tau_{De}}{\tau_{P}} \exp\left(\frac{-t + \tau_{P} - \tau_{Re}}{\tau_{P}}\right), & \tau_{P} - \tau_{Re} \leq t. \end{cases}$$

(3.6)

Since  $g_e$  is  $\tau_{De} - \int V_e$ , using the constraint  $V_e \leq 1$  gives a better lower bound on  $g_e$ , which leads to a better lower bound on  $V_e$ :

$$V_{e}(t) \geq \begin{cases} \frac{(\tau_{De} - t)}{\tau_{P}}, & t \leq \tau_{De} - \tau_{Re}; \\ \frac{\tau_{Re}}{\tau_{P}} \exp\left(\frac{-t + \tau_{De} - \tau_{Re}}{\tau_{Re}}\right), & t \geq \tau_{De} - \tau_{Re}. \end{cases}$$

(3.7)

Although these new bounds are tighter than the previous ones (Eq. (3.5)), the general dependence on the time constants remains the same. The difference between  $\tau_{Re}$  and  $\tau_{P}$  controls the uncertainty in the estimate. The bounds for a circuit with a low-frequency pole-zero pair are widely separated (see Figure 3.6), warning

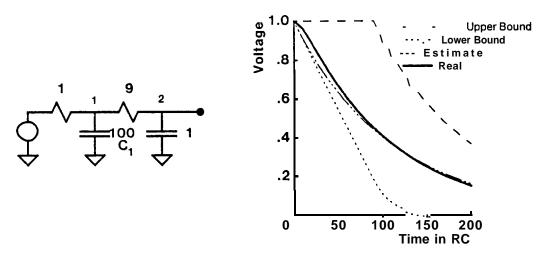

**Figure 3.6** Output bounds for a circuit with a low-frequency pole-zero pair.  $\tau_{De} = 9$ ,  $\tau_{Re} = 5$ ,  $\tau_{P} = 29$

**Figure 3.7** Output bounds for **a** distributed RC line.  $\tau_{De} = .5$ ,  $\tau_{Re} = .33$ ,  $\tau_{P} = .5$

the designer that the estimate is poor. For an output with a single-time-constant behavior, the bounds are close to the estimate, as can be seen in Figure 3.7.

## 3.4.3 Computational Requirements

For the waveform estimate and bounds, three time constants characterize the output:  $\tau_{De}$ ,  $\tau_{Re}$ , and  $\tau_{P}$ . These time constants are needed for each physical output

of a transistor cluster, since the outputs can have different waveforms. Each time constant is a sum over all the capacitors in the network (for distributed elements these sums become integrals), so for a network of n capacitors a time constant takes O(n) time to compute. Repeating this process for all outputs requires  $O(n^2)$  time, assuming the number of outputs is proportional to the number of nodes (capacitors). The time complexity can be reduced to O(n) by using an algorithm that finds the time constants for all the outputs simultaneously. This reduction is possible because the time constants for different outputs share common terms; finding the time constants for the outermost nodes provides the inner time constants with little extra computational effort. An algorithm for finding  $\tau_{De}$  for all nodes in a tree is given in Figure 3.8. The algorithm for  $\tau_{Re}$  is analogous.

## 3.4.4 Time Constant Interpretation

In addition to providing output bounds,  $\tau_{Re}$  and  $\tau_P$  provide useful information about the network, especially for cases where the bounds are poor. For an output dominated by a cluster of n poles all at the same frequency,  $\tau_{Re}$  is equal to  $\tau_{De}/n$ , while  $\tau_P$  remains approximately equal to  $\tau_{De}$ . When low-frequency pole-zero pairs are present,  $\tau_P$  is much larger than  $\tau_{De}$  without affecting  $\tau_{Re}$ . When  $\tau_{Re}$  and  $\tau_P$  are both close to  $\tau_{De}$ , the output is dominated by a single pole.

A small  $\tau_{Re}$  does not imply coincident poles. A single pole dominates the output of the RC tree shown in Figure 3.9, yet  $\tau_{Re}$  is much less than  $\tau_{De}$ . This type of circuit often occurs in modelling a bus. The bus capacitance  $(C_1)$  dominates the circuit, but is located between the driving gate  $(R_1)$  and the pass transistor reading the bus  $(R_2)$ . The particular voltage bounds used to generate  $\tau_{Re}$  (Eq. (3.3)) substantially underestimate the actual voltages present for this circuit. As will be shown in the next section, improving the internal voltage bounds leads to better single-time-constant bounds on the output waveform.

```

↑ c[k] ↓

```

```

procedure findC_T (k:node);

(* C_T[k] is the total cap. of the subtree with node k as its root. *)

begin

C_T[\mathbf{k}] := \mathbb{C}[\mathbf{k}];

for all children i do begin

\operatorname{find} C_T(\mathbf{i});

C_T[k] := C_T[k] + C_T[i];

end;

end;

procedure find \tau_D(k:node);

begin

for all children i do begin

\tau_D[i] := \tau_D[k] + R[i] C_T[i];

\operatorname{find} \tau_D(i);

end;

end;

begin

\tau_D[\text{root}] := \mathbf{0};

\operatorname{find} C_T(\operatorname{root});

\operatorname{find} \tau_D(\operatorname{root});

end;

```

**Figure 3.8** Algorithm to find  $\tau_{De}$  in linear time.

The bounds are poor for outputs where  $\tau_P >> \tau_{De}$  because a single pole does not dominate the output waveform. An exponential is a crude model of an output with a slowly decaying tail. The upper bound over-estimates the output during the initial fast decay, since the output is modelled by a waveform that decays at the slow tail rate. The lower bound is also poor since it ignores the fast transient completely. It becomes a lower bound on the slow tail, which is a valid, but not useful, lower

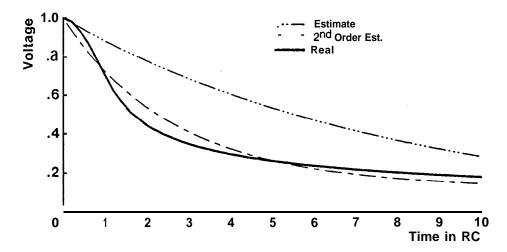

Figure 3.9 Circuit with a poor  $\tau_{Re}$ .  $\tau_{De} = 110$ ,  $\tau_{Re} = 20$ ,  $\tau_{P} = 110$ .

bound on the actual output. To improve this output estimate a two-time-constant model is needed.

# 3.4.5 Improved $\tau_{Re}$

For an RC tree with a poor  $\tau_{Re}$ , a capacitor (or group of capacitors) in the middle of the network sets the circuit's dominant pole. All voltages further from the source, including the output node e, track this capacitor's voltage. Yet the lower bound on the dominant capacitor's voltage is  $\frac{R_{ke}}{R_{ee}}V_e$  instead of  $V_e$  — A. Approximating a node's voltage by this lower bound causes the output bound to be poor if  $R_{ke}$  for the dominant capacitor is much less than  $R_{ee}$ . For the circuit shown in Figure 3.9, the capacitor at node 1 dominates the circuit; the output tracks this voltage. Yet, the lower bound on node 1 is  $V_2/10$ , a poor approximation to the actual voltage.

An improved bound on the output requires a better lower bound for  $V_k$ . The lower bound on  $V_k$  in Eq. (3.3) is the lowest voltage possible given  $V_e$  and positive capacitor currents; the bound does not use any information about the time behavior of the network. For an RC line, using this information leads to **an** improved voltage

Figure 3.10 Improved output bounds using  $\hat{\tau}_{Re}$ .  $\tau_{De} = 110$ ,  $\hat{\tau}_{Re} = 101$ ,  $\tau_{P} = 110$ .

bound, which in turn improves  $\tau_{Re}$ . The improved time constant,  $\hat{\tau}_{Re}$ , is

$$\hat{\tau}_{Re} = \sum_{k} \alpha_{ke} R_{ke} C_{k}; \qquad \alpha_{ke} = \max \left( \frac{R_{ke}}{\bar{R}_{ee}}, 1 - \frac{\tau_{De} - \tau_{Dk}}{\tau_{Rk}} \right).$$

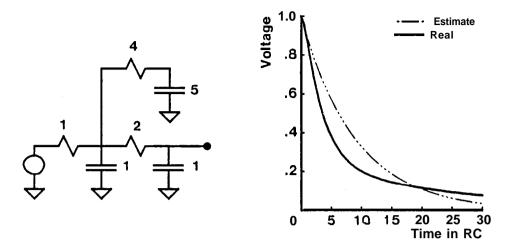

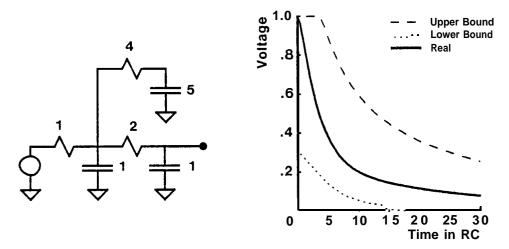

Figure 3.10 shows the improved bounds for the RC line given in Figure 3.9. The new  $\tau_{Re}$  greatly improves the bounds when the dominant capacitor lies on the path from the output to driving gate. Outputs where  $\hat{\tau}_{Re}$  is still much smaller than  $\tau_{De}$  have coincident poles and can be better approximated by a two-time-constant estimate.

### 3.5 Two-Time-Constant Model

For outputs with multiple time constants, the problem with the single-timeconstant model is the assumption that all voltages in the network are proportional to the output voltage. These networks have a low frequency pole caused by capacitors

<sup>&</sup>lt;sup>†</sup>The improved bounds are derived using the constraint  $-\frac{dV_n}{dt}/V_n \ge -\frac{dV_q}{dt}/V_q$  when node q is downstream of n. For a more complete derivation of the improved bounds see Appendix **A.**

off the path from the root to the output. As a result, the voltage on some nodes in the circuit are not tightly coupled to the output voltage. To improve the estimate and bounds for these outputs, the loosely coupled nodes are handled separately from the other nodes. The resulting timing model has two time constants. Outputs in this class are characterized by  $\tau_P \gg \tau_{De}$ .

### 3.5.1 Waveform Estimate

The improved estimate has two time constants — one to model the decay of the initial transient and the other to model the slow decay of the output tail. The improved estimate is the best two-pole, single-zero model of the output waveform. This is the simplest system that can have a slow tail in its output response.

The second order estimate has three parameters: the time constants of the two poles and the one zero. These time constants can be related to three characteristic time constants of the output: the sum of the open circuit time constants,  $\tau_P$ ; the first moment of the impulse response,  $\tau_{De}$ ; and the second moment of the impulse response,  $2\tau_P(\tau_{De}-\tau_{Me})$ . Setting the model's characteristic time constants equal to the characteristic time constants of the output yields the best estimate of the output waveform. This choice of time constants matches the frequency response of the output with the frequency response of the estimate at low frequencies. Unlike the single-time-constant estimate, this model matches the output to second-order terms in s.

The model network transfer function can be written as

$$H_m(s) = \frac{1 + s\tau_z}{(1 + s\tau_1)(1 + s\tau_2)}.$$

(3.8)

The characteristic time constants for this system are

The  $n^{th}$  order moment of the impulse response is equal to -1" times the  $n^{th}$  derivative of the transfer function evaluated at s=0.

$$\tau_{P} = \tau_{1} + \tau_{2}, \qquad \tau_{De} = \tau_{P} - \tau_{z}, \qquad \tau_{Me} = \frac{\tau_{1}\tau_{2}}{\tau_{1} + \tau_{2}}$$

(3.9)

The first two time constants for the output are already known:

$$au_P = \sum_{k} R_{kk} C_k, \qquad au_{De} = \sum_{k} R_{ke} C_k.$$

$\tau_{Me}$  can be found by generating the second order moment of the impulse response, which is twice the first moment of the output voltage. Integrating by parts gives

$$\int tV_e dt = \sum_k R_{ke} C_k \int t dV_k = \sum_k R_{ke} C_k \tau_{Dk} = \tau_P (\tau_{De} - \tau_{Me})$$

or

$$\tau_{Me} = \sum_{k} R_{ke} C_k \left( 1 - \frac{\tau_{Dk}}{\tau_P} \right).$$

Inverting the relations in Eq. (3.9) gives  $\tau_1$  and  $\tau_2$  in terms of the physical time constants:

$$au_z = au_P - au_{De};$$

$au_2, au_1 = rac{ au_P}{2} (1 \pm \sqrt{1 - 4 au_{Me}/ au_P}).$

The inverse Laplace transform of Eq. (3.8) gives the estimated output voltage:

$$V_{e}^{*} = \frac{(\tau_{z} - \tau_{1})e^{-t/\tau_{1}} + (\tau_{2} - \tau_{z})e^{-t/\tau_{2}}}{\tau_{2} - \tau_{1}}.$$

(3.10)

This equation provides an improved estimate for all outputs, even those where  $\tau_P = \tau_{De}$ . The improved estimate is only slightly more complex than the single-time-constant estimate, and requires two additional time constants, though  $\tau_P$  is needed for the bounds already.

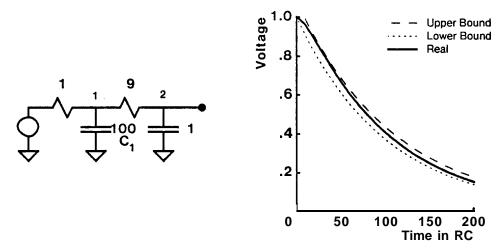

Figure 3.11 shows the single-time-constant estimate, the second-order estimate, and the actual output for the networks shown in Figures 3.4 and 3.5. The improved estimate accurately reflects the actual output. The advantage of the two-time-constant estimate is its ability to model the different decay rates of the output. The estimate has the largest error when an output has many time constants, not just

**Figure 3.11** Two-time-constant Estimate for (a) the circuit with three coincident poles shown in Figure 3.4 —  $\tau_{De} = 3$ ,  $\tau_{P} = 3$ ,  $\tau_{Me} = 1$ ; and for (b) the circuit with a low-frequency pole-zero pair shown in Figure 3.5 —  $\tau_{De} = 9$ ,  $\tau_{P} = 29$ ,  $\tau_{Me} = 3.2$ .

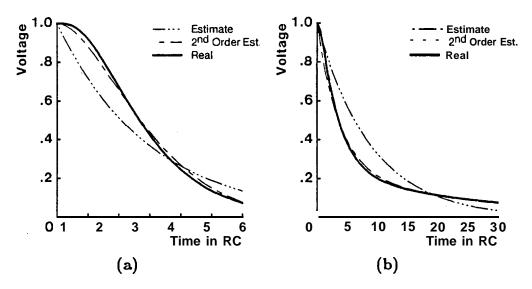

**Figure 3.12** Output from the begining of a long RC line.

two. This situation occurs when the output is at the beginning of a long distributed RC line. The output and estimate in this case are shown in Figure 3.12.

## 3.5.2 Physical Interpretation

When  $\tau_P \gg \tau_{De}$ , the output estimate (Eq. (3.10)) can be viewed as the sum of the slow nodes' contribution and the fast nodes' contribution. Expanding Eq. (3.10) and only keeping terms of first order in  $\frac{\tau_{Dk}}{\tau_P}$  will clarify this point.

To first order,  $\tau_1 = \tau_{Me}$  and  $\tau_2 = \tau_P - \tau_{Me}$ , since  $\tau_{Me}$  is less than  $\tau_{De}$ . For an output with a low-frequency pole-zero pair,  $\tau_{Me}$  represents the time constant of the initial fast transient;  $\tau_P - \tau_{Me}$  represents the time constant in the tail region.  $\tau_{Me}$  is roughly equal to  $\sum R_{ke}C_k$ , where the sum is over all nodes where  $\tau_{Dk} << \tau_P$ ; it is the time constant of the output if the slow nodes in the circuit are removed. Thus  $\tau_1$  represents the time constant of the fast nodes, and  $\tau_2$  represents the time constant of the slow nodes.

The amplitude of the  $\tau_2$  term  $(\frac{\tau_2 - \tau_z}{\tau_2 - \tau_1})$  to first order is  $\frac{\tau_{De} - \tau_{Me}}{\tau_2}$ , which is equal to  $\sum_{slow} R_{ke} C_k / \tau_2$ . The effect of the slow nodes is modelled by assuming they all decay exponentially with a time constant  $\tau_2$ . To first order in  $\frac{\tau_{De}}{\tau_P}$ , the estimate is simply the sum of the contributions of the fast and slow nodes:

$$V_{e}^{*}(t) \approx \left(1 - \frac{\tau_{De_2}}{\tau_2}\right) e^{-t/\tau_1} + \frac{\tau_{De_2}}{\tau_2} e^{-t/\tau_2},$$

where

$$\tau_1 = \sum_{\text{fast}} R_{ke} C_k; \qquad \tau_2 = \sum_{\text{slow}} R_{kk} C_k; \qquad \tau_{De_2} = \sum_{\text{slow}} R_{ke} C_k.$$

<sup>†</sup>If the voltage at the slow nodes is a simple exponential with a time constant  $\tau_2$ , then their contribution to the output is  $\sum_{slow} R_{ke} C_k \frac{dV_k}{dt} = \exp(-t/\tau_2) \sum_{slow} \frac{R_{ke} C_k}{\tau_P}$ .

# 3.5.3 Bounds Improvement when $\tau_P \gg \tau_{De}$

When  $\tau_P$  is much larger than  $\tau_{De}$ , some capacitors decay slowly compared to the output. The relationship between the output and the voltage at these slow nodes changes as the output decays. Initially all the voltages start at the same voltage. When the output voltage is small, the slow nodes' voltage can still be quite large, since they decay more slowly than the output. Using a single constant to bound the voltage at these slow nodes in terms of the output voltage will be a poor approximation of the actual node voltage, at least for some range of output. The improved estimate overcomes this problem by grouping the slow nodes together and letting them decay at their own rate. The output is then written as the sum of two terms, one modelling the slow nodes, and the other modelling the rest of the tree. The same idea of decoupling the slow nodes from the output is used to improve the bounds.

To improve the lower bound on the output,  $\tau_P$  is improved by using a better upper bound on the internal nodal voltages:

$$V_k \leq \min\left(1, \frac{R_{kk}}{R_{ke}} V_e\right).$$

This upper bound sets the voltage at the slow nodes to be 1 when the output voltage is large, thus decoupling the slow nodes during the initial transient. The improved bound on the output voltage becomes

$$V_{e} \ge \frac{g_{e_{lower}} - \tau_{De}^{\alpha}}{\tau_{P}^{\alpha}},\tag{3.11}$$

where

$$\tau_{De}^{\alpha} = \sum_{k} \alpha_{k} R_{ke} C_{k}; \qquad \tau_{P}^{\alpha} = \sum_{k} (1 - \alpha_{k}) R_{kk} C_{k}; \qquad \alpha_{k} = \begin{cases} 1, & 2R_{ke} \leq R_{kk}; \\ 0, & 2R_{ke} > R_{kk}. \end{cases}$$

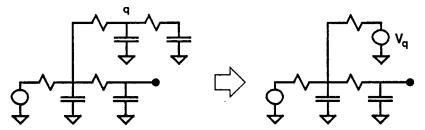

The upper bound on the output is more difficult to improve. Here the slow nodes are decoupled from the output by replacing them by a voltage source. The value of the source is chosen to give an upper bound on the actual output. Superposition is then used to write the bound as the sum of two terms, one caused by the slow nodes and the other from the network minus the slow nodes. Assuming the voltage source is placed at node  $v_1$ , the improved upper bound is

$$V_{e} \leq \frac{R_{ve}}{R_{vv}} + \frac{\tau_{De}^{*}}{\tau_{Re}^{*}} e^{-t/\tau_{P}^{*}}, \tag{3.12}$$

where the starred time constants represent time constants for the modified network, with the slow nodes shorted out by the added voltage source. Appendix C describes these bounds in more detail.

## 3.5.4 Computational Requirements

In both the improved bounds and estimate, a small number of time constants characterize the output waveform. Each time constant is a sum over all the **nodes** in the tree. For a network with n nodes, each time constant takes O(n) time to compute. However, unlike the original bounds, the terms being summed are not shared by different outputs. The bounds are improved by tailoring the time constants to a particular output. This difference means it takes  $O(n^2)$  time to find improved bounds for all nodes in an RC tree, rather than the O(n) time required for the original bounds. If only a constant number of outputs need improved bounds, then the time complexity remains O(n).

The improved estimate only depends on three time constants,  $\tau_{De}$ ,  $\tau_{P}$ , and  $\tau_{Me}$ . Figure 3.8 has already illustrated how to find the first two time constants for all nodes in a tree in linear time.  $\tau_{Me}$  also can be found for all nodes in linear time. Thus, both an estimate and an improved estimate can be found for all outputs in O(n) time.

Thus determining  $\tau_{Me}$  can be reduced to finding  $\sum C_k^* R_{ke}$  for every node, a task equivalent to finding  $\tau_{De}$  for all nodes in a tree.

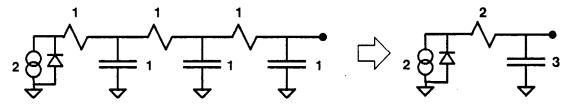

## 3.6 Connecting Two RC Trees

The delay models derived in the preceding sections have always assumed that a voltage source in series with a resistor drives the output network to its new value. This approximation breaks down when the capacitance within a gate is not negligible, or when a pass transistor turns on, connecting a new output net to an already settled output. For these situations, the output net is driven by an RC tree. This section derives timing models for these two-tree circuits. Like previous models, an initial single-time-constant estimate and bounds are derived, and then methods to improve these waveforms are discussed. Networks where the bounds poorly approximate the actual output closely resemble the  $\tau_P >> \tau_{De}$  problem in a single RC tree, and the same techniques can be used to improve the timing model.