# OPTIMIZED MULTIPROCESSOR COMMUNICATION AND SYNCHRONIZATION USING A PROGRAMMABLE PROTOCOL ENGINE

John Heinlein

**Technical Report No.: CSL-TR-98-759**

**March 1998**

This dissertation was supported by an Air Force Laboratory Graduate Fellowship (administered by the Air Force Office of Scientific Research), by an Intel Foundation Fellowship, and by the Defense Advanced Research Projects Agency, which funded the FLASH project under DARPA Contract DABT63-94-C-0054.

### Optimized Multiprocessor Communication and Synchronization Using a Programmable Protocol Engine

#### John Heinlein

CSL-TR-98-759

#### **March 1998**

COMPUTER SYSTEMS LABORATORY

Departments of Electrical Engineering and Computer Science

Gates Computer Science Building, #408

Stanford University

Stanford, CA 94305-9040

pubs@shasta.stanford.edu

#### Abstract

In recent years, multiprocessor designs have converged towards a unified hardware architecture despite supporting different communication abstractions. The implementation of these communication abstractions and the associated protocols in hardware is complex, inflexible, and error prone. For these reasons, some recent designs have employed a programmable controller to manage system communication. One particular focus of these designs is implementing cache coherence protocols in software. This dissertation argues that a programmable communication controller that provides cache coherence can also effectively support block transfer and synchronization protocols. This research is part of the FLASH project, a major focus of which is exploring the integration of multiple communication protocols in a single multiprocessor architecture.

In our analysis, we examine the needs of protocols other than cache coherence to identify the requirements they share. The interface between the processor and controller is one critical issue in these protocols, so we propose techniques to export such protocols reliably, at low overhead, and without system calls. Unlike most prior studies, our approach supports a modern operating system with features like multiprogramming, protection, and virtual memory.

Our study focuses in detail on two classes of communication that are important for large scale multiprocessors: block transfer and synchronization using locks and barriers. In particular, we attempt to improve the performance of these classes of communication as compared to implementations using only software on top of shared memory. For each protocol we identify the critical metrics of performance, explore the limitations of existing techniques, then present our implementation, which is tailored to leverage the programmable communication controller. We evaluate each protocol in isolation, in the context of microbenchmarks, and within a variety of applications.

We find that embedding advanced communication and synchronization features in a programmable controller has a number of advantages. For example, the block transfer protocol improves transfer performance in some cases, enables the processor to perform other work in parallel, and reduces processor cache pollution caused by the transfer. The synchronization protocols reduce overhead and eliminate bottlenecks associated with synchronization primitives implemented using software on top of shared memory. Simulations of scientific applications running on FLASH show that, in many cases, synchronization support improves performance and increases the range of machine sizes over which the applications scale. Our study shows that embedded programmability is a convenient approach for supporting block transfer and synchronization, and that the FLASH system design effectively supports this approach.

**Keywords & Phrases:** multiprocessors, FLASH, cache-coherent shared memory, message passing, synchronization

Copyright © 1998 by John Heinlein All Rights Reserved

## Acknowledgements

I have had the privilege to carry out my graduate studies among some of the most talented researchers in the computer architecture field. I especially thank my advisor, Anoop Gupta, whose guidance has helped me grow as both a researcher and a person. His advice and feedback on this dissertation itself has significantly improved its quality. I am also grateful to John Hennessy, my secondary advisor. Despite the pressures of being computer science department chair and then engineering dean, John was always available to give me his invaluable guidance and support. I thank Bruce Wooley for chairing my orals committee and serving on my reading committee, which were very generous given his equally taxing responsibilities as acting electrical engineering department chair.

Besides those faculty on my reading committee, I would like to acknowledge the contributions of two others as well. First, Mark Horowitz, who served as the day-to-day leader of the FLASH project. Mark's seemingly limitless knowledge and experience, as well as his skill at managing the project made a difficult task achievable and fun. I also benefitted greatly from the advice, friendship, and collaboration of Mendel Rosenblum, who brought a valued alternative perspective to the project.

I feel particularly lucky to have received the guidance of DASH veteran Kourosh Gharachorloo, who worked closely with me at Stanford throughout the work on block transfer and later during my internship at Digital Equipment Corporation's Western Research Laboratory (WRL). His attention to detail has enriched my graduate training. His insight is reflected in particular in the techniques presented in Chapter 4.

I was also fortunate enough to have a wonderful group of fellow researchers with whom I was able to work. First and foremost, the FLASH team was responsible for developing the novel architecture studied in this research: Joel Baxter, Jules Bergmann, Mark Heinrich, Hema Kapadia, Jeffrey Kuskin, David Ofelt, David Nakahira, and Richard Simoni. I also acknowledge two other colleagues, Steven Woo and Chris Holt, who graciously helped me unravel the SPLASH applications I studied. I am also grateful for having been able to work closely with a "second family"

as well, Mendel Rosenblum's Hive and SimOS groups: Robert Bosch, Edouard Bugnion, John Chapin, Scott Devine, Kinshuk Govil, Steve Herrod, Beth Seamans, Dan Teodosiu, Ben Verghese, Ben Werther, and Emmett Witchel. John Chapin collaborated on the operating system and interface issues for the protocols we study. Robert Bosch contributed to the performance evaluation of memory copy.

Of all these, I would like to specially acknowledge my two sets of officemates: from the CSL Trailer, David Ofelt and Jeffrey Kuskin; and from Gates 354, Robert Bosch and Steve Herrod. I learned a great deal from them especially, and I sincerely valued their friendship and support over these many years. Special thanks also go to Joel Baxter and Mark Heinrich whose endless simulator work and unfailing assistance were invaluable in supporting this research.

I thank Charlie Orgish and Thoi Nguyen for helping me sleep at night knowing my data was safe, but even more importantly for being wonderful friends. Throughout my studies and my work as CSL student bureaucrat, I benefited from the care and help of a number of administrators: Lori Balough, Darlene Hadding, Margaret Rowland, Naomi Schulman, Eileen Schwappach, Terry West, and many others. From out of the blue I was blessed with the advice and kindness of Nick McKeown and Murray Warren, who helped me along my journey in many ways.

I gratefully acknowledge support for my graduate studies from an Air Force Laboratory Graduate Fellowship (administered by the Air Force Office of Scientific Research), from an Intel Foundation Fellowship, and from the Defense Advanced Research Projects Agency, which funded the FLASH project under DARPA Contract DABT63-94-C-0054. The completion of my dissertation took place at Transmeta Corporation. I cannot adequately express my gratitude for the support and understanding I received from my supervisors Craig Anderson and Jack Guskin, especially as the process dragged on beyond all expectation.

I thank Michelle Stohlmeyer for her loving and patient support during the often difficult process of finishing my dissertation. Her empathy (not to mention her excellent care packages) kept me going in the final stages.

Finally, I am deeply grateful for the unfailing love and support of my parents, John and Janet, and my brother Jason. The nurturing environment they provided is undoubtedly responsible for my accomplishments in life, and my love for them cannot be overstated.

To my parents John and Janet who gave me every opportunity in the world.

# **Contents**

| Al | ostrac | t       |                                                  | i  |

|----|--------|---------|--------------------------------------------------|----|

| A  | cknow  | ledgem  | ents                                             | v  |

| 1  | Intr   | oductio | o <b>n</b>                                       | 1  |

|    | 1.1    | Using   | a Programmable Protocol Engine                   | 2  |

|    |        | 1.1.1   | Why Embed Programmability?                       | 2  |

|    |        | 1.1.2   | The FLASH Approach                               | 3  |

|    | 1.2    | Dissert | tation Focus                                     | 4  |

|    |        | 1.2.1   | Processor/Controller Interface Issues            | 4  |

|    |        | 1.2.2   | Requirements of Alternate Protocols              | 4  |

|    |        | 1.2.3   | Detailed Protocol Studies                        | 4  |

|    | 1.3    | Contrib | butions                                          | 5  |

|    | 1.4    | Organi  | zation                                           | 6  |

| 2  | The    | FLASH   | Multiprocessor                                   | 9  |

|    | 2.1    | Backgr  | round and Motivation                             | 9  |

|    |        | 2.1.1   | The DASH Multiprocessor                          | 11 |

|    |        | 2.1.2   | The FLASH Approach                               | 12 |

|    | 2.2    | FLASH   | Overview                                         | 12 |

|    |        | 2.2.1   | FLASH System Architecture                        | 13 |

|    |        | 2.2.2   | Communication Protocol Terminology and Semantics | 14 |

|    |        | 2.2.3   | Cache Coherence                                  | 15 |

|    | 2.3    | MAGIC   | C (Memory and General Interconnect Controller)   | 17 |

|    |        | 2.3.1   | MAGIC Microarchitecture Overview                 | 17 |

|    |        | 2.3.2   | The Protocol Processor                           | 19 |

|   |      | 2.3.3   | The Processor Interface                          | 20              |

|---|------|---------|--------------------------------------------------|-----------------|

|   |      | 2.3.4   | Data Buffers and Memory Access                   | 22              |

|   |      | 2.3.5   | The Software Queue and Idle Handler              | 24              |

|   |      | 2.3.6   | Deadlock                                         | 26              |

|   | 2.4  | FLASH   | Software Environment                             | 27              |

|   |      | 2.4.1   | Protocol Compilation and Scheduling              | 27              |

|   |      | 2.4.2   | FLASH System Simulation                          | 28              |

|   | 2.5  | Summa   | ary                                              | 29              |

| 3 | Uses | of Flex | cibility Beyond Cache Coherence                  | 31              |

|   | 3.1  | Block   | Transfer (Message Passing) in FLASH              | 32              |

|   |      | 3.1.1   | Message Passing Overview                         | 33              |

|   |      | 3.1.2   | Message Passing Models                           | 34              |

|   |      | 3.1.3   | Providing Block Transfer                         | 35              |

|   |      | 3.1.4   | Integrated Shared Memory and Message Passing     | 36              |

|   | 3.2  | Synchr  | ronization Primitives                            | 37              |

|   |      | 3.2.1   | Locks                                            | 38              |

|   |      | 3.2.2   | Barriers                                         | 39              |

|   | 3.3  | Summa   | ary                                              | 39              |

| 4 | Alte | rnate P | rotocol Fundamentals                             | 41              |

|   | 4.1  | Proces  | sor/MAGIC Communication                          | 42              |

|   |      | 4.1.1   | The Protocol Processor Call (PPC)                | 43              |

|   |      | 4.1.2   | The Protocol Processor Register (PPR)            | 47              |

|   |      | 4.1.3   | The Operating System Procedure Call (OSPC)       | 48              |

|   | 4.2  | Virtual | Memory                                           | 50              |

|   |      | 4.2.1   | Providing Authentic Translations from User Level | 51              |

|   |      | 4.2.2   | Guaranteeing Translations Remain Valid           | 55              |

|   |      | 4.2.3   | Comparing the Virtual Memory Techniques          | 59              |

|   | 4.3  | Protect | tion                                             | 60              |

|   | 4.4  | Cohere  | ence of Alternate Protocols (PP Ownership)       | 61              |

|   |      | 4.4.1   | MAGIC IO Subsystem                               | 62              |

|   |      | 4.4.2   | PP Ownership                                     | 63              |

|   |      |         |                                                  |                 |

|   | 4.5  | Summa   | ary                                              | 65              |

| 5 |      |         | nory Copy                                        | 65<br><b>67</b> |

| 5 |      | SH Men  |                                                  |                 |

|   | 5.2 | Locally | y Coherent Transfer Model                       | 70  |

|---|-----|---------|-------------------------------------------------|-----|

|   |     | 5.2.1   | Transfer Overview                               | 70  |

|   |     | 5.2.2   | Base Implementation                             | 73  |

|   |     | 5.2.3   | Optimized Implementation                        | 79  |

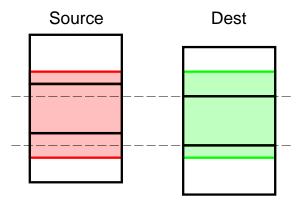

|   |     | 5.2.4   | Unaligned Transfers                             | 83  |

|   | 5.3 | Fully ( | Coherent Transfer Model                         | 85  |

|   |     | 5.3.1   | Cache Coherence for Block Transfer Data         | 85  |

|   |     | 5.3.2   | Support for Remote Homes                        | 88  |

|   |     | 5.3.3   | Implementation Issues                           | 89  |

|   | 5.4 | Low-le  | evel Performance Analysis                       | 90  |

|   |     | 5.4.1   | Simulation Environment                          | 90  |

|   |     | 5.4.2   | Transfer Overhead                               | 91  |

|   |     | 5.4.3   | Transfer Bottlenecks                            | 93  |

|   | 5.5 | Bench   | marks and Performance Comparison                | 95  |

|   |     | 5.5.1   | Microbenchmark Analysis                         | 96  |

|   |     | 5.5.2   | Message Passing Interface (MPI)                 | 98  |

|   |     | 5.5.3   | GNU tar Application                             | 99  |

|   | 5.6 | Related | d Work                                          | 100 |

|   |     | 5.6.1   | Discussion                                      | 103 |

|   | 5.7 | Summ    | ary                                             | 104 |

|   |     | ~       |                                                 |     |

| • |     | •       | chronization Primitives                         | 107 |

|   | 6.1 |         | Locks                                           |     |

|   |     | 6.1.1   | Metrics for Evaluating Lock Performance         |     |

|   |     | 6.1.2   | Conventional Lock Implementations               |     |

|   |     | 6.1.3   | FLASH Lock Application Programming Interface    |     |

|   |     |         | FLASH Lock Implementation                       |     |

|   |     | 6.1.5   | Protocol Discussion                             | 123 |

|   |     | 6.1.6   | Multiprogramming/Multithreading Issues          | 125 |

|   |     | 6.1.7   | Protocol Handlers                               | 128 |

|   |     | 6.1.8   | Lock Performance in Isolation                   | 130 |

|   |     | 6.1.9   | Related Work                                    | 137 |

|   | 6.2 |         | Barriers                                        | 143 |

|   |     | 6.2.1   | Metrics for Evaluating Barrier Performance      | 143 |

|   |     | 6.2.2   | Conventional Barrier Implementations            | 146 |

|   |     | 6.2.3   | FLASH Barrier Application Programming Interface | 150 |

|   |     |         |                                                 |     |

|     |        | 6.2.5 Protocol Handlers                             | 55             |

|-----|--------|-----------------------------------------------------|----------------|

|     |        | 6.2.6 Barrier Performance in Isolation              | 55             |

|     |        | 6.2.7 Related Work                                  | 51             |

|     | 6.3    | Lock and Barrier Performance Impact in Applications | 53             |

|     |        | 6.3.1 Application Descriptions and Characteristics  | 54             |

|     |        | 6.3.2 Water                                         | 56             |

|     |        | 6.3.3 Barnes                                        | 15             |

|     |        | 6.3.4 Ocean                                         | 30             |

|     | 6.4    | Discussion                                          | 1              |

|     | 6.5    | Summary                                             | )3             |

| 7   | Exte   | sions and Future Directions 19                      | )5             |

|     | 7.1    | Active Messages                                     | )5             |

|     |        | 7.1.1 Processor-Implemented Active Messages         | <del>)</del> 6 |

|     |        | 7.1.2 MAGIC-Implemented Active Messages             | <b>)</b> 7     |

|     | 7.2    | Other Protocols                                     | 9              |

|     |        | 7.2.1 Fetch-and-Op                                  | 9              |

|     |        | 7.2.2 Global Reduction Operations                   | 0              |

|     |        | 7.2.3 Fault Containment, Reliability, and Recovery  | )1             |

|     |        | 7.2.4 Performance Monitoring                        | )1             |

|     | 7.3    | Summary                                             | )2             |

| 8   | Con    | dusions 20                                          | )5             |

|     | 8.1    | Interface Between Processor and Controller          | )5             |

|     | 8.2    | Memory Copy                                         | )6             |

|     | 8.3    | Synchronization                                     | )7             |

|     | 8.4    | Flexible Controller Design Observations             | )9             |

| A   | MAG    | IC Implementation Details 21                        | 1              |

|     | A.1    | PP Instruction Set                                  | 1              |

|     | A.2    | Processor Interface                                 | 1              |

|     |        | A.2.1 PI Reply Register                             | 1              |

|     |        | A.2.2 Supported PI Operations                       | .3             |

| В   | Syn    | hronization Primitive Implementations 21            | 5              |

|     | B.1    | Locks                                               | .5             |

|     | B.2    | Barriers                                            | .7             |

| Bil | bliogr | phy 22                                              | 21             |

# **List of Tables**

| 5.1         | Breakdown of fbcopy overhead components                                    | 92  |

|-------------|----------------------------------------------------------------------------|-----|

| 5.2         | Transfer latency to send 4 KB using bcopy, prefetched bcopy, and fbcopy    | 96  |

| 5.3         | Simulation results for GNU tar using different memory copy implementations | 100 |

| 6.1         | Summary of the FLASH lock protocol handlers                                | 129 |

| 6.2         | Acquire latency for an available lock                                      | 131 |

| 6.3         | Two results from the contended locking microbenchmark                      | 133 |

| 6.4         | Summary of the FLASH barrier protocol handlers                             | 156 |

| 6.5         | Barrier fall-through latency ( $t_{\rm ft}$ ) for late arrival             | 157 |

| 6.6         | Barrier fall-through latency ( $t_{\rm ft}$ ) for simultaneous arrival     | 157 |

| 6.7         | Barrier release latency $(t_{\rm rel})$                                    | 159 |

| 6.8         | Master-Slave Barrier microbenchmark results                                | 161 |

| 6.9         | Application problem size and synchronization usage overview                | 165 |

| 6.10        | Water lock results summary.                                                | 169 |

| 6.11        | Barnes lock results summary                                                | 177 |

| 6.12        | Ocean barrier results summary                                              | 183 |

| 8.1         | Protocol code size summary                                                 | 208 |

| <b>A.</b> 1 | Summary of the MAGIC Protocol Processor instruction set                    | 212 |

| A 2         | Explanation of Processor Interface interventions (partial list)            | 213 |

# **List of Figures**

| 2.1  | Symmetric multiprocessor architecture                                                 | 10 |

|------|---------------------------------------------------------------------------------------|----|

| 2.2  | Scalable multiprocessor architecture                                                  | 11 |

| 2.3  | FLASH Node Architecture                                                               | 13 |

| 2.4  | MAGIC Microarchitecture.                                                              | 13 |

| 2.5  | Conceptual illustration of a cache coherence directory                                | 16 |

| 2.6  | Changing data alignment via double-buffer loads                                       | 24 |

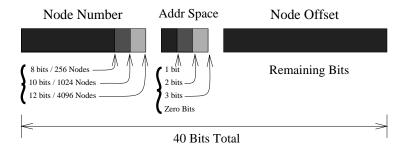

| 4.1  | FLASH Address format                                                                  | 45 |

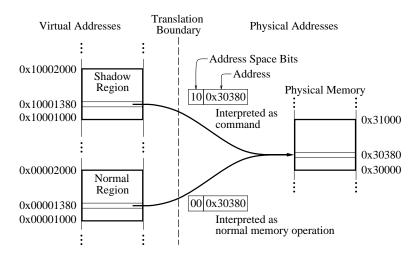

| 4.2  | Example of double mapping illustrating the use of alternate physical address spaces.  | 52 |

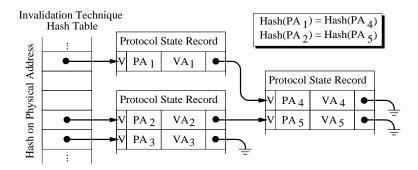

| 4.3  | Example translation invalidation data structure                                       | 58 |

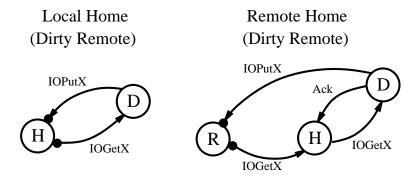

| 4.4  | The PP ownership table                                                                | 63 |

| 4.5  | PP Ownership building on top of the I/O support in the protocol                       | 64 |

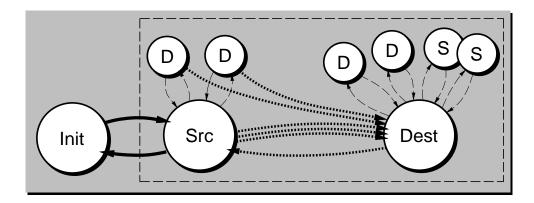

| 5.1  | Sources of complexity in memory copy                                                  | 69 |

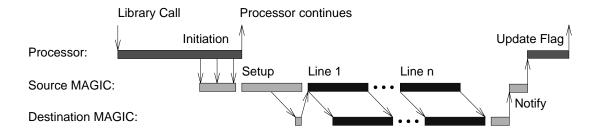

| 5.2  | Schematic transfer timeline                                                           | 71 |

| 5.3  | Pseudo code for the base implementation of the locally coherent transfer handler      | 75 |

| 5.4  | Coherence handling in the locally coherent transfer model                             | 76 |

| 5.5  | Page boundary crossings                                                               | 79 |

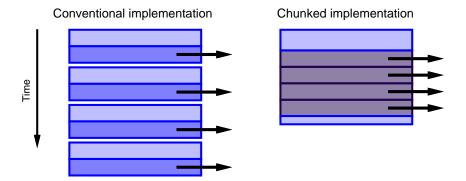

| 5.6  | Potential benefit from chunking                                                       | 80 |

| 5.7  | Pseudo code for the optimized implementation of the locally coherent transfer handler | 81 |

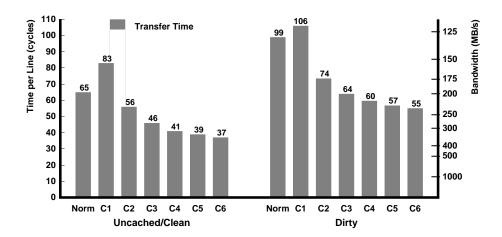

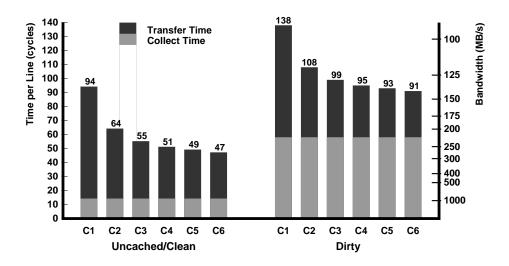

| 5.8  | Transfer handler performance for different chunking and caching parameters            | 82 |

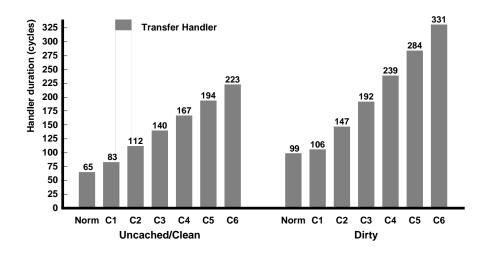

| 5.9  | Total transfer handler duration for different chunking and caching parameters         | 83 |

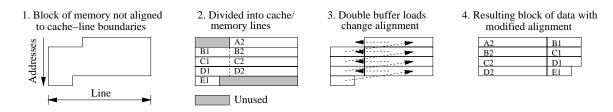

| 5.10 | Support for arbitrary block transfer alignment                                        | 84 |

| 5.11 | Unaligned transfer performance as a function of chunk size and caching state          | 85 |

| 5.12 | Example coherence scenario                                                            | 86 |

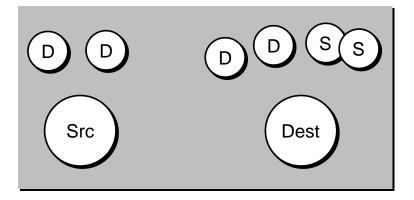

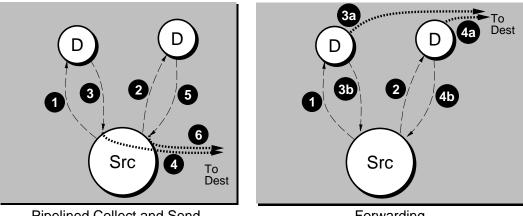

| 5 13 | Source side coherence alternatives                                                    | 87 |

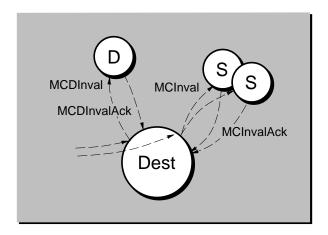

| 5.14 | Destination side coherence                                                           | 88  |

|------|--------------------------------------------------------------------------------------|-----|

| 5.15 | Complete fbcopy protocol including remote home support                               | 89  |

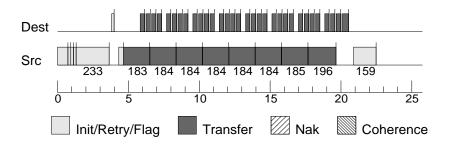

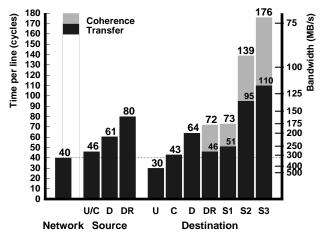

| 5.16 | Time line of a two-node block transfer                                               | 93  |

| 5.17 | Time line of a block transfer with the source buffer dirty on a remote node          | 94  |

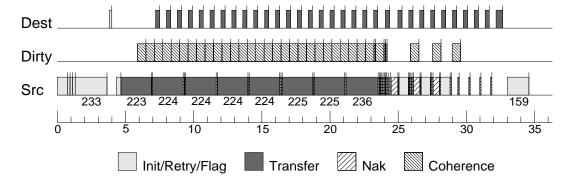

| 5.18 | Comparison of forwarding (Fwd) vs. pipelined collect-and-send (PC&S)                 | 95  |

| 5.19 | Bottlenecks in fbcopy from the network and protocol processing                       | 95  |

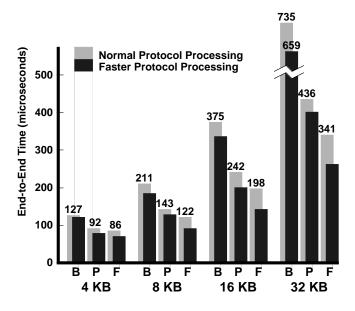

| 5.20 | MPI transfer performance for a range of message sizes and transfer techniques        | 99  |

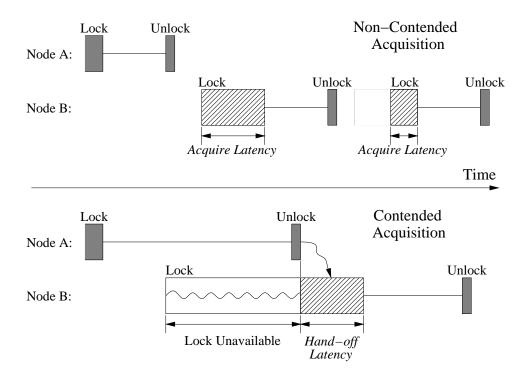

| 6.1  | Non-contended and contended lock acquisition metrics                                 | 111 |

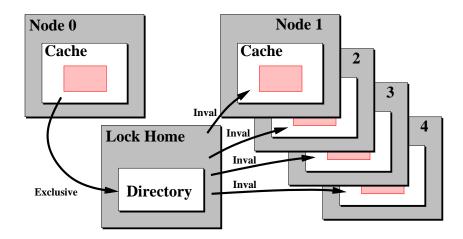

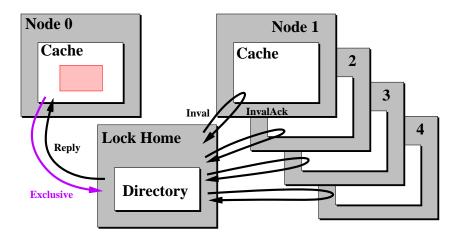

| 6.2  | Invalidation of lock waiters when the holder upgrades to release the lock            | 113 |

| 6.3  | Former sharers acknowledge the invalidation                                          | 113 |

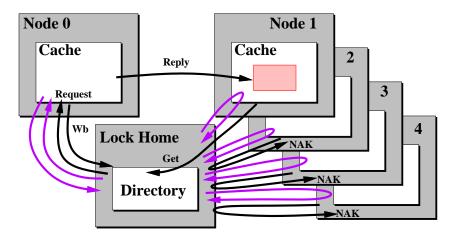

| 6.4  | A rush of requesters follows an unlock                                               | 113 |

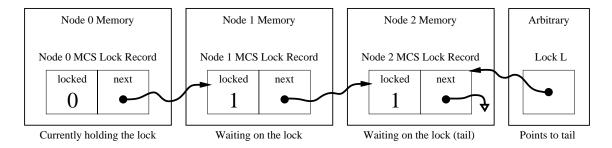

| 6.5  | MCS Lock queueing approach                                                           | 114 |

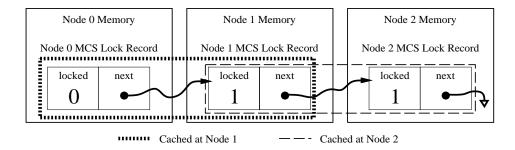

| 6.6  | Extraneous caching in MCS lock queues                                                | 115 |

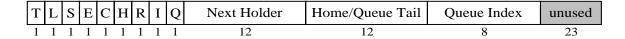

| 6.7  | Lock protocol internal state format                                                  | 118 |

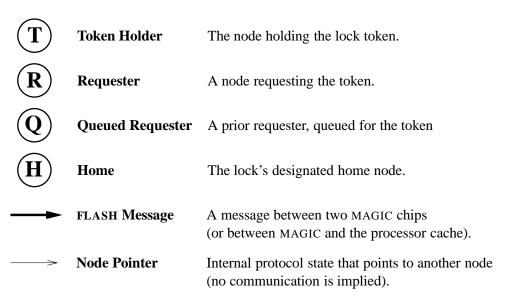

| 6.8  | Legend of symbols in lock protocol diagrams                                          | 120 |

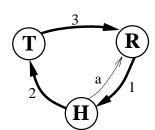

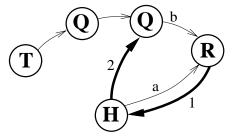

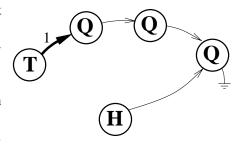

| 6.9  | Request for local lock state from MAGIC                                              | 121 |

| 6.10 | Token request for lock currently at another node, no queue pending (Unlocked)        | 121 |

| 6.11 | Token request for a lock currently at another node, no queue pending (Locked)        | 121 |

| 6.12 | Request for a lock with a queue of waiters pending                                   | 121 |

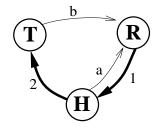

| 6.13 | Unlock operation in cache when no queue is pending                                   | 122 |

| 6.14 | Unlock operation with one or more requesters pending                                 | 122 |

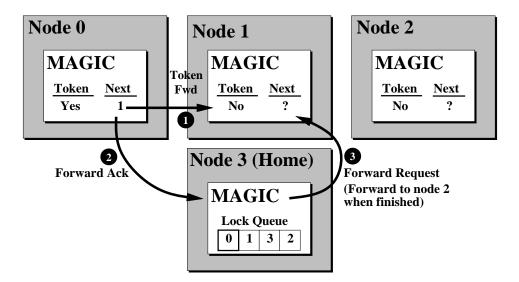

| 6.15 | The centralized queue locking approach for FLASH locks                               | 124 |

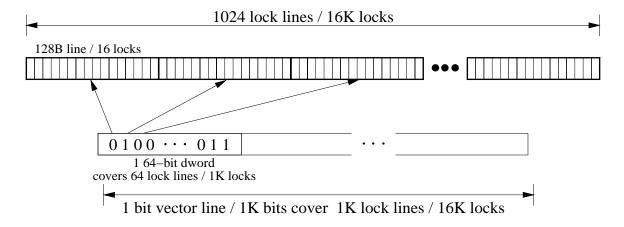

| 6.16 | Timeout bit vector structure and lock correspondence                                 | 126 |

| 6.17 | Pseudo code for the FLASH lock timeout mechanism                                     | 127 |

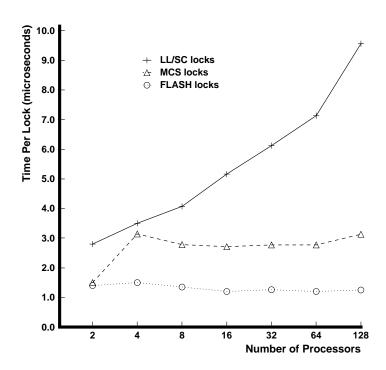

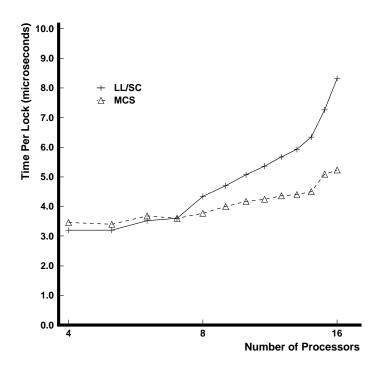

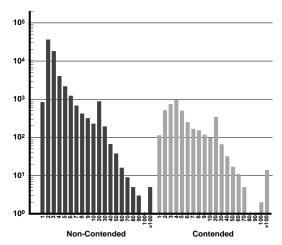

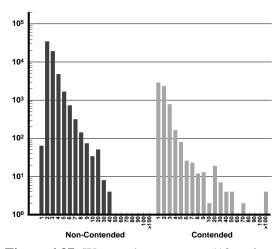

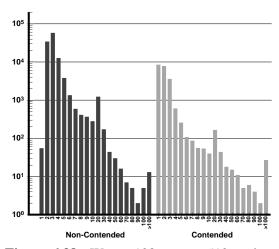

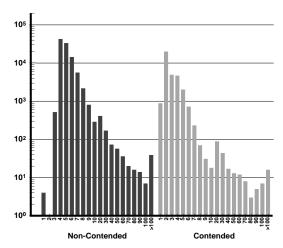

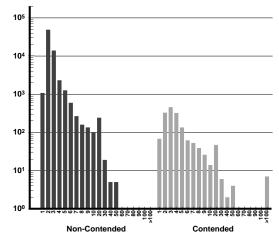

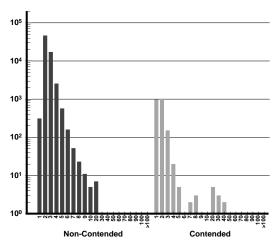

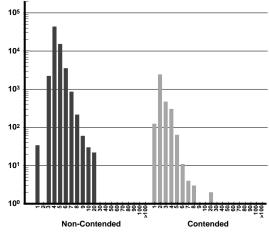

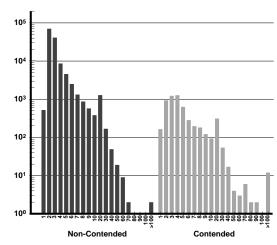

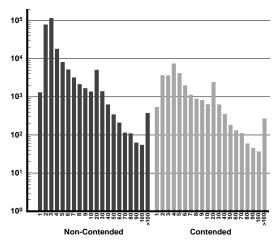

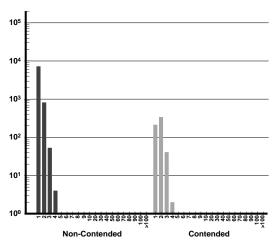

| 6.18 | Results from the high contention benchmark under simulation                          | 134 |

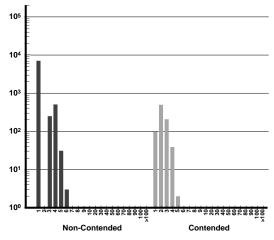

| 6.19 | Results from the high contention benchmark on the Silicon Graphics Origin 2000. $$ . | 135 |

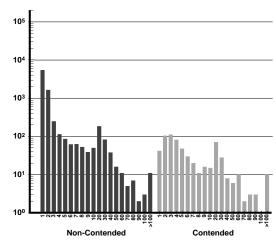

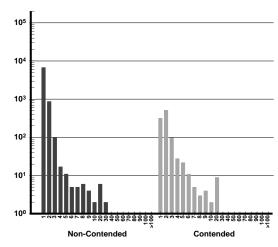

| 6.20 | Performance of the stochastic contended lock microbenchmark under simulation         | 137 |

| 6.21 | Pseudo code for a lock implemented with the QOLB primitive                           | 140 |

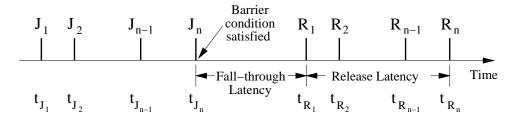

| 6.22 | Barrier nomenclature illustration, showing fall-through latency and release latency. | 145 |

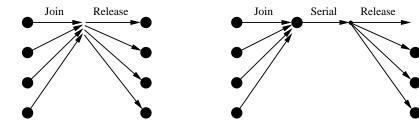

| 6.23 | Schematic illustration of barrier primitive types: conventional and master-slave     | 147 |

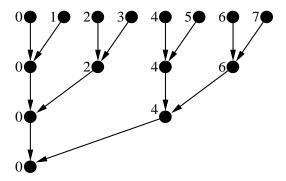

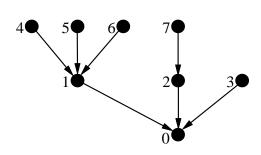

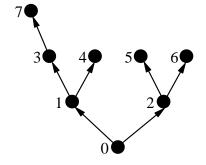

| 6.24 | Example binary tournament barrier tree for an 8-processor application                | 148 |

| 6.25 | Example 3-ary barrier join tree for an 8-processor application                       | 149 |

| 6.26 | Example binary (2-ary) barrier release tree for an 8-processor application           | 149 |

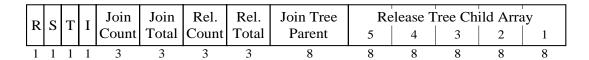

| 6.27 | Barrier protocol internal state format                                               | 152 |

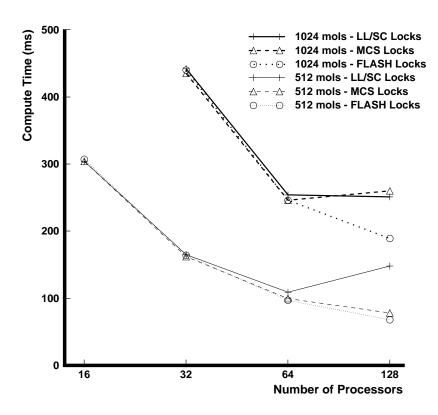

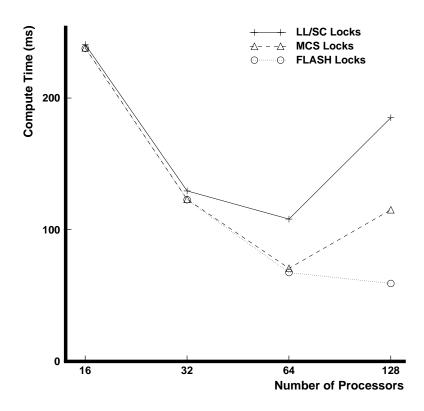

| 6.28 | Water computation time using different lock techniques                               | 167 |

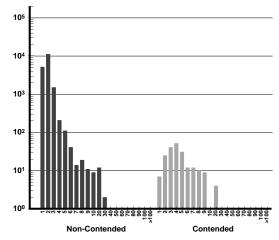

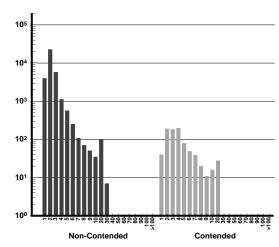

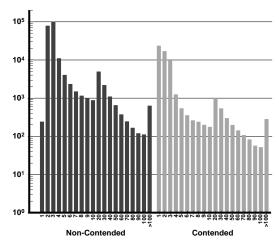

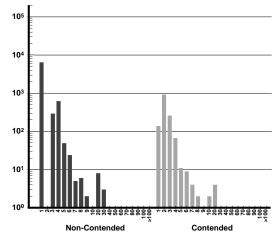

| 6.29 | Water, 16 processors, 512 molecules, LL/SC lock latency histograms                   | 170 |

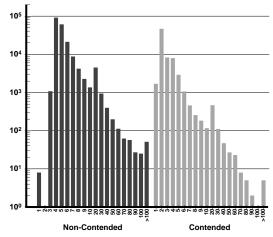

| 6.30 | Water, 32 processors, 512 molecules, LL/SC lock latency histograms              | 170 |

|------|---------------------------------------------------------------------------------|-----|

| 6.31 | Water, 16 processors, 512 molecules, MCS lock latency histograms                | 170 |

| 6.32 | Water, 32 processors, 512 molecules, MCS lock latency histograms                | 170 |

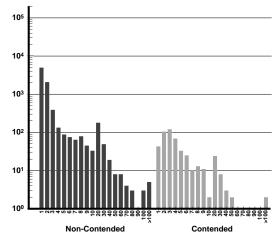

| 6.33 | Water, 16 processors, 512 molecules, FLASH lock latency histograms              | 170 |

| 6.34 | Water, 32 processors, 512 molecules, FLASH lock latency histograms              | 170 |

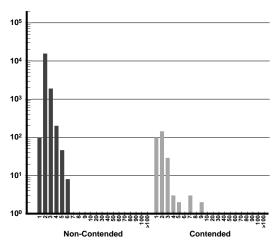

| 6.35 | Water, 64 processors, 512 molecules, LL/SC lock latency histograms              | 171 |

| 6.36 | Water, 128 processors, 512 molecules, LL/SC lock latency histograms             | 171 |

| 6.37 | Water, 64 processors, 512 molecules, MCS lock latency histograms                | 171 |

| 6.38 | Water, 128 processors, 512 molecules, MCS lock latency histograms               | 171 |

| 6.39 | Water, 64 processors, 512 molecules, FLASH lock latency histograms              | 171 |

| 6.40 | Water, 128 processors, 512 molecules, FLASH lock latency histograms             | 171 |

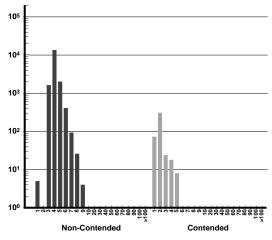

| 6.41 | Water, 32 processors, 1024 molecules, LL/SC lock latency histograms             | 172 |

| 6.42 | Water, 64 processors, 1024 molecules, LL/SC lock latency histograms             | 172 |

| 6.43 | Water, 32 processors, 1024 molecules, MCS lock latency histograms               | 172 |

| 6.44 | Water, 64 processors, 1024 molecules, MCS lock latency histograms               | 172 |

| 6.45 | Water, 32 processors, 1024 molecules, FLASH lock latency histograms             | 172 |

| 6.46 | Water, 64 processors, 1024 molecules, FLASH lock latency histograms             | 172 |

| 6.47 | Water, 128 processors, 1024 molecules, LL/SC lock latency histograms            | 173 |

| 6.48 | Water, 128 processors, 1024 molecules, MCS lock latency histograms              | 173 |

| 6.49 | Water, 128 processors, 1024 molecules, FLASH lock latency histograms            | 173 |

| 6.50 | Barnes computation time using different lock techniques                         | 176 |

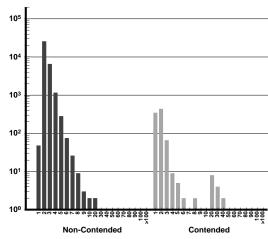

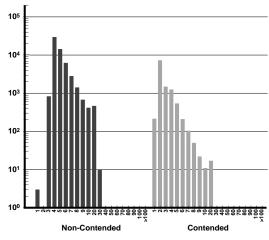

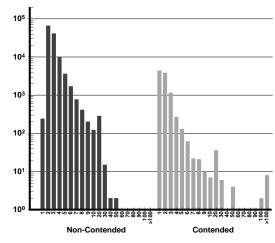

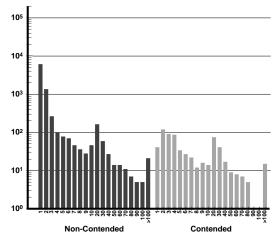

| 6.51 | Barnes, 16 processors, 8k bodies, LL/SC lock latency histograms                 | 178 |

| 6.52 | Barnes, 32 processors, 8k bodies, LL/SC lock latency histograms                 | 178 |

| 6.53 | Barnes, 16 processors, 8k bodies, MCS lock latency histograms                   | 178 |

| 6.54 | Barnes, 32 processors, 8k bodies, MCS lock latency histograms                   | 178 |

| 6.55 | Barnes, 16 processors, 8k bodies, FLASH lock latency histograms                 | 178 |

| 6.56 | Barnes, 32 processors, 8k bodies, FLASH lock latency histograms                 | 178 |

| 6.57 | Barnes, 64 processors, 8k bodies, LL/SC lock latency histograms                 | 179 |

| 6.58 | Barnes, 128 processors, 8k bodies, LL/SC lock latency histograms                | 179 |

| 6.59 | Barnes, 64 processors, 8k bodies, MCS lock latency histograms                   | 179 |

| 6.60 | Barnes, 128 processors, 8k bodies, MCS lock latency histograms                  | 179 |

| 6.61 | Barnes, 64 processors, 8k bodies, FLASH lock latency histograms                 | 179 |

| 6.62 | Barnes, 128 processors, 8k bodies, FLASH lock latency histograms                | 179 |

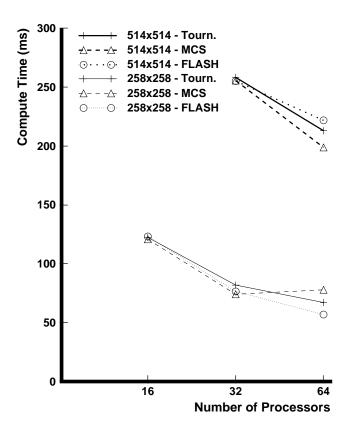

| 6.63 | Ocean computation time using different barrier techniques                       | 182 |

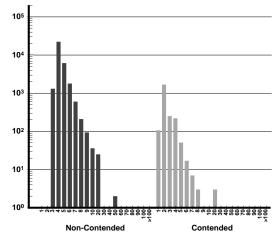

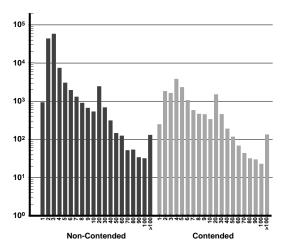

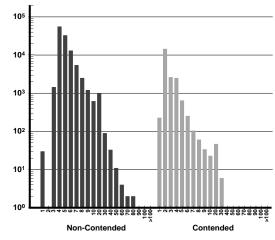

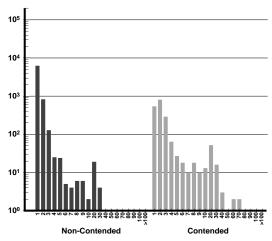

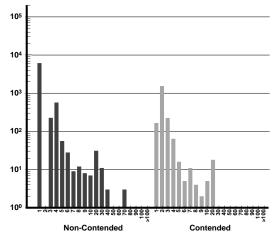

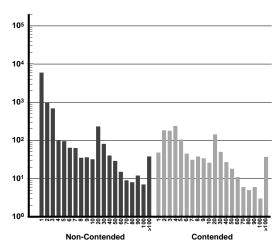

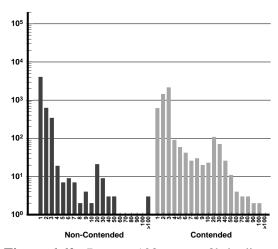

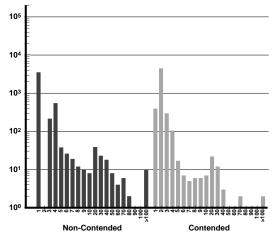

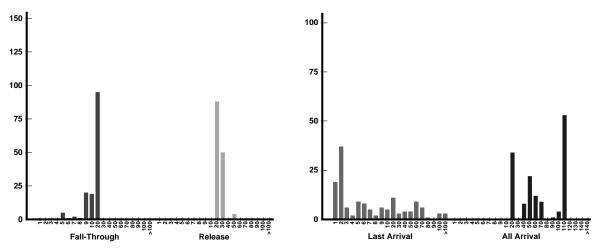

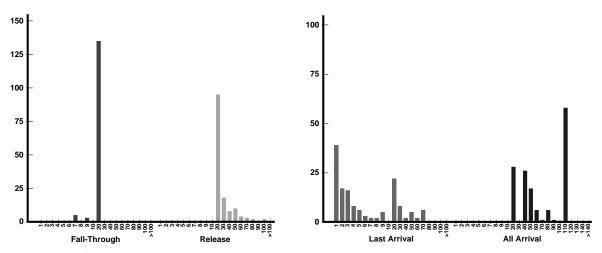

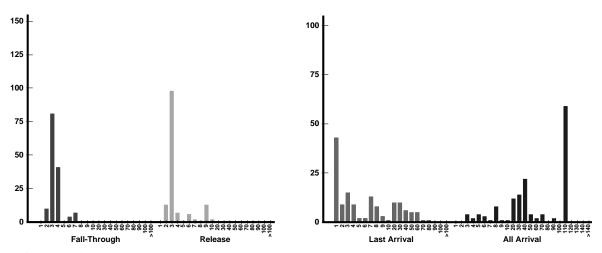

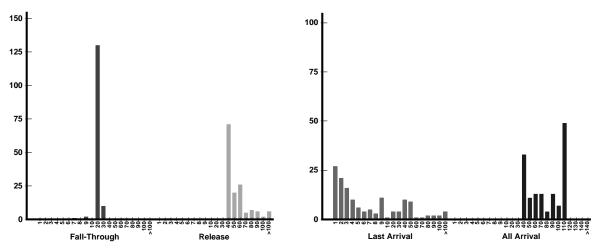

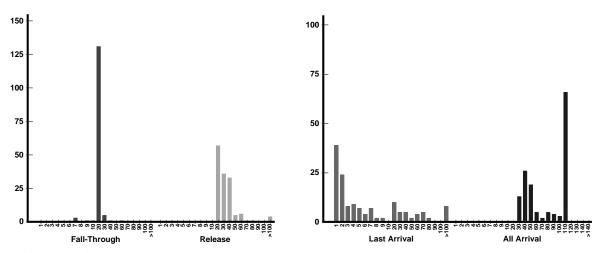

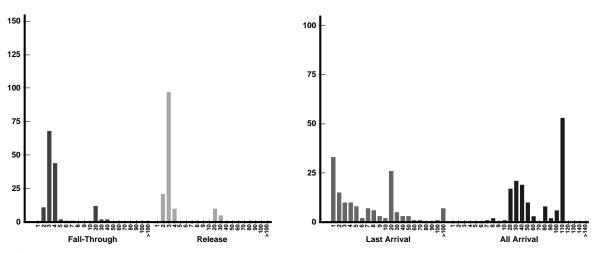

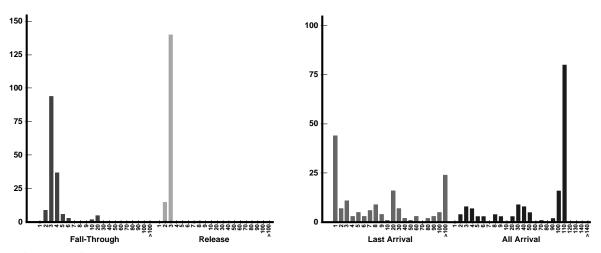

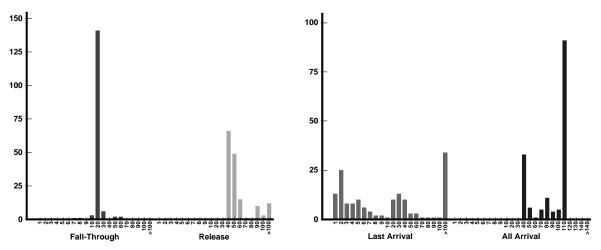

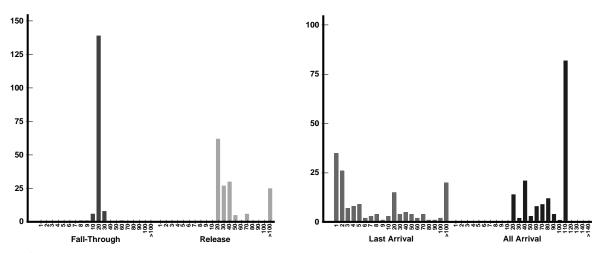

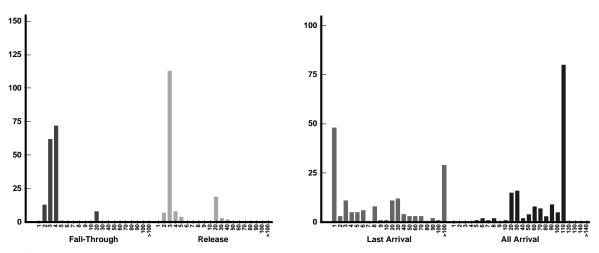

| 6.64 | Ocean, 16 processors, 258x258, Tournament barrier metric and arrival histograms | 184 |

| 6.65 | Ocean, 16 processors, 258x258, MCS barrier metric and arrival histograms        | 184 |

| 6.66 | Ocean, 16 processors, 258x258, FLASH barrier metric and arrival histograms      | 184 |

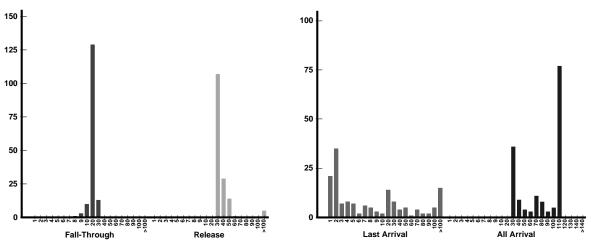

| 6.67 | Ocean, 32 processors, 258x258, Tournament barrier metric and arrival histograms. | 185 |

|------|----------------------------------------------------------------------------------|-----|

| 6.68 | Ocean, 32 processors, 258x258, MCS barrier metric and arrival histograms         | 185 |

| 6.69 | Ocean, 32 processors, 258x258, FLASH barrier metric and arrival histograms       | 185 |

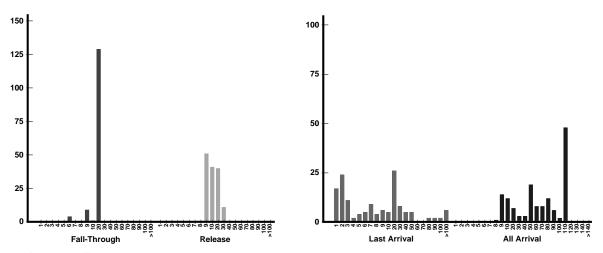

| 6.70 | Ocean, 64 processors, 258x258, Tournament barrier metric and arrival histograms  | 186 |

| 6.71 | Ocean, 64 processors, 258x258, MCS barrier metric and arrival histograms         | 186 |

| 6.72 | Ocean, 64 processors, 258x258, FLASH barrier metric and arrival histograms       | 186 |

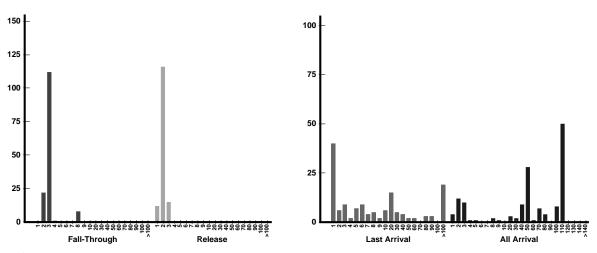

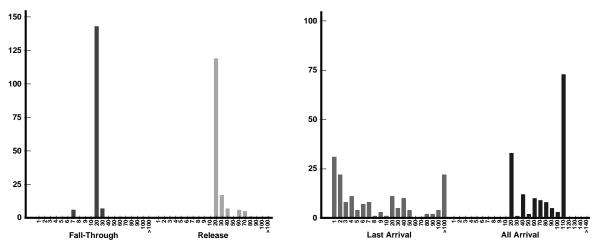

| 6.73 | Ocean, 32 processors, 514x514, Tournament barrier metric and arrival histograms  | 187 |

| 6.74 | Ocean, 32 processors, 514x514, MCS barrier metric and arrival histograms         | 187 |

| 6.75 | Ocean, 32 processors, 514x514, FLASH barrier metric and arrival histograms       | 187 |

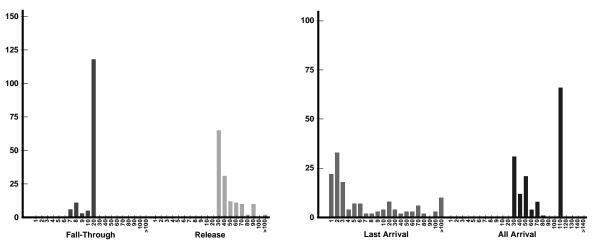

| 6.76 | Ocean, 64 processors, 514x514, Tournament barrier metric and arrival histograms  | 188 |

| 6.77 | Ocean, 64 processors, 514x514, MCS barrier metric and arrival histograms         | 188 |

| 6.78 | Ocean, 64 processors, 514x514, FLASH barrier metric and arrival histograms       | 188 |

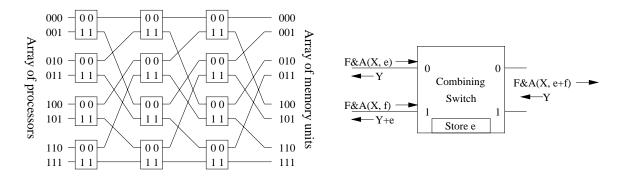

| 7.1  | The NYU Ultracomputer's Combining network                                        | 200 |

| B.1  | Pseudo code for a load-linked/store-conditional-based lock implementation        | 216 |

| B.2  | Pseudo code for the Mellor-Crummey Scott lock                                    | 216 |

| B.3  | Pseudo code for the LL/SC-based barrier implementation                           | 217 |

| B.4  | Pseudo code for the tournament tree barrier implementation                       | 218 |

| B.5  | Pseudo code for the Mellor-Crummey Scott barrier                                 | 219 |

| B.6  | Pseudo code for the Basic Master-Slave barrier implementation                    | 220 |

### **Chapter 1**

### Introduction

A critical problem in multiprocessors is managing communication between the processors in the system. Individual processor performance is important, but it alone is not sufficient to achieve scalable system performance. To address the communication problem, multiprocessor systems research has explored a broad range of design styles and, in turn, communication abstractions presented to the application. Among these models are shared memory, message passing, dataflow, systolic arrays, SIMD, and many others, each of which has advantages for certain classes of programs [Fly66, Vee86, AAG<sup>+</sup>87, AS88, Bla90, Int91, Len92, HT93].

Over time, two models have emerged as the predominant ones supported by multiprocessor systems: cache-coherent shared memory and message passing. Shared memory provides the programmer with a simple memory abstraction similar to a uniprocessor that is particularly well suited for programs that exhibit dynamic communication behavior or fine grain sharing. Certain other types of communication such as the transfer of coarse grain data can sometimes be achieved more efficiently through message passing, though it significantly increases the data management burden on the application programmer.

The complementary nature of the shared memory and message passing communication styles, in conjunction with the convergence of underlying hardware mechanisms used to implement each model has led to a surge of interest in hybrid architectures that support both styles efficiently. Furthermore, the complexity of implementing the protocols in hardware has motivated the development of hybrid hardware/software solutions to manage communication [ACD<sup>+</sup>91, Cra93, ACD<sup>+</sup>95].

As one recent approach, several systems have been designed using a programmable controller to manage system communication [ACD<sup>+</sup>91, ACD<sup>+</sup>95, KOH<sup>+</sup>94]. One particular focus of these systems is implementing cache coherence protocols in software. This study argues that a programmable

communication controller that provides cache coherence can also effectively support block transfer and synchronization protocols. Our focus is on one such system in particular, the FLASH Multiprocessor, which includes a programmable protocol engine to serve as the memory system and network interface controller. FLASH (*FL*exible Architecture for *SH*ared memory), was designed by a team of researchers at Stanford University between 1992–1997. This dissertation complements previous studies of FLASH, which focus on its architecture and its use with a range of cache coherence protocols [KOH<sup>+</sup>94, HKO<sup>+</sup>94, MOH96, Kus97, Hei].

Since the introduction of FLASH, other commercial and research systems have been proposed that incorporate some of the same design characteristics, including the use of a flexible protocol engine. Among these systems are Typhoon [RLW94, RPW96] and the Sequent NUMA-Q [LC96]. As in FLASH, the published research for these systems has also focused primarily on shared memory, though many of the issues we address also apply to those systems. Thus, our study of "alternate" protocols may be applicable in a wider context than just the FLASH project.

#### 1.1 Using a Programmable Protocol Engine

Traditionally, within the core of a multiprocessor system is a hardware unit designed to implement the communication model provided by the machine. For example, in the case of cache-coherent shared memory, the communication controller transparently manipulates data to support the illusion of shared memory. For message passing, it accepts explicit requests for data transfer and moves data asynchronously.

Instead of the traditional hardware-only approach, the system we study uses a communication controller containing a programmable engine at its core. As we describe below, this approach provides a number of benefits over the traditional design. We briefly explore the characteristics of these systems in general, then introduce the particular design of the FLASH system.

#### 1.1.1 Why Embed Programmability?

Embedding programmability to replace a pure hardware solution is not a new idea. The use of microcode to manage the internal control signals of a processor was proposed in 1949 [HP90]. The approach we study, however, uses embedded programmability in a new context: within the communication controller in a multiprocessor system. Flexibility in this context seems a natural extension of computer system design trends occurring in recent years. Several examples of these trends are as follows:

The Alewife system designed at MIT allows software control over communication protocols by supporting fast processor interrupts. Alewife's approach thus *shares* a single processor to perform both computation and protocol processing tasks [ACD<sup>+</sup>91, ACD<sup>+</sup>95].

Multiprocessor bus controllers continue to grow in complexity and functionality, especially those for high-end servers. Current designs include support for features such as high performance I/O management, RAS (Reliability, Availability, and Serviceability), and seamless multiprocessing expandability. These features have reached a level of complexity where an implementation based partially or entirely on software may soon be a reasonable design trade-off.

The Stanford DASH and the Sun S3.mp systems both integrate a controller with some degree of programmability within their coherence protocol units. DASH uses a hybrid approach in which most functions are provided in hardware but key protocol decisions are stored in a table. This allows only limited customizations, such as enabling some protocol errors to be fixed [Len92]. S3.mp provides a slightly more powerful model closer to a traditional microcode approach [NAB<sup>+</sup>95].

Flexibility embedded in the system enables a broad range of advantages over a purely hardware approach. First and foremost it allows one architecture to support a range of different communication models. Hardware approaches could support multiple models, but they must be selected and fixed in advance. On the other hand, a system with embedded programmability allows the communication protocols to be changed even after the system has been designed and built.

Late customization is valuable for a variety of reasons, among them: (i) to fix bugs in the protocol, (ii) to enable low-level performance optimizations, and (iii) to allow communication extensions for particular applications or even entirely new protocols. In addition, protocol development in software is convenient since one can use traditional software development and debugging techniques. The challenge in a system with embedded flexibility is achieving high performance, since an implementation incorporating software may be less efficient than one based purely on hardware.

#### 1.1.2 The FLASH Approach

FLASH was designed from the beginning to balance the goal of integrating flexibility with the desire for high performance. It is based on a programmable communication controller, MAGIC (Memory And General Interconnect Controller), placed centrally in the node and given high-performance access to memory, network, I/O, and the main processor. One of the key innovations in MAGIC is its support for the parallel handling of control processing and data movement. Its centerpiece is a programmable Protocol Processor that performs the control processing in software. Alongside the Protocol Processor, MAGIC contains optimized hardware units to swiftly move data between its communication interfaces. This hybrid design is enables protocols with a wide range of characteristics to achieve high performance.

#### 1.2 Dissertation Focus

The focus of this dissertation is to study the advantages and design issues of using a programmable controller to support protocols other than cache coherence. We argue that through careful design of the controller and protocols the same hardware designed for cache coherence can support other classes of communication as well. We support our thesis by analyzing alternate protocols from several different fronts, which we introduce below:

#### 1.2.1 Processor/Controller Interface Issues

While the introduction of a programmable controller opens up a range of possibilities of communication functionality and performance, it also brings with it many new problems. For communication support in the memory system to be useful, the processor must be able to access it at low overhead. To accomplish this goal, we describe techniques that export these protocols at user level, i.e., without system calls. Avoiding system call overhead increases the range of protocols that show benefits from implementation on the communication controller.

However, unlike past studies that have considered systems running in single-user mode or in a restricted system environment, our goal is to provide support for a modern operating system. To bridge this gap, our research proposes techniques to support operating system features like multi-programming, protection, and virtual memory.

#### 1.2.2 Requirements of Alternate Protocols

One goal of embedding programmability in the communication controller is to support a range of protocols effectively. Nonetheless, the design of these systems tends to focus more strongly on the requirements of one protocol in particular, in this case cache coherence. One focus of this study is to understand in a similar way the controller features which are particularly valuable for alternate protocols.

This analysis studies the FLASH system and its node controller, MAGIC, focusing on the features that are particularly important for alternate protocols. We analyze a range of specific alternate protocols that one might support with a programmable controller, identifying their requirements and their amenability to implementation on FLASH. In cases where the FLASH system design limits the full generality of these protocols we discuss the tradeoffs associated with extending the controller and propose alternatives that can address the limitations without controller extensions.

#### 1.2.3 Detailed Protocol Studies

Finally, our study focuses in detail on two particular classes of communication which are important for large scale multiprocessors. We find that each of these classes encounters disadvantages when implemented on top of shared memory, in part because their communication does not exactly match that provided by the cache coherence protocol.

First we present the mechanisms used to support efficient block transfer in FLASH. The protocol we implement and study provides *memory copy* functionality, which can be used to support message passing as well as accelerate block transfer communication in shared memory programs. Our protocol delegates the data transfer functionality to MAGIC which implements it with protocol software. In addition to describing the transfer implementation itself, we also explain how the protocol integrates block transfer with cache coherence, which is critical to enable its use within shared memory applications.

In our experiments we compare the performance of the FLASH memory copy primitive with processor-based implementations, including those using prefetching. Our results suggest that implementing block transfer support in MAGIC improves transfer performance in many cases, enables the processor to perform other work in parallel, and reduces processor cache pollution caused by the transfer.

We also study the design of two synchronization primitives, *locks* and *barriers*. These primitives are typically implemented on top of shared memory and as a result often perform poorly due to artifactual communication associated with cache coherence. Our design targets these artifacts; by eliminating them we improve synchronization performance and characteristics.

Synchronization protocols highlight the benefits of the careful implementation of embedded programmability in MAGIC. These protocols are very lightweight, with very different characteristics than the block transfer protocol. Nonetheless, the flexibility of FLASH enables high performance for these protocols as well. Our results show that synchronization support from the programmable controller improves performance of some applications from the SPLASH-2 benchmark suite [WOT+95], especially at larger machine sizes.

#### 1.3 Contributions

The primary contributions of this dissertation are the following:

- We propose mechanisms to allow the processor and controller to cooperate effectively. One

important facet of this cooperation is permitting the processor to request communication features at low overhead. Unlike most prior studies, our techniques provide this capability while

maintaining the integrity of processor operating system features such as protection, virtual

memory, and multiprogramming.

- We examine the implementation details of the communication controller that impact the performance or functionality of other protocols differently than they impact cache coherence. To

this end, we consider a range of communication protocols to determine the requirements they share, and discuss the impact on those protocols of controller design features or restrictions.

- We study the design trade-offs for a custom FLASH memory copy protocol, and present an

implementation that leverages the support provided by the programmable communication

controller. A major focus of this design is on efficiently integrating the protocol with cache

coherence to enable the primitive to be used in a wide range of situations. This goal raises

major challenges, especially in achieving the integration while maintaining high performance.

- We present custom lock and barrier synchronization primitives for FLASH. These primitives are targeted to improve the performance of synchronization as compared to shared memory implementations by eliminating artifactual communication caused by cache coherence. We examine several conventional approaches to identify their benefits and limitations. Then we describe the implementation of the custom protocols in detail, identifying how the primitive improves performance by matching the inherent communication the operation requires.

#### 1.4 Organization

This dissertation is organized as follows:

Chapter 2 begins by describing the motivation for incorporating a programmable communication controller inside a multiprocessor. Then it describes the solution we consider, the FLASH Multiprocessor, focusing closely on the characteristics that are relevant to the alternate protocols we study.

Chapter 3 describes the design space and motivation for alternate uses of the flexible communication controller beyond cache coherence. This chapter focuses on the protocols that we implement and study in detail in later chapters: block transfer/message passing, and lock and barrier synchronization.

In Chapter 4 we explore issues arising from the division of functionality between the main processor and communication controller. In particular we present techniques that enable efficient communication between the processor and MAGIC without system calls. We also describe a range of approaches to permit MAGIC to interact with processor features such as multiprogramming, virtual memory, and protection.

Then we present the two protocol classes in detail. Chapter 5 presents the FLASH memory copy protocol, which can be used to provide message passing functionality as well as accelerate block transfer within shared memory applications. Chapter 6 presents FLASH lock and barrier synchronization protocols, designed to improve synchronization performance and characteristics beyond what can be achieved through traditional primitives based on shared memory. In each case, we first describe the design and goals of the protocol in detail, then present its implementation. Finally,

we evaluate each protocol in isolation, in the context of microbenchmarks, and within a variety of applications.

Chapter 7 describes other protocols that are amenable to using a programmable controller such as MAGIC. We describe issues associated with "active messages", which pose some unique implementation challenges, as well as other protocols that may be promising future research directions.

Finally, Chapter 8 summarizes the conclusions of the dissertation.

### Chapter 2

# The FLASH Multiprocessor

This chapter describes the Stanford FLASH Multiprocessor, a high-performance, scalable parallel computer. This dissertation uses the FLASH system as a context for the study of communication and synchronization protocols. We begin by briefly describing the background behind the FLASH system to motivate its fairly unique design. Next the FLASH architecture is described, with emphasis on the features and characteristics of particular interest for supporting advanced communication and synchronization primitives. A very complete presentation of the FLASH architecture and prototype appears in [Kus97].

### 2.1 Background and Motivation

In designing a multiprocessor, we are presented with a wide design spectrum from which to choose. We focus on two key issues: the ability of the system to scale and the different choices of communication model to present to the user. We also present the design point offered by FLASH's direct predecessor, the DASH system, before finally describing the FLASH system itself.

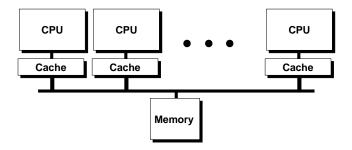

In small scale multiprocessors, the processors typically share a single bus. This style, called a bus-based or "symmetric" multiprocessor (SMP) is illustrated in Figure 2.1. SMPs can be fairly simple to design, and for small machine sizes are very effective. However, the single bus fundamentally limits their scalability. Beyond a certain size the load offered by additional processors overwhelms the bus and effective request latency increases. The exact size when this occurs depends on the performance of the processors and bus, though usually it less than 16–32 processors. Systems of this design are sometimes known as Uniform Memory Access (UMA) systems since all memory accesses take (essentially) the same latency to be satisfied.

Figure 2.1: Symmetric multiprocessor architecture.

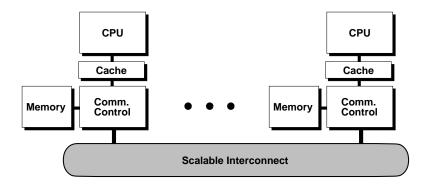

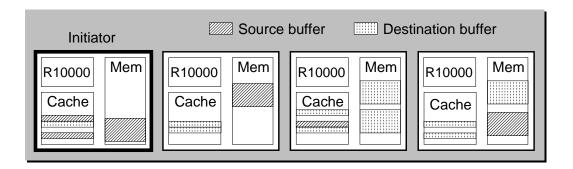

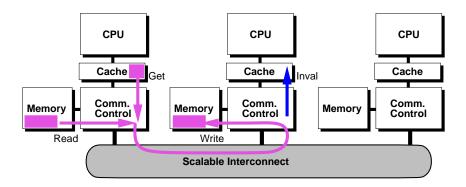

Recently, the trend in the design of multiprocessors is towards scalable architectures. To achieve scalability, SMPs have gradually been replaced by systems with several important modifications. First, the system is split into groups of resources, called *nodes*. Each node contains a small number of processors, typically between 1–4. Instead of the single memory system in an SMP, memory is distributed around the system, with each node containing a portion of the overall machine memory. Distributing the memory increases aggregate bandwidth and allows the system memory to scale without requiring expensive memory architectures such as those used in many supercomputers. Second, the single bus is replaced by a more scalable interconnect between the nodes, one that can offer more bandwidth as the system scales. With the scalable interconnect, a communication controller is introduced to manage the network. Figure 2.2 illustrates this architecture.

These scalable systems provide applications with one of the two predominant communication paradigms: *shared memory* or *message passing*. In a shared memory system, the communication controller "hides" the distribution of the machine's physical memory by transparently communicating with the correct node (and thus memory module) for processor requests to remote memory. Shared memory provided on a distributed memory system is often called Distributed Shared Memory (DSM), or Non-Uniform Memory Access (NUMA). The latter name arises because, unlike SMPs, the time to access memory depends on the location of the memory being accessed.

In some shared memory systems nodes are also permitted to hold data from remote memory locations in their cache. This can improve performance by eliminating repeated expensive misses for remote data. Caching remote memory introduces the problem, however, that modifications made to shared memory may not be globally visible. If this occurs, nodes around the system may see different values for the same memory location. This problem, known as *cache coherence*, requires that either the processor or the system hardware take special steps to assure that when a line is modified the currently cached copies are eliminated. Systems providing cache coherence support are often called Cache Coherent Non-Uniform Memory Access (CC-NUMA) machines.

The second communication paradigm found in scalable systems is *message passing*. In a message passing system, the distribution of the memory is made visible to the user; only local memory can directly be accessed by the processor using load and store instructions. Communication between

Figure 2.2: Scalable multiprocessor architecture.

nodes is accomplished through explicit *messages*. Message passing offers the system or application the ability to customize the communication granularity and timing; the drawback is that it increases the burden on the application to manage the communication. In Section 3.1 we compare these two models in further detail.

From a system design perspective, what is interesting about these two paradigms is that despite the vast differences in the interfaces they export to the user, they both utilize an architecture similar to the one in Figure 2.2. The main difference is in the design and operation of the communication controller, which usually supports one model or the other. At the beginning of the FLASH project, systems being designed elsewhere highlighted the differences between these two design styles and provided mechanisms for one or the other, instead of focusing on the extensive commonality between them [DCF<sup>+</sup>89, Int91, Thi91, Bec92, Cra93]. One of the main goals of the FLASH project is to consider the design of scalable multiprocessors, in particular the communication controller and the protocols they use, to see if both of these models (and potentially others) can be efficiently supported by a *single* system.

#### 2.1.1 The DASH Multiprocessor

To explore briefly how we might design the FLASH system, we first consider the architecture of its predecessor. In 1989, researchers at Stanford University began the design of the DASH multiprocessor (*D*irectory Architecture for *SH* ared memory) [LLG<sup>+</sup>90, LLG<sup>+</sup>92, Len92]. DASH aimed to demonstrate a real implementation of a scalable hardware-supported cache-coherent shared memory system.

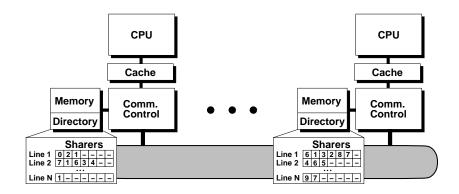

DASH is built by interconnecting small-scale bus-based commercial multiprocessors; it is comprised of SGI 4D/240 systems, which contain 4 processors each. To these systems, called a *cluster*, the DASH designers add two boards to support cache coherent distributed shared memory [Len92]. DASH uses a directory-based approach to cache coherence, which was described as early as 1978 by Censier and Fautrier [CF78]. In that approach, each node maintains a table called a *directory* that

tracks where lines are cached in the machine. In DASH, the directory is a dedicated memory array (implemented in SRAM), which stores the list of sharers in a bit vector.

DASH shows the benefits of hardware cache coherence, and that its complexities are manageable. The specific implementation of DASH has two main limitations, however. First, the system is only designed to scale to 64 nodes. In particular, the bit vector directory format used in DASH is inappropriate for larger size machines. Second, this protocol is implemented through on-board tables indicating the actions the hardware should take based on network and processor events. These tables are designed to encapsulate the hardware actions needed by the DASH protocol, but provide only limited flexibility if protocol modification should be desired for research purposes or needed to fix unexpected bugs. The ability to modify the protocol after the fact is a serious concern given the difficulty in adequately simulating and verifying large parallel machines.

#### 2.1.2 The FLASH Approach

Given this background as context, the FLASH project focuses on two main goals. The first is to study the design of scalable multiprocessor systems, with emphasis on the communication controller, to see if a single system can effectively support both cache-coherent shared memory and message passing. The second is to implement cache coherence protocols in a more flexible way, so the protocol may later be corrected, optimized, or replaced altogether.

FLASH addresses these goals by replacing the hard-coded table-based coherence protocol of systems like DASH with an embedded processor capable of handling processor and network events in *software*. Along with this processor, FLASH provides specialized hardware to improve protocol processing throughput. This style of design allows the coherence protocol to be modified and extended as needed. In addition, it permits the implementation of so-called *alternate* protocols such as message passing, scalable synchronization, fault tolerance and recovery, and performance monitoring.

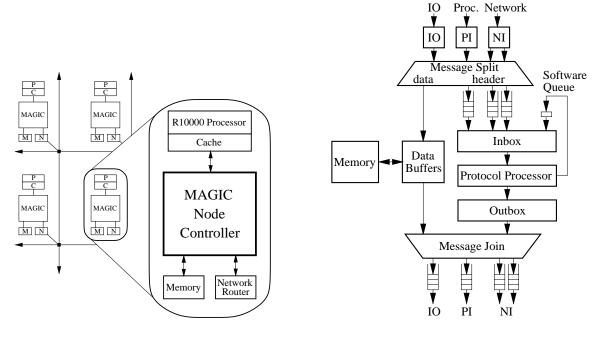

#### 2.2 FLASH Overview

The FLASH Multiprocessor is a high performance parallel computer system being designed and implemented by a team of researchers at Stanford University [KOH<sup>+</sup>94, Kus97]. FLASH (*FL*exible Architecture for *SH*ared memory) consists of a scalable array of processing nodes connected by a low-latency, high-bandwidth communication network. Each node in the multiprocessor contains all the major components of a modern high-performance scientific workstation, with the addition of a custom, programmable node controller to provide communication and other functions. The FLASH architecture is illustrated in Figure 2.3.

<sup>&</sup>lt;sup>1</sup>Though DASH does not directly provide the ability to support models other than shared memory, it does provide some optimizations in the protocol for data movement and locks.

Figure 2.3: FLASH Node Architecture.

Figure 2.4: MAGIC Microarchitecture.

#### 2.2.1 FLASH System Architecture

Each FLASH node contains a single processor, the MIPS R10000.<sup>2</sup> The R10000 is a dynamically scheduled superscalar processor that provides aggressive performance for both integer and floating point code, achieving a SPECint95 of 8.85 and SPECfp95 of 13.8 (17.5 predicted) [MIP96]. This enables the FLASH system to efficiently run not only scientific applications, which generally have heavy floating point demands, but integer-based applications as well. The R10K provides on-chip instruction and data caches, each 32 KB, as well as a variable-sized, processor-managed secondary cache. In the initial FLASH prototype, the secondary cache of the R10K is 1 MB.

The FLASH node also contains a large amount of DRAM, similar to workstations. In FLASH, this memory is part of the machine-wide distributed main memory as described earlier. Logically, the memory on a node is one piece of a contiguous physical address space beginning with address zero on node zero and ending with the physical memory on the highest numbered node. The FLASH system reserves a small portion of the memory on each node for protocol code and storage. FLASH uses this protocol storage in part to implement a directory for maintaining cache coherence, similar to DASH. By using main memory instead of a specialized memory, protocol storage can grow or shrink as needed to support arbitrary communication and synchronization protocols.

<sup>&</sup>lt;sup>2</sup>The use of a uniprocessor node in FLASH is not a fundamental restriction, but was a design decision partly driven by implementation practicality concerns. The FLASH architecture can support a multiprocessor node with only localized modifications.

In conventional workstations, dedicated hardware chipsets are typically used to control memory, I/O devices, and other board-level resources. The key innovation in the FLASH system is the use of a custom node controller, named MAGIC (Memory And General Interconnect Controller). MAGIC comprises a programmable processor optimized for executing protocol operations and dedicated data paths which provide low latency communication between the main processor, memory, and the communication ports of the node. Figure 2.4 shows the microarchitecture of MAGIC.

Besides the interface to the processor, MAGIC provides two IO interfaces on a FLASH node. For high-bandwidth, low-latency communication between nodes in the system, FLASH uses the SGI CrayLink network technology (formerly nicknamed "Spider") [Gal96]. CrayLink is configured as a "fat hierarchical hypercube topology" with data transfer bandwidth of 800 MB/s per endpoint. Figure 2.4 provides a logical view of the queues in MAGIC that are used to buffer incoming and outgoing protocol messages. We exploit the virtual lane capability of the network, which provides four incoming and outgoing network queues. This simplifies the solution for deadlock in most protocols since separate queues can be used for request and reply messages [LLG<sup>+</sup>90].

The second network is a PCI interface for use in comparably low-bandwidth I/O devices such as disk, console, graphics, Ethernet, etc. Section 2.3 describes the architecture of MAGIC in more detail, to provide background for the detailed protocol descriptions and tradeoffs described later in this thesis.

#### 2.2.2 Communication Protocol Terminology and Semantics

In this dissertation, we refer to a *protocol* to mean a specification describing the interaction among nodes in the FLASH system to accomplish a particular communication task. For example, a cache coherence protocol describes interactions between nodes aimed at providing a consistent view of memory despite caching on remote nodes. Specifically, the protocol encompasses the behavior which the participants provide in response to messages, as well as the kinds of messages they can send. In practice, protocols can be implemented in a variety of ways: using hardware, software, or a combination of both.

In the FLASH system, protocols are tightly integrated into the node through the hardware and software communication features provided by the MAGIC chip. Internally, MAGIC expresses the requests from its different interfaces in a common format, called *messages*. A message is the smallest unit of communication on FLASH, consisting of two parts: The *header* portion describes the contents of the message, its sender, receiver, data length, and other attributes useful to MAGIC. The *data* portion contains the message payload, which in FLASH is either empty (no payload), one doubleword (eight bytes), or one cache line (128 bytes). Note that these messages are not the same as application-level messages exchanged in a message passing communication model on the main processor. Rather, the messages described here are short communications used internally by the

FLASH system to implement more complicated communication operations requested by the main processor.<sup>3</sup>

Similar to the Active Message model [vECGS92], MAGIC invokes a short segment of code called a *handler* to process each message it receives. Unlike the original description of active messages which sends the actual program counter in the header of the request [vECGS92], FLASH provides an encoded *message type* instead. This message type is used along with two other attributes of the message (whether it comes from the processor or network, and whether the address is local or remote) to select a group of four possibly matching handlers from a dispatch table. These candidate handlers are then considered more closely using a number of additional attributes: a protection check (whether the sender is within the same fault containment boundary as the receiver), the availability of data buffers, additional parts of the address, and several others. By providing handler dispatch functions in hardware, a number of different attributes can be tested in parallel rather than using software-based dispatch, which would be significantly slower.

In the FLASH system, the implementation of a protocol consists of three parts. First, a set of unique message types is selected, representing the kinds of requests a node can make. When multiple kinds of communication coexist on the machine (a major focus of later chapters), each takes a subset of the message type name space for its use. Second, a collection of software handlers is created to satisfy these different requests. Finally, the dispatch table is created that describes the correspondence between the handlers and the situations in which they should be invoked (which includes the message type and the other factors described above).

Protocol handlers may need to carry out a wide range of actions to satisfy the request depending on the particular services needed. Handlers may send messages to other nodes, read and write protocol state affected by the request, perform memory operations, make requests of the local processor, or carry out other tasks internal to MAGIC. In many cases, the original request generates a response to the sender, eventually causing a handler to execute on the protocol processor of the sender's MAGIC chip. In Section 2.3.6, we consider some restrictions that must be placed upon the handlers in the FLASH system to avoid deadlock.

#### 2.2.3 Cache Coherence

In this section, we describe the cache coherence protocol in FLASH. This forms the basis on top of which the cache-coherent block transfer and other protocols are built in the remainder of this dissertation. The coherence protocol consists of two main parts. First we consider the format of the directory which is used to track outstanding copies of lines in the system. Then we consider the algorithm through which the system maintains coherence, based on the information in the directory.

<sup>&</sup>lt;sup>3</sup>Later, in discussing message passing protocols in FLASH we generally refer to these application-level messages as *block transfer*, so the distinction should be unambiguous.

Figure 2.5: Conceptual illustration of a cache coherence directory.

#### **Directory Format**

The FLASH system is fundamentally designed to allow many different protocols and directory formats to be used. Figure 2.5 illustrates a generic directory structure, showing how each node maintains directory state for its share of the machine's memory. As part of the project, other researchers have developed several completely different cache coherence protocols for FLASH to study the trade-offs in detail. For this dissertation, we have chosen to use one of the more scalable of these directory formats, *dynamic pointer allocation*, designed to support machines up to several hundreds or even thousands of nodes. The FLASH implementation of this protocol is the work of Mark Heinrich.

Dynamic pointer allocation was originally developed as part of the DASH project by Richard Simoni as a way to surpass the limited scalability of bit-vector based approaches [Sim92]. This approach takes advantage of the sharing characteristics of typical applications: most memory lines are only shared by one or two nodes at any time, while relatively few lines are shared more widely [WG89]. Unlike bit-vector or limited-pointer based formats [ASHH88], which allow for a conservative amount of caching of *each* memory line, dynamic pointer allocation uses a minimal per-line directory entry. Then it adds a pool of pointers<sup>4</sup> shared between all the lines and allocated on demand (i.e., dynamically), for use in handling lines with more widespread sharing.

The FLASH implementation of dynamic pointer allocation maintains a directory entry per memory line capable of tracking the line being cached by the local processor and one remote processor. It also maintains an array of bits used to track the state of the line (e.g., whether it is modified, whether it is busy with coherence actions, etc.). Finally, it also holds a total sharer count and the beginning of a linked list of pointer entries, which are allocated as needed from the large shared pool.

<sup>&</sup>lt;sup>4</sup>In this context, a *pointer* refers to an indication of a single remote sharer of a line.

#### **Coherence Algorithm**

The FLASH coherence protocol is a (MESI) exclusive ownership-based protocol. Lines which are read-only may be widely shared in the system, but before a line may be modified, all outstanding copies are eliminated so only a single writable copy exists. When ownership of a line is requested, FLASH eliminates outstanding copies by sending *invalidations* to remote caches currently holding the data, instructing the cache to discard the line. To improve performance, relaxed consistency models such as release consistency [Gha95] allow optimizations such as permitting writes to occur in parallel with sending the invalidations; FLASH can support many of these optimizations. As alluded to in Section 2.3.3, restrictions imposed by the processor prevent us from using an update-based approach in which modifications to the line are sent to current holders to keep their copy current.

One of the difficulties that arises in a cache coherence protocol is managing the asynchrony that occurs from many processors simultaneously sending requests. If multiple references occur to the same line, they may conflict. To make this problem more manageable, the protocol marks a line as *pending* in the directory when coherence actions are in progress (such as sending invalidations to a list of sharers in preparation for providing exclusive access). Requests for lines which are marked as busy are refused with a negative acknowledgement (NAK) and are forced to retry.

## 2.3 MAGIC (Memory and General Interconnect Controller)

This section describes the microarchitecture of MAGIC in more detail, to provide a basis for the description of the protocols in later chapters. We focus on the portions which most directly impact the protocols we implement and study; this is not intended to be a complete description of MAGIC. More details can be found in the publications on FLASH [KOH<sup>+</sup>94, HKO<sup>+</sup>94, HGDG94, Kus97, Hei]. First we provide an overview of the MAGIC microarchitecture and illustrate the way control and data are handled differently. Next we focus on the custom protocol processor (PP) inside MAGIC, with emphasis on its specialized support for communication protocols. We describe the processor interface (PI) in some detail, since it impacts the kinds of operations our protocols can use to request data from and supply data to the processor. Finally, we explain the data buffer (DB) logic which is used to stage data as it passes through MAGIC, highlighting certain special features provided by the DB for efficient protocol data movement.

#### 2.3.1 MAGIC Microarchitecture Overview

A major goal in designing MAGIC was to optimize both the protocol processing of incoming messages and the transfer of data between its interfaces. For example, MAGIC may need to decide the correct actions to maintain coherence when a request arrives, and may need to move a cache line

of data as part of the request. To accomplish this goal, MAGIC splits an incoming message into its control and data components, as illustrated in Figure 2.4. Data processing is provided by dedicated data paths that transfer data between interfaces in a pipelined fashion. Control processing is accomplished in parallel by the programmable protocol processor. The protocol processor controls macro-operations on the data paths using specialized instructions. These operations can cause, for example, an entire cache line of data to be manipulated. For example, an entire line of memory may be loaded or stored into a buffer. In this way, the protocol processor is always in charge of data movement, but is freed from the burden of handling the individual data words. The parallel handling of data and control plays an important role in achieving efficient protocol processing in FLASH. We begin by discussing the control portions of MAGIC; later we describe the data logic and how the two interact.

Keeping memory request latency low and providing high throughput are essential requirements to achieving high system performance. In the FLASH design, protocol processing efficiency is therefore critical since all requests to memory and the network are serviced by MAGIC. The microarchitecture of MAGIC is designed for pipelined protocol processing at several levels to improve throughput. At the highest level, MAGIC provides a "macro-pipeline" that allows multiple messages to be in various phases of processing simultaneously. Figure 2.4 provides an overview of the three stages in the macro-pipeline. Some of these phases also include optimizations to allow the overall latency request to be reduced as well.

The first stage, the *Inbox*, designed by Mark Heinrich, prepares an incoming protocol message for processing by the PP. The Inbox selects requests from the three hardware interfaces (the main processor, network, and PCI IO bus), and two other sources (described below), the software queue, and the idle handler. The Inbox carries out the dispatch function described in Section 2.2.2, selecting the handler to be executed by the PP. In some cases it also initiates a speculative memory operation on behalf of the incoming message, for example reading the data from memory for a cache miss. By starting the memory fetch during the Inbox phase, before the handler is even able to execute, the overall latency to satisfy a request can be reduced. In addition, it removes the need to explicitly perform a memory request in the handler code, reducing total handler *occupancy* (the length of time the PP is busy to satisfy the request) [HHS<sup>+</sup>95].

For reads, the memory operation is speculative since it was started without first consulting the directory state. In the case of a cache miss, for example, the most current copy of the data may currently be in another node's cache. In that case, the memory read was useless. In the case of writes, since our cache coherence protocol is ownership-based, a speculative write may always proceed without checking the directory state because only the current owner should issue a writeback. In Section 5.2.2 we describe how these "blind" writes slightly complicate the implementation of high performance coherent block transfer.

The Inbox also considers resource limitations in the system, such as full outgoing network FIFOs, and only selects requests from queues for which it knows MAGIC can provide certain minimum service guarantees. In Section 2.3.6, we describe how this feature is used to avoid deadlock in FLASH.

The second stage of the macro-pipeline is the Protocol Processor (PP) itself. The PP carries out the appropriate protocol actions, and often sends other requests to either the processor or the network. We discuss the protocol processor in more detail below. In the case of a cache miss, the protocol processor checks the directory state to locate the current data, and eventually sends the requested data to the processor.

The *Outbox* forms the third and simplest stage of the macro-pipeline by assuming control of any messages sent by the PP handler. The recipient unit of these messages cooperates with the Outbox and Data Buffer units to include the appropriate payload data associated with the message (if any).

#### 2.3.2 The Protocol Processor