## **Resource Management Issues for Shared-Memory Multiprocessors**

**Ben Verghese**

## **Technical Report: CSL-TR-98-753**

**March 1998**

This work was supported in part by ARPA contract DABT63-94-C-0054.

### **Resource Management Issues For Shared-Memory Multiprocessors**

**Ben Verghese**

Technical Report: CSL-TR-98-753 March 1998

Computer Systems Laboratory Department of Electrical Engineering and Computer Science Stanford University Stanford, CA 94305-2140 {pubs}@cs.Stanford.EDU

#### Abstract

Shared-memory multiprocessors (SMPs) are attractive as general-purpose compute servers. On the software side, they present the same programming paradigm as uniprocessors, and they can run unmodified uniprocessor binaries. On the hardware side, the tight coupling of multiple processors, memory, and I/O provides enormous computing power in a single system, and enables the efficient sharing of these resources. As a compute server, this power can be exploited both by a collection of uniprocessor programs and by explicitly or automatically parallelized applications. This thesis addresses two important performance-related issues encountered in such systems, performance isolation and data locality. The solutions presented in this dissertation address these issues through careful resource management in the operating system.

Current shared-memory multiprocessor operating systems provide very few controls for sharing the resources of the system among the active tasks or users. This is a serious limitation for a compute server that is to be used for multiple tasks or by multiple users. The current unconstrained sharing scheme allows the load placed by one user or task to adversely affect the performance seen by another. We show that this lack of isolation is caused by the resource allocation scheme (or lack thereof) carried over from single-user workstations. Multi-user multiprocessor systems require more sophisticated resource management, and we propose "performance isolation", a new resource management scheme for such systems.

Performance isolation has the following desirable features. It allows the resources on the system to be shared by different tasks or users. The resources can be flexibly partitioned to reflect different criteria, e.g. the share of the cost of the system paid by different groups or the importance of different tasks or users. Performance isolation guarantees the task or user its share of the machine regardless of the load placed on the system by other users, leading to isolation of tasks in a heavily-loaded system. Performance isolation is also flexible enough to allow a task or user to utilize any extra resources that may be idle in the system, leading to better performance in a lightly-loaded system. We implement performance isolation in the operating system for three important system resources: CPU time, memory, and disk bandwidth. Running a number of workloads we show that it is successful at providing workstation-like isolation and latency under heavy load, SMP-like latency under light load, and SMP-like throughput under all conditions.

Most currently available shared-memory systems have a bus-based architecture, with the processors using a common bus to access main memory. This architecture provides an uniform access time to memory, independent of the processor and memory location accessed. For performance and scalability reasons the architecture of shared-memory machines is evolving to one with multiple nodes, each with one or more processors and a portion of the global shared memory (local memory). These nodes are interconnected with a fast and scalable network. In this architecture access to memory in another node (remote memory) is significantly slower than access to memory in the local node. Such systems are called CC-NUMA systems — cache-coherent non-uniform memory-access architecture.

In CC-NUMA systems good data locality is an important performance issue. Ideally, the data accessed by a process should be allocated in memory local to the processor running the process. However, such static allocation is not possible with the dynamic workloads found on compute servers. For fairness and efficiency, a compute server needs to move processes between processors to maintain load-balance. If a process is moved away from its data it will have to make accesses to remote memory, resulting in poor data locality and a large memory stall time.

In this dissertation, we carefully study the problem of automatically providing good data locality to applications. Our solution to this problem is to provide the kernel functionality to efficiently migrate and replicate pages in response to changes in the memory-access patterns of applications. We use cache-miss counting to detect the changing memory-access patterns of dynamic workloads, and use this information to drive the decision to migrate and replicate pages in the virtual memory system. We show that our OS-based solution is very effective in maintaining good data locality in CC-NUMA machines, and is able to greatly improve application performance.

**Key Words and Phrases:** SMP, resource allocation, performance isolation, fairness, resource sharing, data locality, CC-NUMA, page migration, page replication.

Copyright © 1998 Ben Verghese

## Acknowledgments

My thesis work would not have been possible without the help, support, and encouragement of a number of people.

First, I would like to thank my advisors, Anoop Gupta and Mendel Rosenblum. Anoop's unflagging enthusiasm and demands for perfection greatly improved the quality of this thesis. Mendel's amazing system-building skills and his development of SimOS were crucial to the work done in this thesis. This thesis owes a lot to their inspiration and guidance.

I would also like to thank John Gill for graciously agreeing to be the chairman of my orals committee and for reading my thesis carefully, and John Hennessy for making time to be on my orals committee.

I am extremely grateful to my whole research group — Robert Bosch, Ed Bugnion, John Chapin, Scott Devine, Kinshuk Govil, Steve Herrod, Dan Teodosiu, Emmett Witchel — for all their encouragement and help, especially through those endless paper-deadline nights. This thesis would have been considerably harder if the whole group had not developed a superb simulator (SimOS) and had not indulged in many hours of crazy soccer, both indoors and outdoors.

I would particularly like to acknowledge Scott Devine, my co-conspirator in all the "Data Locality" work.

A number of people on the FLASH hardware team were extremely helpful, especially Joel Baxter, Mark Heinrich, Dave Ofelt, and Dave Nakahira who patiently answered my many questions about the MAGIC chip and other hardware-related issues.

I would like to thank my parents for their love and support. Their faith in my ability to succeed gave me the confidence to embark on this adventure. Finally my wife Preeti, who having been through this experience herself, was always there for me, celebrating my successes and helping me to overcome my failures. I thank her for her love.

# **Table of Contents**

| 1 | Introduction                                          | 1         |

|---|-------------------------------------------------------|-----------|

|   | 1.1 Shared-Memory Multiprocessors as Compute Servers  | 3         |

|   | 1.2 The Architecture of Shared-Memory Multiprocessors | 4         |

|   | 1.3 Challenges for the Operating System               |           |

|   | 1.4 The Performance Isolation Problem                 |           |

|   | 1.4.1 Problem Description                             | 7         |

|   | 1.4.2 Results and Contributions                       | . 11      |

|   | 1.5 The Data Locality Problem                         | . 12      |

|   | 1.5.1 Problem Description                             |           |

|   | 1.5.2 Results and Contributions                       |           |

|   | 1.6 Organization of the Thesis                        |           |

|   |                                                       |           |

| 2 | Performance Isolation                                 | 19        |

|   | 2.1 The Performance Isolation Model                   |           |

|   | 2.1.1 Providing Isolation                             |           |

|   | 2.1.2 Policies for Sharing                            |           |

|   | 2.2 Kernel Implementation                             |           |

|   | 2.2.1 CPU Time                                        |           |

|   | 2.2.2 Memory                                          | . 28      |

|   | 2.2.3 Disk Bandwidth                                  | . 29      |

|   | 2.2.4 Shared Kernel Resources                         | . 31      |

|   | 2.3 Summary                                           | . 33      |

| 2 |                                                       | 25        |

| 3 | Experimental Environment                              | 35        |

|   | 3.1 SimOS                                             |           |

|   | 3.2 Machine Architecture                              |           |

|   | 3.2.1 Common System Parameters                        |           |

|   | 3.2.2 Performance Isolation Specific Parameters       |           |

|   | 3.2.3 Data Locality Specific Parameters               |           |

|   | 3.3 Operating System                                  | . 40      |

| 4 | Experimental Results for Performance Isolation        | 41        |

| • | 4.1 Experimental Setup                                |           |

|   | 4.2 Workload Description                              |           |

|   | 4.3 Experiments Using the Pmake8 Workload             |           |

|   | 4.3.1 Isolation                                       |           |

|   | 4.3.2 Resource Sharing                                |           |

|   | 4.3.3 Comparison with a Single Workstation            | <u>48</u> |

|   | 4.4 Experiments Using the CPU Isolation Workload      | 51        |

|   |                                                       | . 51      |

|   | <ul> <li>4.5 Experiments Using the Memory Isolation Workload</li> <li>4.6 Experiments Using the Disk Bandwidth Isolation Workload</li> <li>4.7 Summary of Results</li> </ul> | 54        |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 5 | Data Locality                                                                                                                                                                | 59        |

|   | 5.1 Process Scheduling                                                                                                                                                       | 61        |

|   | 5.2 A Framework for Providing Data Locality                                                                                                                                  | 63        |

|   | 5.2.1 The Problem Definition                                                                                                                                                 | 63        |

|   | 5.2.2 Policy Structure                                                                                                                                                       |           |

|   | 5.3 Cache Miss Counting                                                                                                                                                      |           |

|   | 5.4 Kernel Implementation                                                                                                                                                    |           |

|   | 5.4.1 Policy Implementation                                                                                                                                                  |           |

|   | 5.4.2 New Kernel Functionality                                                                                                                                               |           |

|   | 5.4.3 Performance Optimizations                                                                                                                                              |           |

|   | 5.5 Summary                                                                                                                                                                  | 78        |

| 6 | Experimental Results for Data Locality<br>6.1 Workload Characterization                                                                                                      | <b>81</b> |

|   | 6.2 Execution Time Improvement                                                                                                                                               |           |

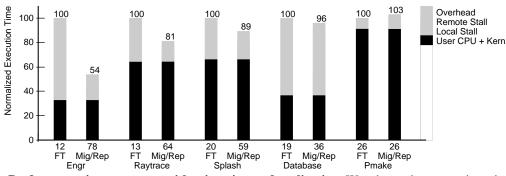

|   | 6.2.1 Results for the Engineering Workload                                                                                                                                   |           |

|   | 6.2.2 Results for the Raytrace Workload                                                                                                                                      |           |

|   | 6.2.3 Results for the Splash Workload                                                                                                                                        |           |

|   | 6.2.4 Results for the Database Workload                                                                                                                                      |           |

|   | 6.2.5 Results for the Pmake Workload                                                                                                                                         |           |

|   | 6.3 System-wide Benefit                                                                                                                                                      |           |

|   | 6.4 Analysis of Kernel Overheads                                                                                                                                             |           |

|   | 6.5 Discussion                                                                                                                                                               |           |

|   | 6.5.1 TLB Misses and Other Metrics                                                                                                                                           | 96        |

|   | 6.5.2 Alternative Policies                                                                                                                                                   |           |

|   | 6.5.3 Memory Pressure and the Memory Space Overhead                                                                                                                          |           |

|   | 6.5.4 Sensitivity to parameters                                                                                                                                              |           |

|   | 6.6 Scalability                                                                                                                                                              |           |

|   | 6.7 Summary of Experimental Results                                                                                                                                          | 104       |

| 7 | Related Work                                                                                                                                                                 | 107       |

|   | 7.1 Performance Isolation                                                                                                                                                    |           |

|   | 7.2 Data Locality                                                                                                                                                            |           |

|   | 7.3 Other Related Work                                                                                                                                                       | 112       |

| 8 | Concluding Remarks                                                                                                                                                           | 113       |

|   | 8.1 Performance Isolation                                                                                                                                                    |           |

|   | 8.2 Data locality                                                                                                                                                            |           |

|   | 8.3 Future Work                                                                                                                                                              |           |

|   | 8.3.1 Performance Isolation                                                                                                                                                  | 117       |

| 8.3.2 Data Locality | <br> | <br> |     |

|---------------------|------|------|-----|

| References          |      |      | 119 |

# **List of Tables**

| TABLE 1.  | Summary of the performance isolation implementation            | 26 |

|-----------|----------------------------------------------------------------|----|

| TABLE 2.  | Parameters for the experimental environment                    | 39 |

| TABLE 3.  | Different resource allocation schemes for MPs                  | 42 |

| TABLE 4.  | Description of the workloads used for the performance results  | 44 |

| TABLE 5.  | The effect of performance isolation on a disk-limited workload | 56 |

| TABLE 6.  | The advantage of considering both head-position and fairness   | 56 |

| TABLE 7.  | Key parameters used by the policy                              | 69 |

| TABLE 8.  | Description of the workloads.                                  | 82 |

| TABLE 9.  | Execution time statistics for the workloads                    | 85 |

| TABLE 10. | Breakdown of actions taken on hot pages                        | 88 |

| TABLE 11. | Latency of various functions in the implementation             | 92 |

| TABLE 12. | Breakdown of total kernel overhead by function                 | 93 |

| TABLE 13. | Effect of Memory Pressure on policy performance 1              | 00 |

|           |                                                                |    |

x

# **List of Figures**

| FIGURE 1.   | Architecture of bus-based shared-memory multiprocessors4                    |

|-------------|-----------------------------------------------------------------------------|

| FIGURE 2.   | Architecture of CC-NUMA shared-memory multiprocessors                       |

| FIGURE 3.   | Trade-offs when clustering computing resources                              |

| FIGURE 4.   | Lack of isolation in MP compute servers                                     |

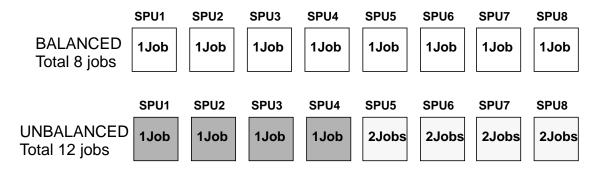

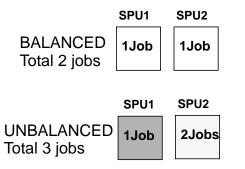

| FIGURE 5.   | Balanced and Unbalanced configurations for the Pmake8 workload45            |

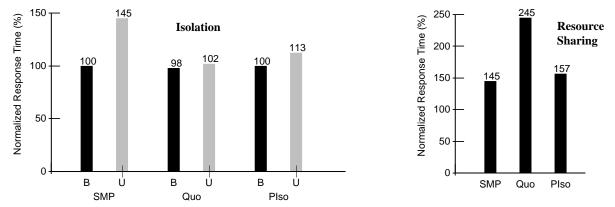

| FIGURE 6.   | Effect of Isolation in the Pmake8 workload                                  |

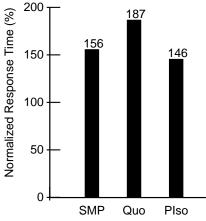

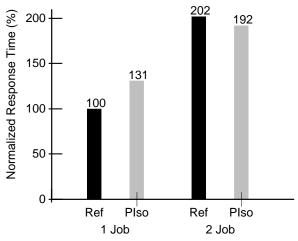

| FIGURE 7.   | Effect of resource sharing in the Pmake8 workload                           |

| FIGURE 8.   | Comparison with a single workstation                                        |

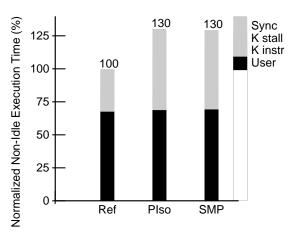

| FIGURE 9.   | Non-idle execution times for Pmake8 workload                                |

| FIGURE 10.  | The structure of the CPU Isolation workload                                 |

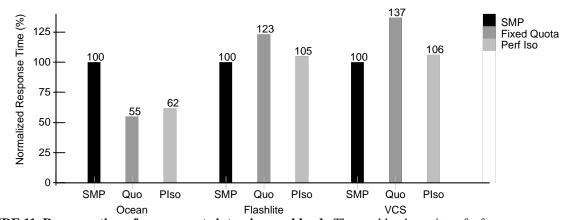

| FIGURE 11.  | Response times for a compute intensive workload                             |

| FIGURE 12.  | Balanced and Unbalanced configurations for the memory-isolation workload 53 |

| FIGURE 13.  | Performance Isolation for a memory-limited workload                         |

| FIGURE 14.  | Motivation workload with and without performance isolation                  |

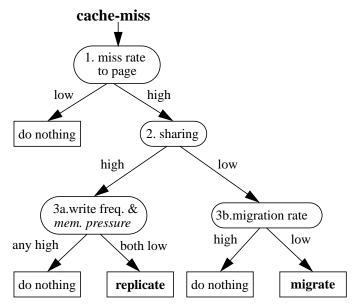

| FIGURE 15.  | Replication/Migration decision tree                                         |

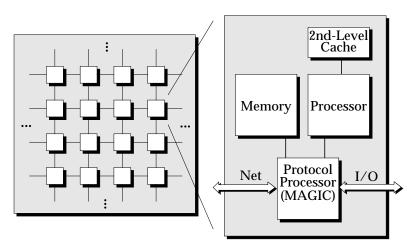

| FIGURE 16.  | The Stanford FLASH multiprocessor                                           |

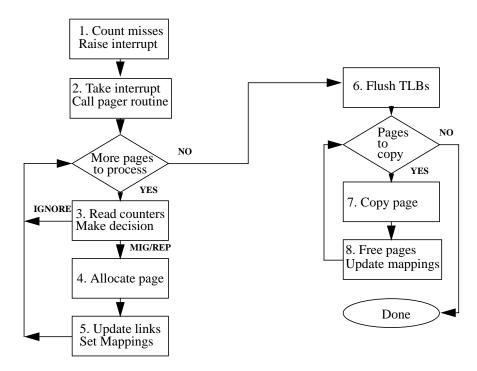

| FIGURE 17.  | Flow chart for migration or replication                                     |

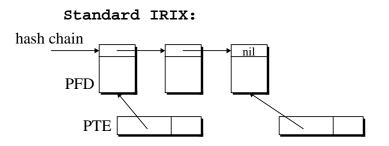

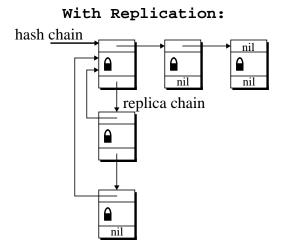

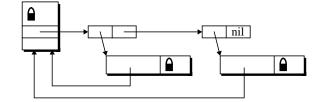

| FIGURE 18a. | Standard IRIX hash table structure                                          |

| FIGURE 18b. | Hash table structure with replication75                                     |

| FIGURE 18c. | Hash table structure with back mappings                                     |

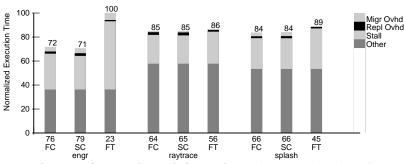

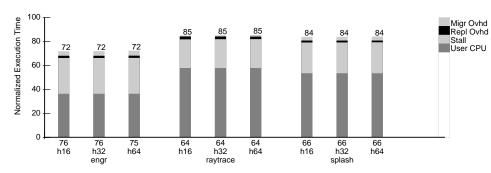

| FIGURE 19.  | Performance improvement with migration and replication                      |

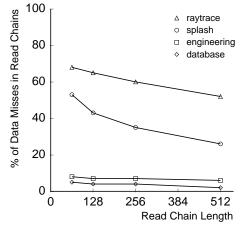

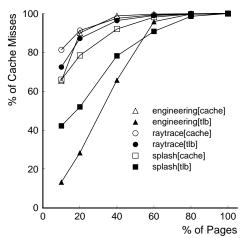

| FIGURE 20.  | Percentage of data cache misses in read chains                              |

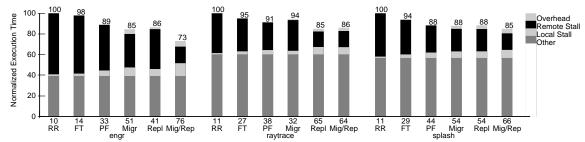

| FIGURE 21.  | Performance impact of approximate information                               |

| FIGURE 22.  | Effectiveness of TLB misses for finding hot pages                           |

| FIGURE 23.  | Comparison of different static and dynamic policies                         |

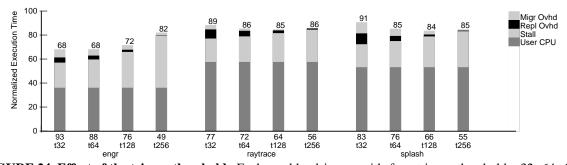

| FIGURE 24.  | Effect of the trigger threshold101                                          |

| FIGURE 25.  | Effect of the sharing threshold102                                          |

## Chapter 1 Introduction

The last thirty years of mainstream computing have seen significant changes in the basic computing paradigm in response to the evolution of computing technology and the concurrent changes in the requirements of users and applications. In the early days, the computing paradigm was essentially a centralized one, mostly mainframe systems that were shared by a large number of users. A centralized model was appropriate at that time because computing resources were scarce and expensive, and efficient utilization of these expensive resources was the primary concern.

In response to a variety of factors, this centralized computing paradigm gradually changed to a more distributed computing paradigm; personal workstations connected over a network. The main reasons for this change were:

- The cost of computing resources reduced dramatically. The first cracks appeared with minicomputers that were cheaper to build, resulting in some degree of decentralization. The advent of the microprocessor speeded up the process of change. The microprocessor enabled manufacturers to build relatively inexpensive personal workstations that rivalled the minicomputer in processing speed.

- The graphical display directly connected to the personal workstation replaced the clunky terminal. This change gave users a more sophisticated user interface, enabling more complex interactions between the user and the computer.

• The personal workstation gave the user significantly better control over the performance of applications running on it. In the centralized model in some cases, system overload conditions caused considerable user frustration.

More recently the computing paradigm is gradually shifting back to a more centralized model. The widespread adoption of computers in the workplace has exposed inefficiencies in the highly distributed model of computing. Two important factors driving this shift are:

- The cost of computing resources is no longer a large fraction of total cost of ownership of a desktop computer. A recent Gartner Group study [Gar94] showed that only about 27% of the costs of a network of computers were technology costs, i.e. for the hardware and software. The rest were personnel costs for maintaining this distributed computing environment, i.e. administration, troubleshooting, installation, support, and training.

- Second, a completely distributed environment results in the duplication of data and the fragmentation of resources. Every user must have enough resources on their system to accommodate the largest possible application they may want to run. For example, a single task requiring more memory than is available on a workstation cannot be run efficiently even though there is plenty of idle memory on other workstations in the network.

The client-server computing paradigm has emerged to address these concerns. The clients are simple personal computers with a good display capability and only limited computing and storage resources; moving more in the direction of "thin clients" in the future. These clients maintain very little permanent state, and so do not require much by way of system administration. The bulk of the actual computing resources is centralized in powerful and efficient servers. Only these servers, much fewer in number than the clients, have to be administered carefully. Examples of these servers are file servers, web servers, and database servers for centralizing information retrieval and storage, and also general-purpose compute servers that are able to efficiently run large tasks for users; ones that they would not be able to run on the clients or on personal workstations.

Client-server computing has generated an interest in servers. We will first discuss why sharedmemory multiprocessors are well suited to assume the function of servers (Section 1.1). Next, we will describe the current and evolving architecture of shared-memory multiprocessors (Section 1.2). In Section 1.3, we examine the new demands being placed on the operating systems for these machines when they are used as servers. Specifically, we identify two important resource Introduction

management issues that we explore in this thesis — "Performance Isolation" (Section 1.4) and "Data Locality" (Section 1.5). In Section 1.4 and Section 1.5, we will also present a summary of the results and the contributions of this thesis for each of these two operating systems issues. Finally we describe the organization of the remainder of this thesis in Section 1.6.

### 1.1 Shared-Memory Multiprocessors as Compute Servers

Shared-memory multiprocessors are now being widely used as large servers. There are two important reasons why these machines are being selected for this purpose. First, shared-memory systems aggregate a large collection of computing resource — multiple processors, large amounts of memory, and I/O — in a tightly-coupled system. Second, they provide a familiar view of memory, a single cache-coherent physical address space independent of the processor making the access and of the memory location being accessed. This hardware cache-coherence provides transparent low latency access to memory from the processors.

These two features are attractive for a number of reasons:

- The entire set of legacy applications available for the particular architecture can run on this server without any modifications, including sequential programs that run on an equivalent uniprocessor system.

- The single physical address space paradigm is also familiar to programmers, the one that they are used to with uniprocessor systems. This makes it easier to speed up large programs by parallelizing them and using the multiple processors available on these systems.

- These systems can be exploited in different ways by different types of applications. Sequential applications can now process larger data sets that could not fit in the memory of any single workstation [VeR97]. Parallel applications can use the multiple processors to achieve significant speedups. I/O bandwidth limited applications can exploit parallel I/O to a common buffer pool.

- Efficient utilization of the total computing resources is possible through fine-grain sharing. The tight coupling gives the OS great flexibility to schedule multiple applications.

The Architecture of Shared-Memory Multiprocessors

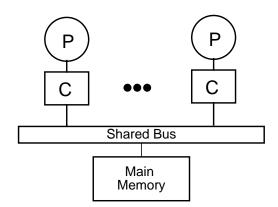

**FIGURE 1. Architecture of bus-based shared-memory multiprocessors.** Most current shared-memory multiprocessors have a bus-based architecture, with multiple processors (P), with their caches (C), connected to main memory through a shared bus. This type of architecture is called UMA (uniform memory architecture) because any processors can access any memory location with the same latency.

#### **1.2 The Architecture of Shared-Memory Multiprocessors**

Most current shared-memory multiprocessors use hardware-support to provide a cache-coherent single physical address space across the whole system. This architecture guarantees two important properties for all memory accesses. First, the single physical address space property guarantees that any memory location can be directly addressed by any processor, and can be read or modified through load and store instructions. Second, the cache-coherence property guarantees that the value read or modified is the most current value corresponding to the memory location addressed; the cache-coherence hardware finds the most current value, either from memory if it is clean, or from one of the caches in the system if it is dirty.

Most current cache-coherent shared-memory multiprocessors are small (4 - 8 PEs), and are designed around a shared bus as shown in Figure 1. This shared bus connects all the CPUs to the main memory of the system. These bus-based systems are called *uniform memory access* (UMA) systems because any processor can access any memory location with the same latency. Cache coherence is implemented by processors snooping memory requests on the shared bus, and responding appropriately if they have a copy of the requested line in their cache [PaH96]. However, this bus-based architecture does not scale to larger systems because contention for the bus increases as processors are added to the system. The shared memory bus becomes the bottleneck in the system, and the latency of all memory accesses increases.

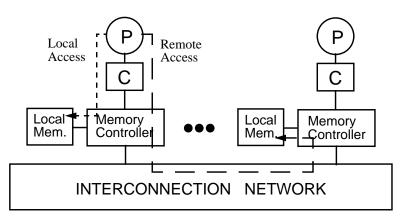

**FIGURE 2.** Architecture of CC-NUMA shared-memory multiprocessors. The figure shows the CC-NUMA (cache-coherent non-uniform access) architecture for scalable shared-memory multiprocessors. This architecture allows fast access to data in local memory and slower access to data in a remote memory. The dashed lines show sample paths taken for local and remote memory access. Each node has a specialized memory controller, and the memory controllers in all the nodes co-operate using directory techniques to maintain cache-coherence across the system.

The dominant architectural solution to this scalability problem is the distributed shared-memory architecture also known as the *cache-coherent non-uniform memory-access architecture* (CC-NUMA) [PaH96]. In this architecture the machine is divided into a number of nodes as shown in Figure 1. Each node consists of one or more processors and a part of main memory. These nodes are connected using scalable interconnect technology, and cache coherence is provided by a special memory controller using directory techniques. As processors get faster and their architecture gets more sophisticated, the shared bus will be a bottleneck even for smaller multiprocessors. Therefore, the CC-NUMA architecture is likely to be adopted even for smaller systems. These CC-NUMA machines were first designed in academia, Stanford DASH [LLG+90] and MIT Alewife [ABC+91]. A number of these machines have recently become available commercially, such as the Sequent STiNG [LoC96], Convex Exemplar [BrA97], Data General NumaLiine and SGI ORIGIN 2000 [LaL97].

CC-NUMA systems have different memory-access latencies depending on the location of memory. They provide fast access to data that is in memory local to the node. The latency for access to data in remote memory is considerably larger. The local access can be satisfied by the local memory controller without communicating with any other part of the system. The remote access takes longer because the local memory controller has to communicate with other nodes to satisfy the request as shown in Figure 1. The ratio of local to remote access latency is a function of the memory-controller architecture, the directory protocol used, and the interconnection network. Published numbers for the ratio of local to remote access latency for some systems include 1:3 for the Stanford DASH machine [LLG+90], 1:4 expected for the Stanford FLASH machine [KOH+94], 1:2 for small configurations and 1:3 for large configurations for the SGI ORIGIN system [LaL97], 1:8 for the Sequent STiNG system. These numbers are for latencies without any contention on an idle system. These latencies can increase significantly with contention. The disparity in the access time for local and remote memory makes data locality an important issue on these systems.

### 1.3 Challenges for the Operating System

Typical compute server workloads are quite different from large stand-alone parallel applications, which were an important initial motivation for the design of scalable shared-memory multiprocessor systems. Today, compute-server workloads consist of multiple applications with potentially widely differing characteristics. They may be sequential or parallel, long-lived or short-lived, memory-intensive, CPU-intensive or I/O intensive. These workloads are multiprogrammed and very dynamic, with the applications constantly entering and leaving. These multiprocessors also represent a large aggregation of computing resources that will potentially be used for multiple tasks and shared by multiple users or projects. Some examples of workloads running on multiprocessor compute servers include:

- A database server (with multiple threads) replying to queries from many clients.

- A web server and a video-streaming server providing information service to a whole building.

- Many long running jobs from multiple users on a machine, where each user owns a fraction of the machine.

- Multiple parallel scientific applications in a multiprogrammed workload.

Such environments require intervention from the operating system to carefully allocate resources to different tasks, making trade-offs where required. These trade-offs are generally between the performance of individual applications or users and system-wide performance qualities such as fairness, efficiency and throughput. The usage of computing resources, such as CPU time, memory, disk bandwidth and I/O bandwidth, by different applications needs to be managed on a continuous basis. For example in the workload above with a web server and a video server, it is important that the OS carefully manage the usage of disk and network bandwidth along with CPU time and memory. Given the dynamic and multi-user nature of these workloads, static allocation

and partitioning of resources is either not possible or will lead to poor response time for individuals, and poor throughput for the whole system.

This thesis identifies, analyzes, and proposes solutions for two important performance issues for multiprocessor compute servers. Both involve interesting trade-offs between individual applications and user performance on one hand, and overall system issues such as fairness, efficiency and load-balance on the other. The two issues we will address are performance isolation and data locality.

- **Performance Isolation:** Can the operating system provide performance guarantees to groupings of processes representing individual users or tasks in a multiprogrammed environment, and at the same time maintain the fine-grain sharing of machine resources that is important for good throughput.

- Data locality: Can the operating system automatically provide good data locality on CC-NUMA systems (i.e. ensure that most of the cache misses are to local memory), even though applications are being moved around among the processors to maintain load balance in response to the dynamic nature of the workload.

We discuss each of these two issues in greater detail in the next two sub-sections.

### **1.4 The Performance Isolation Problem**

In this section, we will first motivate and describe the performance isolation problem and then present the results and contributions of this thesis.

#### **1.4.1 Problem Description**

Current operating systems present the user with two fairly sub-optimal choices for a computeserver solution. As an illustration, let us take the example of end-users accessing information over the web. For simplicity we consider a content provider (CP) providing information resources to a number of high-end customers. The customers needs are diverse, and the CP provides web page service, video service, SQL-based data access, etc.

The CP has basically two possible server solutions available today. The first solution is to provide a separate machine for each service. Each machine must be configured with enough resources to

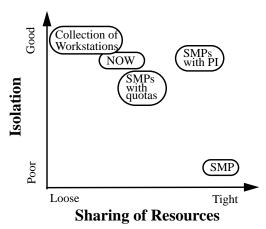

**FIGURE 3. Trade-offs when clustering computing resources.** We consider the effectiveness of different ways of clustering computing resources, as collections of workstations or as shared-memory multiprocessors with equivalent configurations (processors, memory, and I/O resources). The two axes here are sharing of resources and isolation of performance. A network of workstations (NOW) provides good isolation of performance, but poor sharing of resources. The situation is the opposite for current SMPs. SMPs with fixed quotas fall somewhere in between. With Performance Isolation on shared-memory multiprocessors (SMPs with PI), we get most of the ben-efit on both axes, workstation response times under heavy load, and SMP response times under light load.

handle the peak requirements of the service. This solution leads to an over-commitment of resources, and is inefficient because a large fraction of the resources are potentially idle at any time. The consequence will be higher hardware and maintenance costs for the CP (and the end-user).

The second solution is to have the different services share a multiprocessor system. The multiprocessor solution provides more efficient utilization of resources, but could lead to interference between the services. For example, a flurry of queries to the web server could cause enough disk activity and force the video server to miss deadlines because of delayed disk accesses. Similarly, web accesses may interfere with video data at the network interface. In a different scenario, a complex query on the SQL server may be executed in parallel and starve the web server and video server of CPU time. There can be no assurance of predictable service and this choice could lead to a decrease in customer satisfaction. The ideal solution should provide both cost efficiency and customer satisfaction (performance).

We explore this trade-off in Figure 3. The two axes on the graph represent two desirable qualities for compute servers. The x-axis represents the ability of the system to share computing resources between processes. Shared-memory systems with their tight coupling are able to efficiently share resources at a fine grain. The y-axis is isolation, i.e., how well can different tasks or groups of tasks control their expected performance and not be affected by the load placed on the system by

others. Here the more distributed solution, in the form of individual workstations or networks of workstations (NOW) [ACP+94], fares significantly better than current shared-memory multiprocessors. The workstation solution has implicit isolation because jobs are run on separate workstations.

Current operating systems have little support for controlling the allocation of resources to groups of processes, or for providing fairness by any abstraction other than individual processes. The existing controls for fairness regulate only access to the CPU by a process. There are few controls for allocating other resources that can affect performance, such as memory and I/O bandwidth. A compute-server may be shared by multiple users, groups of users, or by multiple important tasks, and therefore needs more sophisticated controls for sharing resources.

The lack of control over resource sharing leads to poor isolation in current shared-memory multiprocessors. As a result of unconstrained sharing, the performance seen by an individual user in a multi-user environment is dependent on the load placed on the system by other users. Users have no reasonable guarantee of minimum performance even if they are using much less than the share of the resources they are entitled to. A single user or process can easily load the system unfairly, and tie up a large fraction of the resources. Examples of activities that can lead to unfair load are a user starting many processes, a process touching a large number of pages resulting in a huge working set, or a process making a large number of accesses to a disk. The lack of good resource control mechanisms has generated the perception that shared-memory systems cannot isolate a user from interference, and resulted in many detractors of these systems.

We use an example to illustrate the extent of the interference between jobs caused by the lack of isolation on a shared-memory multiprocessor. Consider a user running a job on a uniprocessor workstation. The job in this case is a parallel make with two simultaneously active compiles. This user now shares in buying a multiprocessor with three other users. This is a four-way multiprocessor that has four times the memory and disks as the uniprocessor. User A expects better performance than on the uniprocessor when the system is idle. Also, user A's share of the computing resources of the multiprocessor is equivalent to that of the uniprocessor system. Therefore, user A may expect that the observed performance on the multiprocessor should at worst be comparable to the uniprocessor performance when the other users are also active.

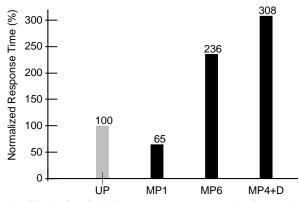

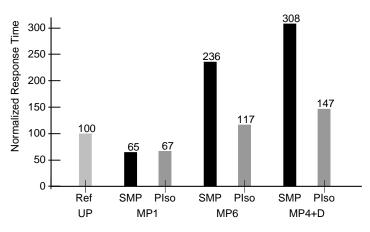

**FIGURE 4. Lack of isolation in MP compute servers.** The figure shows the response time for a Pmake job on an MP for three different system workloads relative to the uniprocessor case (UP). MP1 is just the single Pmake. MP6 is six simultaneous Pmake jobs accessing different disks. MP4+D is 4 simultaneous Pmake jobs, with one large file copy or core dump happening to the disk of one of the Pmakes.

Figure 4 shows the performance<sup>1</sup> of user A's pmake job on the uniprocessor and the multiprocessor, normalized to the uniprocessor case (UP), under various system load conditions. In the first multiprocessor case (MP1), user A is the only one using the system. User A's job is able to finish quicker (35% improvement) by utilizing the idle processors and additional memory. More available resources under low-load conditions is the primary attraction of moving to a shared-memory multiprocessor for compute-server type workloads. Idle resources are easily exploitable unlike a workstation solution.

We now consider two interference scenarios that may be familiar to users of shared multiprocessors. When other users increase the load on the system, the performance of User A's job steadily gets worse even though its resource requirements do not change. MP6 represents the first such scenario, where the other three users have started five similar jobs on the system for a total of six jobs. If the system was fair, user A who is only running one job might have expected to see a response time approximately that of the uniprocessor workstation. Response time for user A's job has increased to **236%** of the uniprocessor case.

The other scenario is four users each running a job, and one of the other users causes a core dump to the disk on which the sources for user A's compile job reside (MP4+D). In this case, user A

The uniprocessor system models a MIPS R4000 based workstation and the multiprocessor corresponds to a similar MIPS R4000 based CHALLENGE multiprocessor from Silicon Graphics, both running the IRIX5.3 kernel. The results shown here are obtained using the SimOS simulation system, and the specific architectural parameters of the systems will be defined in Section 3.2.

might have expected to see a slight increase in response time over that of the uniprocessor case because of sharing of disk bandwidth. Instead, the response time for user A's job in this case is over **three** times what it was on the uniprocessor due to the writes caused by the core dump competing for disk bandwidth with the pmake. These examples clearly show that the performance seen by an individual user on these systems is completely dependent on the background system load and the activities of other users; clearly enough incentive to retreat to individual workstations.

The "Network of Workstations" solution for aggregating resources is not the appropriate model. These systems provide good isolation and response time for an individual's jobs at the cost of overall throughput. There is a much higher overhead for sharing resources because it is a loosely coupled system. Therefore, fine-grain sharing is difficult, and idle resources can only be allocated at a very coarse granularity.

One possible solution to provide isolation on shared-memory systems is to enforce fixed quotas. However this solution is too static, and would not allow the sharing of idle resources. Fixed quotas will significantly reduce the throughput and response time seen on these systems under lightload conditions as we will show later.

The performance isolation problem for the operating system is to allow users to easily utilize idle resources on a lightly-loaded system, while at the same time isolating the performance of a user from the load placed on the system by other users. This can be translated into getting the best of what workstations and SMPs currently provide; the efficient sharing and overall throughput of the SMP and the isolation of the workstation.

#### **1.4.2 Results and Contributions**

- This thesis shows that the lack of predictable performance for tasks is not inherent to sharedmemory multiprocessors. It is an artifact of the limited CPU-centric resource allocation scheme used by current SMP operating systems, as inherited from single-user workstation operating systems.

- To solve this problem we propose a new comprehensive resource allocation scheme for sharedmemory multiprocessors— Performance Isolation. Performance isolation is capable of dealing with any entity, not just a single process, such as tasks, users, or groups of users, and allows the

machine resources to be flexibly partitioned among such entities. It also encompasses all resources that can affect performance, such as memory and I/O bandwidth, and not just CPU time. The objective of this model is to provide groups of processes with predictable performance corresponding to their assigned share of resources independent of system load. This performance is to be achieved without compromising the fine-grain sharing of idle resources and efficient resource utilization provided by shared-memory multiprocessors.

- We outline the general framework for providing performance isolation based on a new kernel abstraction called the SPU (Software Performance Unit). The SPU encompasses facilities for monitoring resources used by groups of processes, limiting resource usage, and allowing careful sharing of idle resources. The actual implementation of the model for CPU time, memory, and disk bandwidth in the IRIX 5.3 kernel from Silicon Graphics is discussed in detail, providing working solutions to problems encountered.

- Our solution for providing fairness for disk bandwidth is quite novel. The solution balances fairness and disk-head position when scheduling disk requests. An implementation of fairness that does not take into account disk-head position will result in lower overall throughput because of higher seek latencies.

- By running specific workloads, we highlight how performance isolation achieves its objectives for individual resources and for applications in general. Overall we show that the performance isolation model is able to provide the best of individual workstation and SMP performance, under different conditions of individual user requirements and system load.

#### **1.5 The Data Locality Problem**

In this section, we will first motivate and describe the data locality problem and then present the results and contributions of this thesis.

#### **1.5.1 Problem Description**

The higher latency for satisfying a cache miss from remote memory in CC-NUMA systems makes it essential that an application find most of its important data in local memory. On a cache miss, the processor is potentially stalled for the duration of the latency to fetch the required data from memory. As processors get faster applications spend a larger fraction of their execution time

stalled for memory. A large number of cache misses to remote memory could severely impact application performance because of the larger resulting memory-stall time. The higher remoteaccess latency is important even for newer processors that can have multiple outstanding misses to memory, and so overlap and hide some of the cache-miss latency. The number of outstanding misses in these processors is usually a small number, and it is very hard to hide the long latency to access remote memory.

There are many reasons why a process may not find its data in local memory. First, the user or application writer may not care to do data placement. Second, even if they do want to, they may not be able to do so for a number of reasons.

- The static solution of locking processes to processors, and placing data in the appropriate local memory will not work for compute server workloads. In a dynamic environment, where applications enter and leave the system, for load-balance and fairness reasons the operating system will eventually need to relocate a process to a different node. Once a process changes nodes, the data that was initially placed in local memory will now be remote. In such cases the process itself cannot do much to improve data locality because it is not aware of remote memory, and it is not informed when it is moved.

- Even if a process were to stay relatively fixed to a processor for a period of time, processes with a large memory footprint are likely to find that all their data does not fit in local memory. As their access patterns change with time, many of the misses will go to remote memory.

- Even for stand-alone parallel applications, the programmer may not always be able to do static placement because the access patterns may be data dependent or may not be captured through static placement.

The data locality problem for the OS on CC-NUMA systems is to ensure that an application finds most of its important data in local memory while also maintaining load-balance and fairness across the entire workload. In our experiments running compute-server workloads with NUMA-unaware operating systems, the data locality was very poor; 12% of misses to local memory in an eight-node system, which is no better than random (details in Section 6.2).Therefore, it is important that the current working set of the process, currently running on the local processor, be moved to local memory as and when this changes. The overhead for providing good data locality should also be kept low so that the application sees an overall improvement in performance.

#### **1.5.2 Results and Contributions**

The solution to the data locality problem for distributed shared-memory (or CC-NUMA) multiprocessors has two parts. Process scheduling decides on which processors different processes are scheduled, and this determines where cache misses originate. The virtual memory system (VM) decides where the data is located in physical memory, and this determines where cache misses are satisfied. Both process scheduling and the VM need to work in conjunction to solve the datalocality problem.

Earlier work by us for process scheduling on CC-NUMA multiprocessors [CDV+94] showed that:

- For sequential applications, *affinity* scheduling is very effective in reducing the memory-stall time of applications over regular UNIX scheduling. Affinity scheduling schedules processes to improve reuse of data cached at various points in the memory hierarchy. More specifically, cache affinity is affinity acquired for a processor because of state built up in its caches. Cluster affinity is affinity for a group of processors in a clustered environment like the DASH system [LLJ+92] because of state built up in other caches in the cluster.

- Importantly, affinity is also required to keep a process from moving away from the memory that holds its data. Memory affinity is crucial to see benefits from migration and replication of data. The overhead to bring data to local memory is paid up front, but the benefit from data locality will increase the longer the process stays local to this memory.

- Scheduling schemes that are aware of parallel applications can provide modest benefits over standard UNIX scheduling. This is true for both time-partitioned schemes like gang scheduling<sup>1</sup> [Ous82] and space-partitioned schemes like process control<sup>2</sup> [ABL+91] [TuG91]. The improvement is dependent on the relative importance of data distribution and the non-linearity of the speedup curve, the former favoring gang scheduling and the latter favoring process control.

- In multiprogrammed parallel workloads the data placement assumptions of the programmer

<sup>1.</sup> In gang scheduling multiple parallel applications share a machine through time slicing and all processes of a parallel application are scheduled at the same time on different processors.

<sup>2.</sup> In process control scheduling each parallel application is allocated a subset of the processors, and the number of processes active in the parallel application changes to match the number of processors allocated to the application.

break down. Even gang-scheduled applications cannot assume a static environment because processes will be moved for load balancing purposes. OS support for automatic data locality becomes very important.

In this thesis we build on these results and focus on the virtual memory aspect of the data-locality problem. We assume affinity scheduling for sequential applications, and consider the impact on parallel applications that are gang-scheduled or support process control. We explore the use of migration and replication of data to improve the data locality of applications. The results from our work are:

- We design a generalized policy framework for page migration and replication based on a carefully analysis of the data-locality problem in terms of costs and benefits. The policy framework incorporates features to maximize benefit and minimize cost because data locality for CC-NUMA multiprocessors is only an optimization and is not needed for correctness.

- In order to maximize benefits, only the pages taking the most cache misses should be considered as candidates for migration and replication. This is a key addition to earlier policies developed for non-cache-coherent shared memory machines. To find the pages taking the most cache misses we recommend counting cache misses in the memory controller. Our analysis shows that counting TLB misses, a potential software-only scheme, is not reliable because the correlation between TLB misses and cache misses is not consistent for all applications. We also find that sampling of cache misses can be used to reduce the cost of cache-miss counting without compromising information quality.

- We implement page replication and migration in the IRIX5.3 kernel from Silicon Graphics. Needed kernel changes fall into two categories, new functionality and performance optimizations. New functionality not found in current kernels includes support for tracking replicas of pages, efficient back mappings from physical pages to page table entries, and implementation of the policy. Performance optimizations include finer-grain synchronization in the VM system, reducing the cost of taking interrupts, and reducing the cost of TLB flushing. TLB flushing turns out to be the cause of significant kernel overhead.

- Our policy and implementation of migration and replication is able to greatly improve the locality of application cache misses; from almost random to greater than 80% in some cases. This greatly improved memory locality and low kernel overheads result in improved applica-

tion performance, reducing the execution time as much as 50% in some workloads. The implementation is also robust, and does not reduce the performance for applications where the access patterns preclude improvement of data locality.

- Another benefit that is not immediately obvious, but equally important, is the system-wide benefit from the reduction in utilization of memory system components, such as the memory controller and the network, because of the improvement in locality. This results in a reduction in network queue lengths, reduction in controller occupancy, and a significant reduction in the observed latency of local misses, as much as 30% in our experiments.

- From exploring the policy space of possible solutions for data locality and the parameters in our policy, we find that dynamic policies are able to outperform even the best off-line static policy. Both migration and replication are required to get the total benefit in all cases, and each by itself is not sufficient. The trigger threshold, which decides how aggressive the policy should be in selecting busy pages, is the important parameter and is dependent on the ratio of local and remote misses and the cost of migrating or replicating a page.

#### **1.6** Organization of the Thesis

The organization of the remainder of this thesis is as follows. In chapter 2 we analyze the reasons for the lack of isolation in current shared-memory multiprocessors. We propose Performance Isolation, a new method for resource management to solve this problem. We then develop a general framework for implementing the performance isolation model and describe the details of our implementation for CPU time, memory and disk bandwidth in the IRIX5.3 kernel from Silicon Graphics.

In chapter 3 we describe the SimOS simulation environment that we use to perform our experimental runs, and discuss the factors that prompted us to use a simulation system for our experiments. We also describe the target machine architecture which forms the basis of our experiments, and justify the choice of the SGI IRIX 5.3 operating system that forms the basis for implementing our various schemes.

In chapter 4 we present the experimental results from running workloads using our implementation of the performance isolation model. These results are compared with results using an unmodified SMP operating system and with a version that uses fixed quotas to provide isolation. Different workloads are used to highlight the effectiveness of performance isolation for each of the resource types, CPU time, memory, and disk bandwidth.

In chapter 5 we discuss the data-locality problem, and provide a general policy framework for implementing automatic migration and replication of data. We then describe the details of the kernel implementation of the policy, and discuss the mechanisms for counting cache misses to drive the policy.

In chapter 6 we present the experimental results of running workloads with the automatic migration and replication of data, and show the benefits possible by comparing it to that of the base operating system without this functionality. We carefully analyze and describe the overheads introduced in the implementation. Finally we discuss a number of issues relating to possible policy variations.

Chapter 7 surveys related work in both the data locality and performance isolation areas, and chapter 8 presents our conclusions.

## Chapter 2 Performance Isolation

Shared-memory multiprocessors are well suited to be compute servers for many reasons. As compute servers, these machines are often used in a shared environment by multiple users, by groups of users or by different simultaneous tasks. However, such systems are currently unable to isolate the performance of a process or a group of processes from changes in system load. Users have no reasonable guarantee of minimum performance for their applications even if they are using much less than the share of the resources they are entitled to on the system. One or more users or processes can easily load the system unfairly and tie up a large fraction of the resources, as was demonstrated in Figure 4. This behavior has generated the perception that shared-memory systems are inherently unable to isolate a user from interference, and has resulted in many detractors of these systems.

Our assertion is that this lack of isolation is not inherent to the fine-grain sharing provided by SMP operating systems on these machines, rather the observed degradation of performance is an artifact of the existing CPU-centric resource allocation method. This CPU-centric method might have been appropriate on workstations, where access to the CPU implied access to all resources on the system. Workstations usually have only a single user on the system who can control the number and type of active processes to achieve certain expectations of performance, albeit in an ad-hoc manner. Another potential shortcoming is that CPU allocation was done to maintain fairness on a per-process basis, but there were few controls for other resources that are also important

in determining application performance, such as memory and I/O bandwidth. Memory allocation was usually not done explicitly with static quotas per process at best, and allocation of I/O bandwidth was nonexistent. Current operating systems also have little support for controlling the allocation of resources to groups of processes, or for providing fairness by any abstraction other than individual processes.

This resource allocation method is not appropriate for modern multiprocessors (or even uniprocessor compute servers). On a multiprocessor, control of access to a single CPU gives little control over the other resources. Multiple processes are active at the same time on the system, and without appropriate controls any one of them can consume arbitrary levels of CPU, memory and I/O bandwidth. Resource management needs to be done to provide fairness to higher-level logical entities, such as individual users, a group of users, or a group of processes that comprise a task, not just between competing processes. In the absence of such criteria when allocating resources, we get the unwanted behavior seen on most current systems, where a user or task can get a larger share of the system by simply starting more processes.

A multiprocessor is often a shared resource with implicit or explicit contracts between users or tasks on how to share the machine. For example, all users have equal priority and expect equal performance, or project A owns a third of the machine and project B owns two thirds. Unlike the ad hoc control exerted by the single user on a workstation, such contracts would be very difficult to implement in the absence of explicit mechanisms and policies for resource management.

One method to implement such contracts is to enforce fixed quotas per user or task for the different resources. However, this method would not allow the sharing of idle resources, and significantly reduce the throughput and response time seen on these systems under light-load conditions. This thesis presents "**Performance Isolation**", a new resource management scheme for sharedmemory multiprocessors. This scheme isolates processes belonging to a logical entity, such as a user, from the resource requirements of others, and preserves the inherent sharing ability of these machines. Performance isolation seeks to take advantage of the tight coupling and flexibility of shared-memory machines to provide both workstation-like latency under heavy load and SMPlike latency under light load, and SMP-like throughput all the time, getting the best of both worlds. In Section 2.1 we elaborate on the performance isolation model, explaining the two facets to its implementation. The first is the metrics and mechanisms needed to provide isolation between groups of processes, and the second is the policies needed to enable careful sharing of resources between these groups. In Section 2.2 we discuss our implementation of this resource allocation model in the IRIX5.3 operating system from Silicon Graphics for CPU time, memory and I/O bandwidth resources. We also point out features of current SMP operating systems that make it difficult to provide isolation based on our experience with the implementation. In Chapter 4 we will present the results from running different workloads on our implementation of the performance isolation model.

#### 2.1 The Performance Isolation Model

The performance isolation model for shared-memory multiprocessors essentially partitions the computational resources of the multiprocessor into multiple flexible units based on a previously configured contract for sharing the machine. From a performance and resource allocation view-point the multiprocessor now looks like a collection of smaller machines. At the heart of the model is a new kernel abstraction called the *Software Performance Unit* (SPU), and each of these smaller machines is associated with an SPU. This is not a static permanent allocation of resources to SPUs as will become clear soon. SPUs can be created and destroyed dynamically, or could be suspended when it has no active processes and awakened at a later time.

The SPU abstraction has three parts:

- 1. The first is a criterion for assigning processes to an SPU. This decides which processes have access to the resources of the SPU. The performance of a process will be isolated from the resource requirements of any process that is not associated with its SPU. However, the SPU does not provide isolation between processes that are associated with the same SPU. The desired basis for the grouping of processes can vary greatly, and is dependent on the environment of the particular machine and the isolation goals. Some common possibilities are:

- Individual processes An SPU could be created for a web server.

- Groups of processes representing a task An SPU could be created for all the processes of a parallel database server or a parallel scientific application.

- Processes belonging to a user An SPU could be created for user foo and another for user bar.

- Processes belonging to a group of users Separate SPUs could be created for the OS, compiler, and hardware groups.

- 2. The second is the specification of the share of system resources assigned to the SPU. We are primarily interested in the computing resources that directly affect user performance: CPU time, memory, and I/O bandwidth (disk, network, etc.). However, it would be possible to incorporate other resources if required. There are many possible ways of partitioning resources between SPUs, such as:

- A fixed fraction of the machine An SPU gets half of all the hardware resources of the machine.

- A specified fraction of each resource Two CPUs, 128 Mbytes of memory, and half the bandwidth to all disks and the network.

- 3. The third is a sharing policy. Resources can be lent to other SPUs, and revoked when needed again by the loaning SPU. The sharing policy decides when and to whom resources belonging to an SPU will be allocated when these resources are idle. There are many possible types of sharing policies, and the following is a nonexhaustive list:

- Never give up any resources. This will approximate the case of each SPU being an entirely separate machine with its share of resources, or the machine being divided up with fixed quotas; there is no sharing.

- Share all resources with everyone all the time, without consideration for whether the resources are idle or not. This approximates the behavior of current SMP systems.

- A more interesting possibility is to share only idle resources with all or a subset of the SPUs that lack sufficient resources and could use the idle ones.

- Hierarchical sharing. There is a sharing tree of SPUs, with sharing happening at lower levels of the tree before the higher-levels.

- Priorities could be implemented through the sharing policy. For example SPU 1 is allocated all the resources on the system, and its sharing policy is to give SPUs 2 and 3 half of its idle resources each.

- There could be a temporal element to the sharing policy, i.e., giving up fractions of the idle resources after different intervals.

The sharing policy of the SPU abstraction, as described above, can be set to customize the behavior of the system as seen by the users. The performance isolation model, which we discuss in the rest of this thesis, will use the SPU abstraction with a specific sharing policy to achieve its goals. An SPU will share idle resources with any SPU that needs the idle resources. With this sharing policy, the performance isolation model should achieve the following two performance goals:

1. **Isolation**: If the resource requirements of an SPU are less than its allocated fraction of the machine, the SPU should see no degradation in performance, regardless of the load placed on the system by others.

Sharing: If the resource requirements of an SPU exceeds its configured share of resources, the SPU should be able to easily use any idle resources to improve its response time and throughput.

There are two parts to the solution for implementing the SPU abstraction for providing performance isolation, corresponding to the two goals presented above. First, we need to provide isolation between SPUs so that processes in an SPU cannot interfere with the performance of processes in another. This is done by implementing mechanisms in the kernel to count resource usage by SPU and restrict SPU resource usage to allocated limits. These mechanisms will guarantee that an SPU will be able to utilize all the resources it is entitled to even when the system is heavily loaded.

Second, we need to implement the chosen sharing policy for SPUs. To implement the sharing policy we need to detect idle resources, reallocate these idle resources to SPUs that may need them, and revoke the resources when they are needed again by the loaning SPU. This allows sharing of idle resources when the system is lightly loaded, providing for better throughput and response time.

#### 2.1.1 Providing Isolation

In order to provide isolation between SPUs two new aspects of functionality were needed in the kernel not provided by current SMP systems. First, the utilization of resources by individual SPUs needed to be tracked. For example, every time a memory page is allocated, the kernel needs to know which SPU is getting the page and increment its page usage counter. Second, mechanisms are needed to limit the usage of resources by an SPU to allocated levels. For example, currently in the SGI IRIX operating system a request for a page of memory will fail only if there is no free memory in the system. For isolation a page request from a process may need to be denied if the SPU that owns the process has used its allocation of pages, even if there is still memory available in the system. Current SMP systems do not have the appropriate metrics to track short-term usage of all resources by processes or groups of processes, and cannot limit the usage of these resource by a specific process.

A particular problem area in providing isolation is accounting for resources that are actually shared by multiple SPUs, or that do not belong to any specific SPU. Examples of the former are pages of memory accessed simultaneously by multiple SPUs such as shared library pages or code, and delayed disk write requests that often contain dirty pages from multiple processes and multiple SPUs. Examples of the latter are kernel processes, such as the pager and swapper daemons and pages used by the kernel code and static data.

For this problem our current strategy has been to choose the simplest solutions that seem reasonable. More sophisticated solutions may easily be considered in the future, if we encounter instances where these proposed solutions clearly do not work. To address the above problem we introduce two default SPUs in the system: *kernel*, for kernel processes and memory; and *shared* for tracking resources used by multiple SPUs. The cost of memory pages that are referenced by multiple SPUs is counted in the shared SPU, and not explicitly allocated to any of the user SPUs. Memory pages other than those used by the kernel and shared SPUs are divided among user SPUs. Therefore, the cost of shared and kernel pages is effectively shared by all user SPUs. The cost of shared pages could be assigned more precisely if necessary, but this would incur a larger overhead. Shared disk writes get scheduled for service in the shared SPU. The cost of individual non-shared pages in these write requests is allocated to the appropriate user SPUs. The kernel SPU has unrestricted access to all resources.

#### 2.1.2 Policies for Sharing

The second part of the performance isolation model is the careful sharing of idle resources between SPUs, based on the sharing policy feature of the SPU abstraction. Conceptually, each SPU maintains three resource levels to implement resource sharing. The first level is the amount of resources that the SPU is **entitled** to initially. This level is decided by the division of system resources based on the sharing contract for the system. The second level is the amount of resources that the SPU is **allowed** to use currently. The third level is the amount of resources currently **used** by the SPU.

Sharing is implemented by changing the allowed level for SPUs based on resource requirements and availability. In a system under load where all SPUs are utilizing their share of the resources, all three levels will be at about the same value for the SPUs. The used level will be equal to the entitled, indicating full utilization. The allowed level will be equal to the entitled because there are no idle resources to share. At some point in time the situation may change, one or more SPUs may go idle or be under utilized, and some other SPUs may be heavily loaded. For the under utilized SPUs, their used level will now be much less than their entitled level, indicating idle resources. The sharing policy can now transfer some of these idle resources from the under-utilized SPUs to the others by increasing the value of the allowed level for the latter. In the presence of sharing, the allowed level will be greater than the entitled level for the heavily-loaded SPUs. The situation may change again at a later point in time when the utilization of formerly idle SPUs increases, and they need their resources again. The sharing policy will now revoke resources from SPUs that had borrowed them by lowering their allowed level, potentially to the entitled level.

The isolation of performance of an SPU can be adversely affected if the sharing policy is not careful when transferring idle resources. Transferring all idle resources from underloaded SPUs to overloaded SPUs would result in the best system throughput. However, the resources that are currently idle in an SPU may be needed in the future. The base performance of an SPU will be adversely affected if the resources that are loaned are unavailable when they are needed.

The key factor in making the decision to transfer resources is the **revocation cost** for these resources when they are needed again by the loaning SPU. If the revocation cost were zero, then transferring all the resources would not be a problem as they could be instantly revoked when needed. However, most resources have a non-trivial revocation cost, and this cost plays a part in deciding when resources are transferred and how much of the idle resources are transferred. When making sharing decisions, the policy module needs to ensure that the cost of revocation does not adversely affect the performance of the loaning SPU and break isolation. The revocation cost and the details of sharing are explained for each resource in Section 2.2 below.

## 2.2 Kernel Implementation

In the previous section we discussed a framework for implementing performance isolation in terms of providing isolation and sharing between SPUs. We now describe the details of our implementation of the performance isolation in the IRIX5.3 kernel from Silicon Graphics. Most of the ideas in this implementation are not specific to IRIX, and would apply to other operating systems

| Name    | Unit of<br>allocation   | SPU metrics<br>tracked                                             | Isolation Mechanism                                                                                    | Sharing Policy                                                                                             |

|---------|-------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| CPU     | Time in<br>milliseconds | CPUs entitled<br>CPUs idle<br>CPUs loaned                          | SPU ID of process and<br>CPU must match while<br>scheduling                                            | SPU ID ignored if CPU is idle                                                                              |

| Memory  | Page<br>(4K)            | <i>entitled</i> count<br><i>allowed</i> count<br><i>used</i> count | Page granted only if<br><i>used</i> count < <i>allowed</i><br>count for SPU.                           | Increase <i>allowed</i> for SPU with<br>memory pressure if <i>total idle</i> ><br><i>Reserve Threshold</i> |

| Disk BW | Sectors per<br>second   | Per disk: Sectors<br>transferred &<br>Pending requests             | SPU skipped if <i>trans-</i><br><i>ferred</i> > (share of band-<br>width + BW difference<br>threshold) | Head-position scheduling of<br>pending requests unless SPU is<br>to be skipped                             |

need to be kept per SPU, the mechanism to isolate the performance of an SPU and the basic sharing policy.