## **Checking Experiments For Scan Chain Latches and Flip-Flops**

Samy Makar

| Gates Room # 235, MC 9020<br>Gates Building 2A<br>Computer Systems Laboratory(CSL TR # =<br>July 1996=July 1996=Gates Room # 235, MC 9020<br>Gates Building 2A<br>Computer Systems Laboratory<br>Departments of Electrical Engineering and Computer Science<br>Stanford University<br>Stanford, California 94305 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### Abstract:

This technical report contains the text of Samy Makar's thesis "Checking Experiments for Scan Chain Latches and Flip-Flops".

### **Funding:**

This work was supported in part by the Ballistic Missile Defense Organization, Innovative Science and Technology (BMDO/IST) Directorate and administered through the Department of the Navy, Office of Naval Research under Grant No. N00014-92-J-1782, in part by the Advanced Research Projects Agency under Contract No. DABT63-94-C-0045, and in part by the National Science Foundation under Grant No. MIP-9107760. It was also funded in part by Cirrus Logic.

### ABSTRACT

New digital designs often include scan chains; high quality economical test is the reason. A scan chain allows easy access to internal combinational logic by converting bistable elements, latches and flip-flops, into a shift register. Test patterns are scanned in, applied to the internal circuitry, and the results are scanned out for comparison. While many techniques exist for testing the combinational circuitry, little attention has been paid to testing the bistable elements themselves. The bistable elements are typically tested by shifting in a sequence of zeroes and ones. This test can miss many defects inside the bistable elements. A checking experiment is a sequence of inputs and outputs that contains enough information to extract the functionality of the circuit. A new approach, based on such sequences, can significantly reduce the number of defects missed. Simulation results show that as many as 20 percent of the faults in bistable elements can be missed by typical tests; essentially all of these missed faults are detected by checking experiments. Since the checking experiment is a functional test, it is independent of the implementation of the bistable element. This is especially useful since designers often use different implementations of bistable elements to optimize their circuits for area and performance. Another benefit of a functional test is that it avoids the need for generating test patterns at the transistor level.

Applying a complete checking experiment to a bistable element embedded inside a circuit can be very difficult, if not impossible. The new approach breaks up the checking experiment into a set of small sub-sequences. For each of these sub-sequences a test pattern is generated. These test patterns are scanned in, as in the case of the tests for combinational logic, appropriate changes to the control inputs of the bistable elements are applied, and the results are scanned out. The process of generating the patterns is automated by modifying an existing stuck-at test generator. A designer or test engineer need only provide a gate level description of the circuit to generate tests that guarantee a checking experiment for each bistable element in the design.

Test size is an important economic factor in circuit design. The size of the checking-experiment-based test increases with circuit size at about the same rate as the traditional test, indicating that it is practical for large circuits. Checking-experiment-based tests are an effective economic means for testing the bistable elements in scan chain designs.

## ACKNOWLEDGMENT

I am deeply grateful to my advisor, Prof. Edward J. McCluskey, for his constant guidance, support, and encouragement throughout my years at Stanford. I would like to thank Prof. John Gill, my associate advisor, and Prof. Leonard Tyler, my committee chairman, for reading my dissertation, and Prof. Mike Flynn for agreeing to be the fourth member of my committee.

I would like to thank my colleagues at the Center for Reliable Computing for interesting discussions, helpful comments, and companionship through the years: Khader Abdel-Hafez, LaNae Avra, Jonathan Chang, Hong Hao, Rajesh Kamath, Erin Kan, Wern-Yan Koe, Sunil Kosalge, Siyad Ma, Samiha Mourad, Shridhar Mukund, Rob Norwood, Nirmal Saxena, Philip Shirvani, Alice Tokarnia, Nur Touba and Sanjay Wattal. I also thank Siegrid Munda for her administrative support.

I wish to thank other friends at Stanford for their support over the years: Edgar Holmann, Margaret Martonosi, Tony Todesco and Josep Torrelas. I would also like to thank all members of the Stanford Ballroom Dance Club for all the fun during my years at Stanford. Thanks also go to Judith Shimizu, for reading the many versions of this thesis, and other publications, and for preparing the wonderful food for my oral presentation, and to Sanjay Wattal for his valuable comments on reading this thesis. Special thanks also go to Suhas Patil, founder and chairman of Cirrus Logic Inc., for encouraging me to complete my degree after joining Cirrus Logic.

I am very grateful my parents for their continued support and encouragement during the pursuit of not just my PhD, but to all my education. I dedicate this thesis to them. I also thank my brother and sisters, Rosemary, Ramsey and Hoda, for their continuing encouragement and support.

This work was supported in part by the Ballistic Missile Defense Organization, Innovative Science and Technology (BMDO/IST) Directorate and administered through the Department of the Navy, Office of Naval Research under Grant No. N00014-92-J-1782, in part by the Advanced Research Projects Agency under Contract No. DABT63-94-C-0045, and in part by the National Science Foundation under Grant No. MIP-9107760. It was also funded in part by Cirrus Logic.

# **TABLE OF CONTENTS**

| Abstract                                                                                                               | 1                                                                                    |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Acknowledgment                                                                                                         | ii                                                                                   |

| List of Figures                                                                                                        | V                                                                                    |

| List of Tables                                                                                                         | X                                                                                    |

| Chapter 1. Introduction                                                                                                | 1                                                                                    |

| Chapter 2. Checking Experiments for Latches                                                                            | 11                                                                                   |

| 2.1 Latches and Their Minimum-Length Checking Experiments                                                              | 11                                                                                   |

| 2.2 Deriving Checking Experiments for Two-State Latches                                                                | 14                                                                                   |

| 2.2.1 Two-State SR-Latch                                                                                               | 27                                                                                   |

| 2.2.2 Two-State D-Latch                                                                                                | 28                                                                                   |

| 2.2.3 Two-State MD-Latch                                                                                               | 29                                                                                   |

| 2.2.4 Two-State TP-Latch                                                                                               | 30                                                                                   |

| 2.3 Shift Register                                                                                                     | 32                                                                                   |

| 2.4 Latch Based Scan Chains                                                                                            | 38                                                                                   |

| 2.4.1 MD-Latch Based Scan Architecture                                                                                 | 38                                                                                   |

| 2.4.2 LSSD Architecture                                                                                                | 44                                                                                   |

| 2.5 Summary                                                                                                            | 50                                                                                   |

| Chapter 3. Checking Experiments for Flip-Flops                                                                         | 51                                                                                   |

|                                                                                                                        |                                                                                      |

| 3.1 Checking Experiments for Flip-Flops                                                                                |                                                                                      |

| 3.1 Checking Experiments for Flip-Flops<br>3.1.1 D Flip-Flop                                                           | 51                                                                                   |

|                                                                                                                        | 51<br>52                                                                             |

| 3.1.1 D Flip-Flop                                                                                                      | 51<br>52<br>54                                                                       |

| 3.1.1 D Flip-Flop<br>3.1.2 MD Flip-Flop                                                                                | 51<br>52<br>54<br>58                                                                 |

| 3.1.1 D Flip-Flop<br>3.1.2 MD Flip-Flop<br>3.1.3 TP Flip-Flop                                                          | 51<br>52<br>54<br>58<br>61                                                           |

| 3.1.1 D Flip-Flop<br>3.1.2 MD Flip-Flop<br>3.1.3 TP Flip-Flop<br>3.2 Shift Register                                    | 51<br>52<br>54<br>58<br>61<br>69                                                     |

| 3.1.1 D Flip-Flop<br>3.1.2 MD Flip-Flop<br>3.1.3 TP Flip-Flop<br>3.2 Shift Register<br>3.2.1 Primary Input/Output View | 51<br>52<br>54<br>58<br>61<br>69<br>71                                               |

| <ul> <li>3.1.1 D Flip-Flop</li></ul>                                                                                   | 51<br>52<br>54<br>58<br>61<br>69<br>71<br>72                                         |

| <ul> <li>3.1.1 D Flip-Flop</li></ul>                                                                                   | 51<br>52<br>54<br>58<br>61<br>69<br>71<br>72<br>72                                   |

| <ul> <li>3.1.1 D Flip-Flop</li></ul>                                                                                   | 51<br>52<br>54<br>58<br>61<br>69<br>71<br>72<br>72<br>72<br>88                       |

| <ul> <li>3.1.1 D Flip-Flop</li></ul>                                                                                   | 51<br>52<br>54<br>58<br>61<br>69<br>71<br>72<br>72<br>88<br>99                       |

| <ul> <li>3.1.1 D Flip-Flop</li></ul>                                                                                   | 51<br>52<br>54<br>58<br>61<br>69<br>71<br>72<br>72<br>88<br>99<br><b> 100</b>        |

| <ul> <li>3.1.1 D Flip-Flop</li></ul>                                                                                   | 51<br>52<br>54<br>58<br>61<br>69<br>71<br>72<br>72<br>88<br>99<br><b> 100</b><br>100 |

| 4.2.2 Test Generation for TP-Latches in LSSD Architecture        | . 115 |

|------------------------------------------------------------------|-------|

| 4.2.3 Test Generation for MD Flip-Flops in MD Flip-Flop          |       |

| Architecture                                                     | . 118 |

| 4.2.4 Test Generation for TP Flip-Flops in TP Flip-Flop          |       |

| Architecture                                                     | . 124 |

| 4.3 Summary                                                      | . 128 |

| Chapter 5. Fault Simulation                                      | . 129 |

| 5.1 Fault Simulation of D-Latch                                  | . 130 |

| 5.2 Fault Simulation of MD-Latch                                 | . 135 |

| 5.3 Fault Simulation of D Flip-Flop                              | . 137 |

| 5.4 Fault Simulation of MD Flip-Flop                             | . 142 |

| 5.5 Summary                                                      | . 145 |

| Chapter 6. ATPG Results                                          | . 146 |

| Chapter 7. Concluding Remarks                                    | . 151 |

| Appendix A. Using Checking Experiments To Test Two-State Latches | . 153 |

| Appendix B. Deriving Checking Experiment for Flip-Flops          | . 199 |

| Appendix C. Fault Analysis                                       | . 206 |

| References                                                       | . 225 |

# LIST OF FIGURES

| Figure  | Title                                                              |    |

|---------|--------------------------------------------------------------------|----|

| 1-1     | Test Process                                                       | 1  |

| 1-2     | Example of Exhaustive and Pseudo-Exhaustive Test                   | 2  |

| 1-3     | Example of LFSR (Linear Feedback Shift Register)                   | 2  |

| 1-4     | Example of Test Generation Using Stuck-At Fault Model.             | 3  |

| 1-5     | Example of Test Generation for Circuit With Reconvergent Fanout    | 3  |

| 1-6     | Example of Test Generation for Sequential Circuits.                | 5  |

| 1-7     | Replicating Combinational Logic for Sequential Test Generation     | 5  |

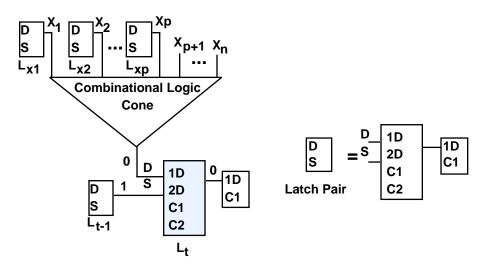

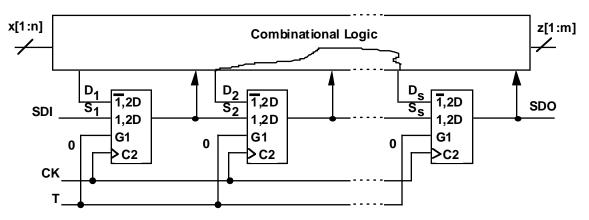

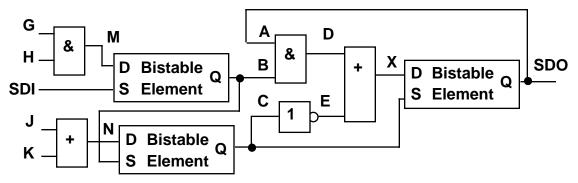

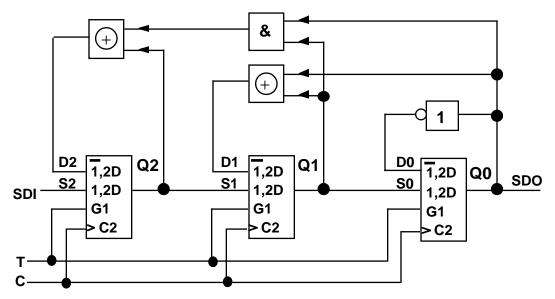

| 1-8     | MD-Latch Based Scan Architecture.                                  | 7  |

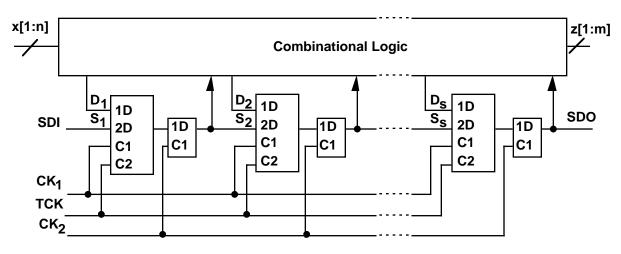

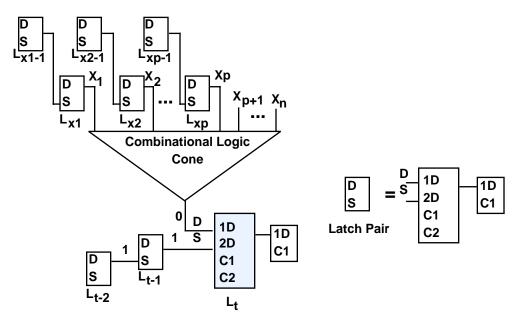

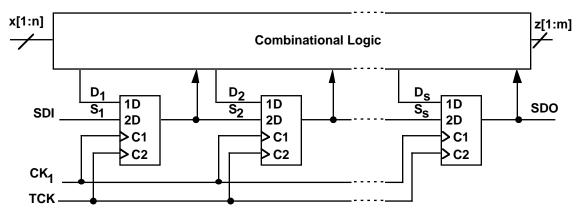

| 1-9     | Level Sensitive Scan Design (LSSD) Architecture.                   | 8  |

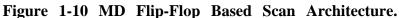

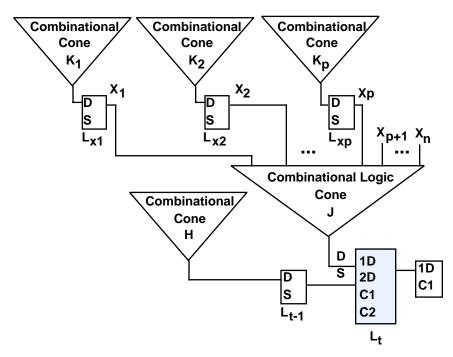

| 1-10    | MD Flip-Flop Based Scan Architecture.                              | 8  |

| 1-11    | TP Flip-Flop Based Scan Architecture.                              | 8  |

| 2.2-1   | Definitions in Flow Table.                                         | 15 |

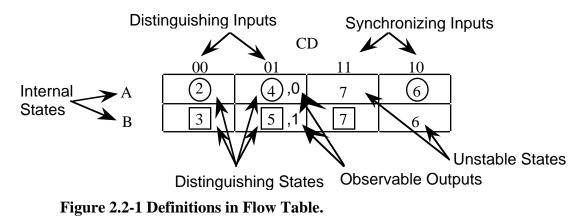

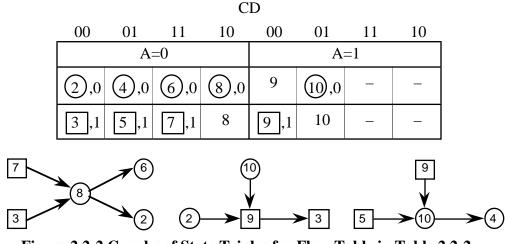

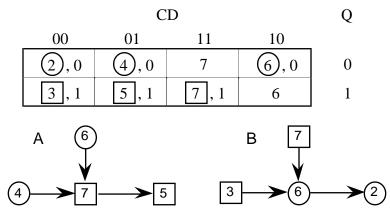

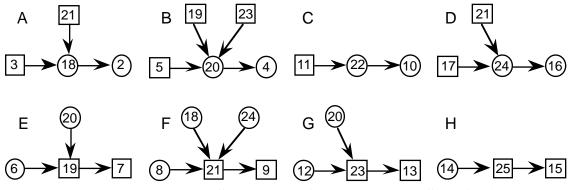

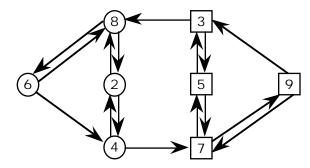

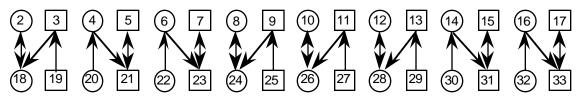

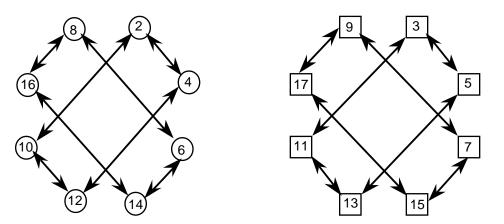

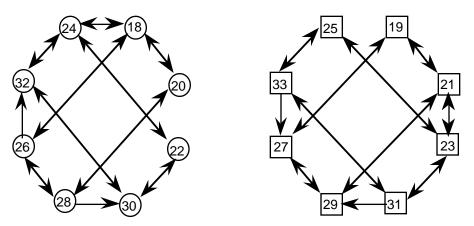

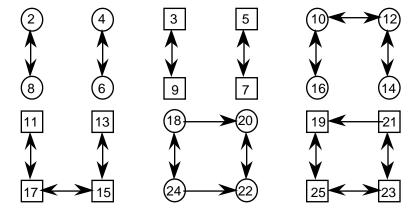

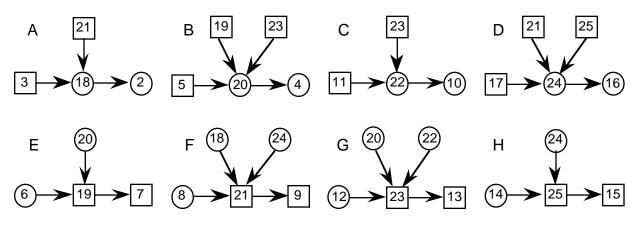

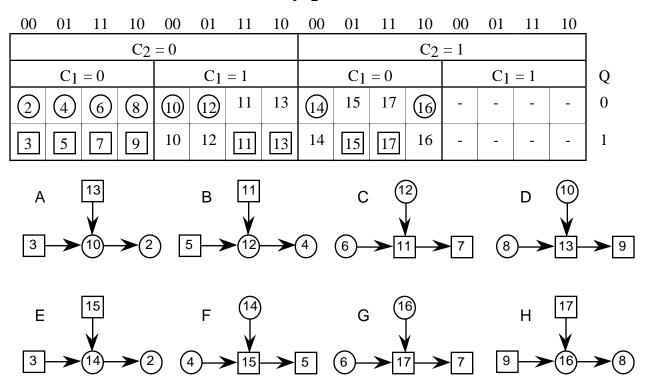

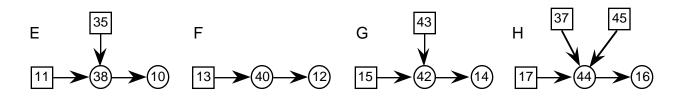

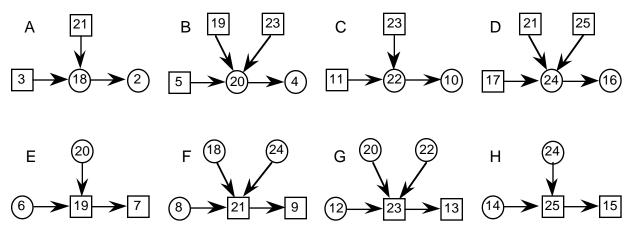

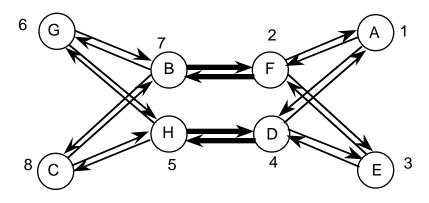

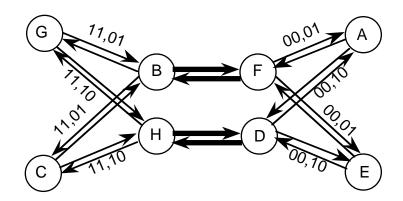

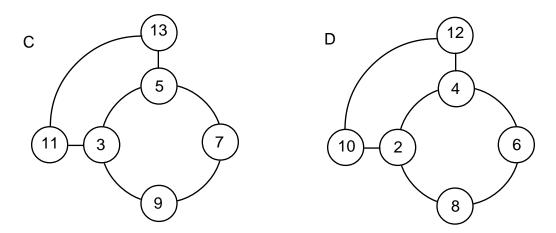

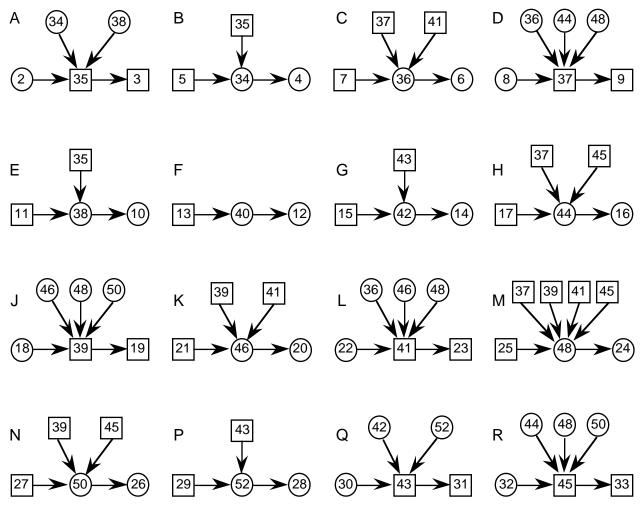

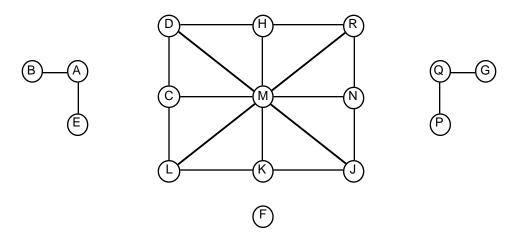

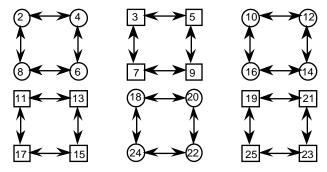

| 2.2-2   | Graphs of State Triples for Flow Table in Table 2.2-2              | 18 |

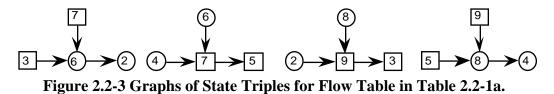

| 2.2-3   | Graphs of State Triples for Flow Table in Table 2.2-1a.            |    |

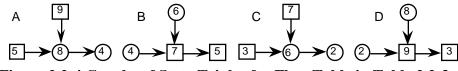

| 2.2-4   | Graphs of State Triples for Flow Table in Table 2.2-3a.            | 19 |

| 2.2-6   | Graph of State Triples for Flow Table in Table 2.2-5.              | 22 |

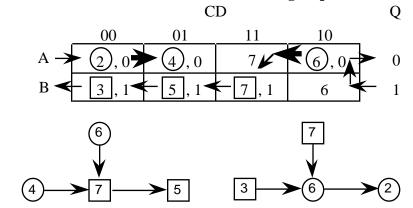

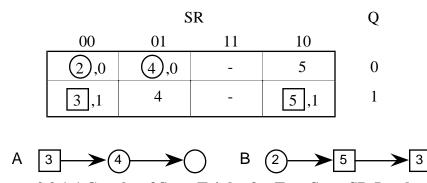

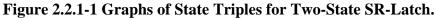

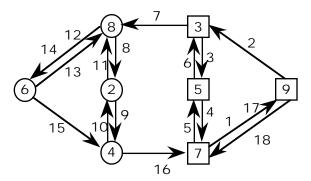

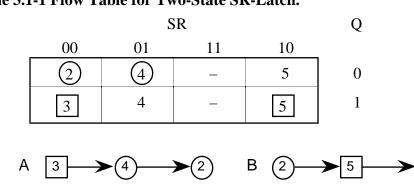

| 2.2.1-1 | Graphs of State Triples for Two-State SR-Latch.                    | 27 |

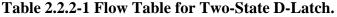

| 2.2.2-1 | Graphs of State Triples for Two-State D-Latch.                     |    |

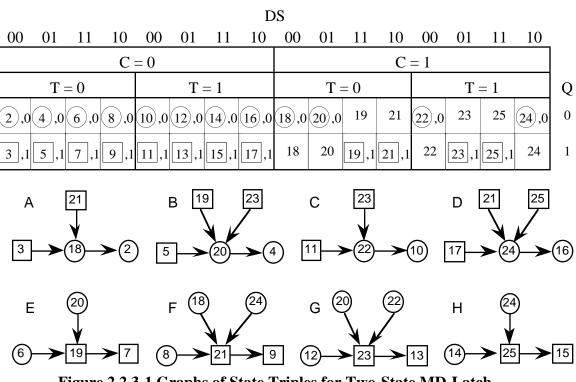

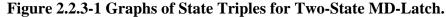

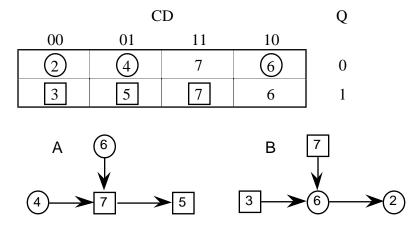

| 2.2.3-1 | Graphs of State Triples for Two-State MD-Latch.                    | 29 |

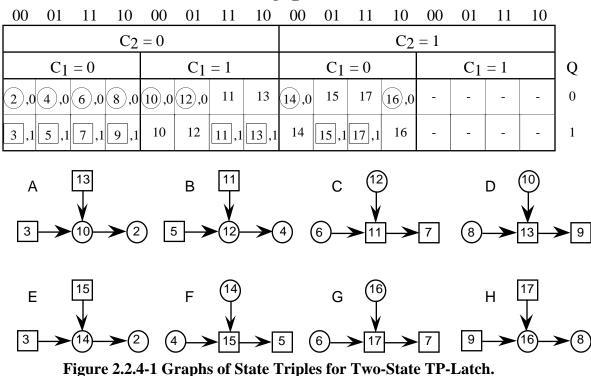

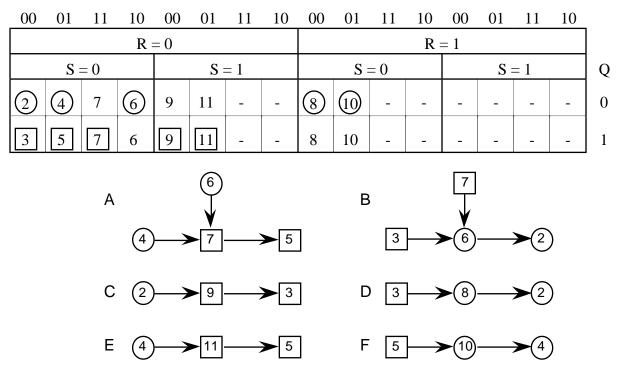

| 2.2.4-1 | Graphs of State Triples for Two-State TP-Latch                     | 30 |

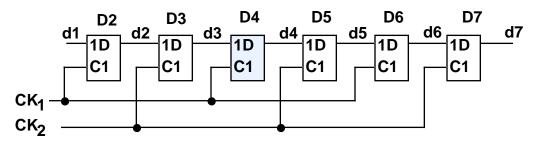

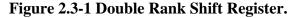

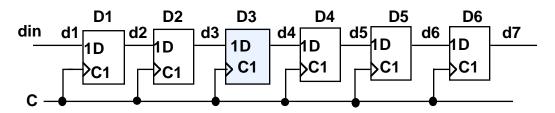

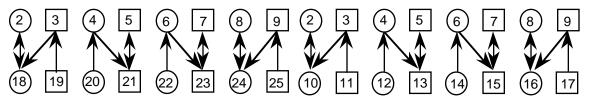

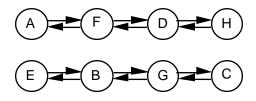

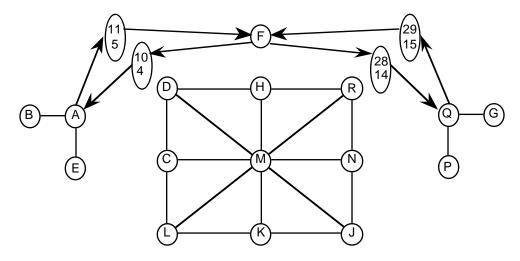

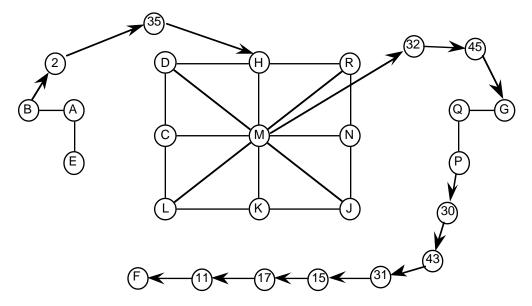

| 2.3-1   | Double Rank Shift Register.                                        | 32 |

| 2.3-2   | Restrictions in Shift Register Operation.                          | 33 |

| 2.3-3   | Reduced Graph of State Triples for D-Latch in Shift Register       | 33 |

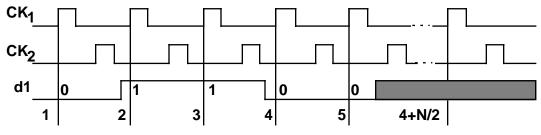

| 2.3-4   | Test for Shift Register Latches (N = Number of Latches)            | 37 |

| 2.4.1-1 | MD-Latch Based Scan Chain Architecture.                            | 38 |

| 2.4.1-2 | Reduced State Triples for MD-Latch in Scan Chain.                  | 39 |

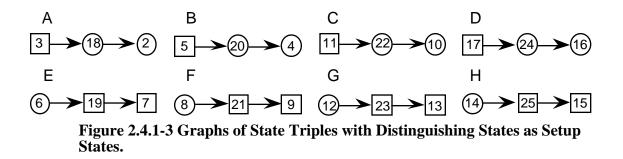

| 2.4.1-3 | Graphs of State Triples with Distinguishing States as Setup States | 40 |

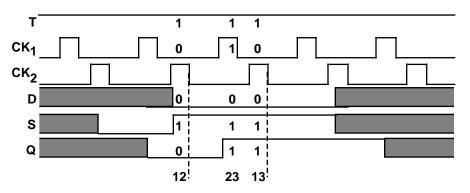

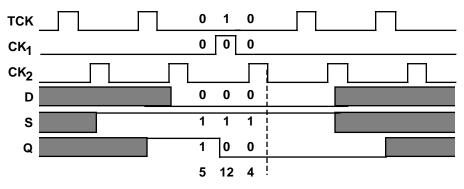

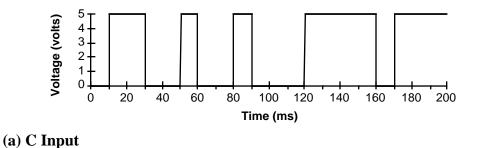

| 2.4.1-4 | Waveforms for Triple G of MD-Latch Under Test.                     | 40 |

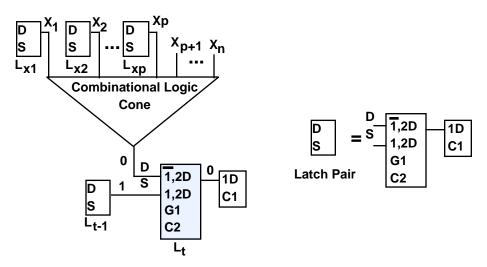

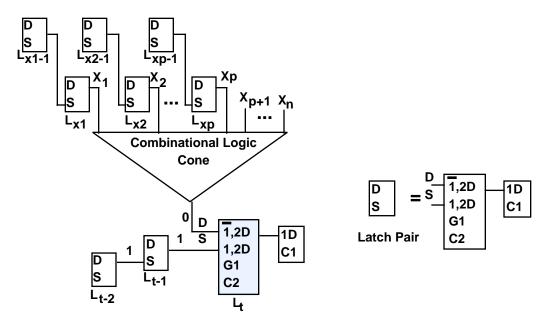

| 2.4.1-5 | Part of Circuit Involved in Testing Lt                             | 41 |

| 2.4.1-6 | Part of Circuit Involved With Distinguishing State for Lt.         | 42 |

| 2.4.1-7 | Circuit With Lt-1 Driving the Combinational Logic of D             | 42 |

| 2.4.1-8 | Waveforms for Triple E of MD-Latch Under Test                      | 43 |

| 2.4.1-9  | Part of Circuit Involved With Distinguishing State of Triple E for Lt. | . 43 |

|----------|------------------------------------------------------------------------|------|

| 2.4.1-10 | Waveforms for Capturing Output of Setup State of Triple E              | . 44 |

| 2.4.2-1  | LSSD Scan Chain Architecture.                                          | . 45 |

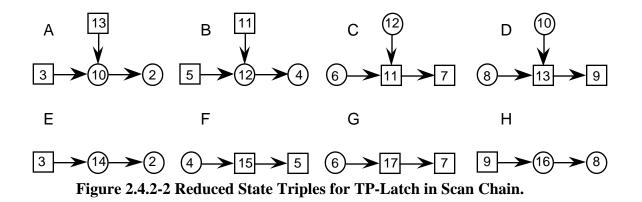

| 2.4.2-2  | Reduced State Triples for TP-Latch in Scan Chain                       | . 46 |

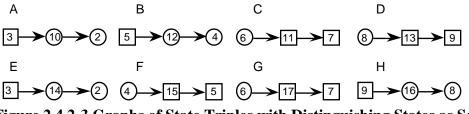

| 2.4.2-3  | Graphs of State Triples with Distinguishing States as Setup States     | . 46 |

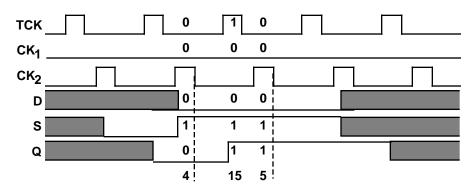

| 2.4.2-4  | Waveforms for Triple F of TP-Latch Under Test.                         | . 47 |

| 2.4.2-5  | Part of Circuit Involved in Testing Lt                                 | . 47 |

| 2.4.2-6  | Part of Circuit Involved With Distinguishing State for Lt.             | . 48 |

| 2.4.2-7  | Waveforms for Triple B of TP-Latch Under Test.                         | . 49 |

| 2.4.2-8  | Part of Circuit Involved With Distinguishing State of Triple B for Lt  | . 49 |

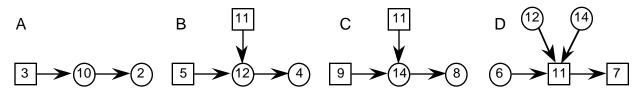

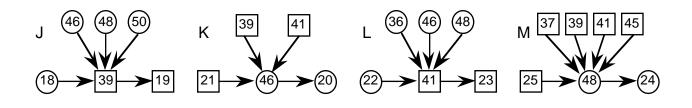

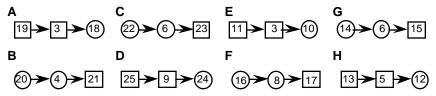

| 3.1.1-1  | Transition Graph From Table 3.1.1-1.                                   | . 53 |

| 3.1.1-2  | Sequence of Transitions in Table 3.1.1-2.                              | . 54 |

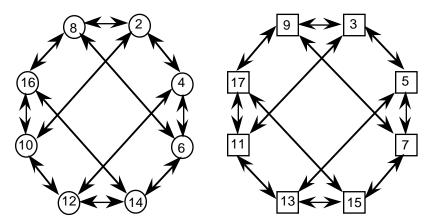

| 3.1.2-1  | Graphs of Transitions Within First Quadrant for MD Flip-Flop.          | . 55 |

| 3.1.2-2  | Graphs of Transitions Within Fourth Quadrant for MD Flip-Flop          | . 55 |

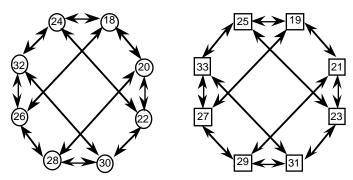

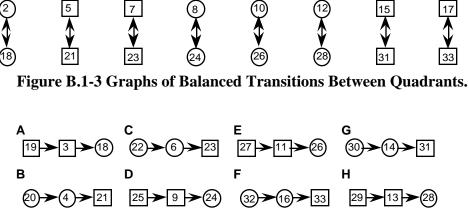

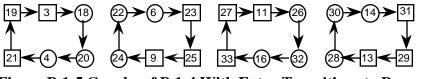

| 3.1.2-3  | Graphs of Transitions Between Quadrants for MD Flip-Flop               | . 57 |

| 3.1.3-1  | Graphs of Transitions Within Quadrants for TP Flip-Flop                | . 59 |

| 3.1.3-2  | Graphs of Transitions Between Quadrants for TP Flip-Flop               | . 60 |

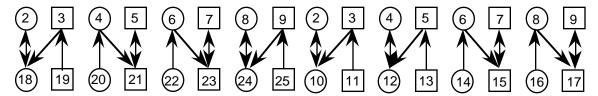

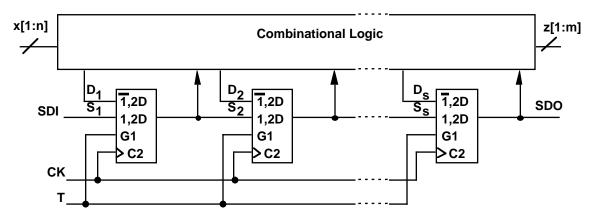

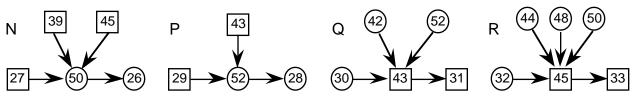

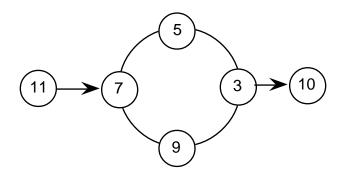

| 3.2-1    | Shift Register Constructed from D Flip-Flops                           | . 61 |

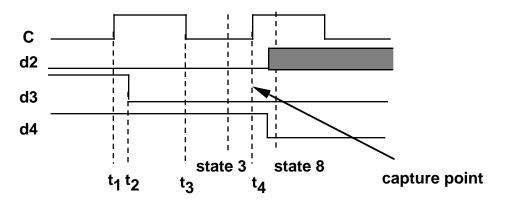

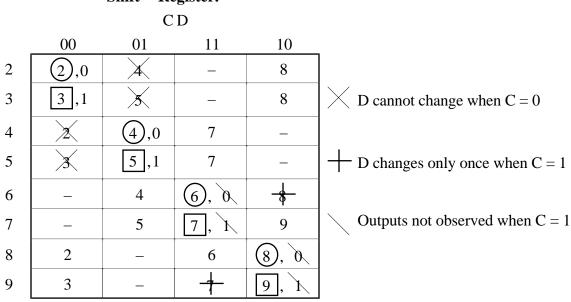

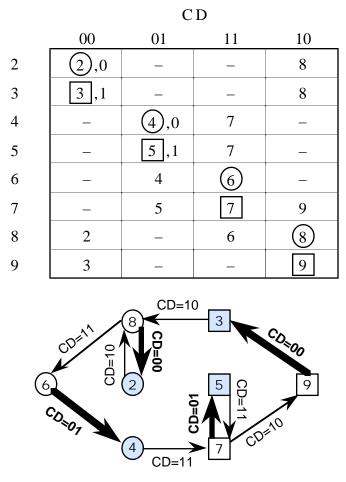

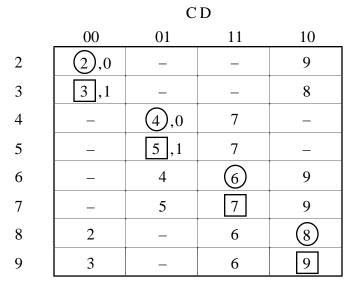

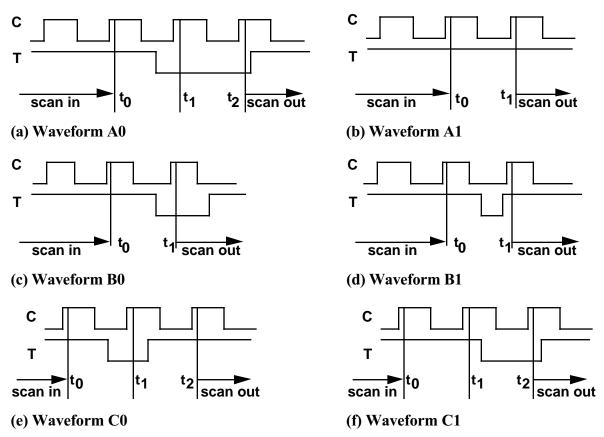

| 3.2-2    | Sequence of Operations in Cycle                                        | . 62 |

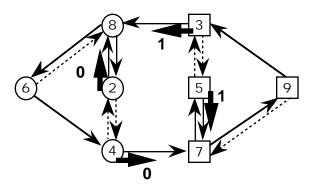

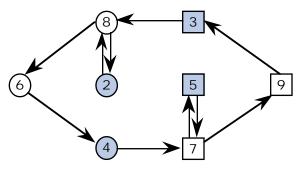

| 3.2-3    | Transition Graph for Internal Flip-Flop (Table 3.2-2) Showing          |      |

|          | Distinguishing Sequences.                                              | . 63 |

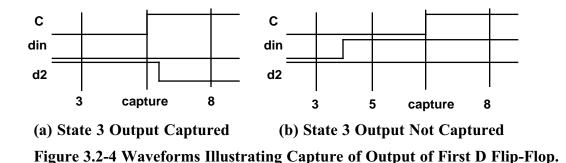

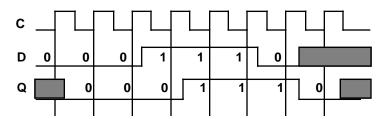

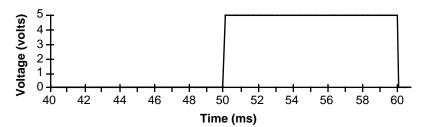

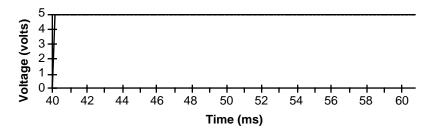

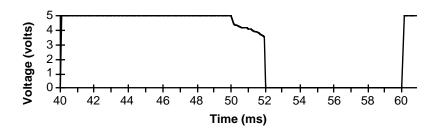

| 3.2-4    | Waveforms Illustrating Capture of Output of First D Flip-Flop          | . 67 |

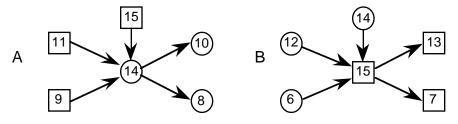

| 3.2-5a   | Transition Graph for the First D Flip-Flop of Shift Register           | . 68 |

| 3.2-5b   | Transition Graph for the Internal D Flip-Flop of Shift Register.       | . 68 |

| 3.2.1-1  | Waveforms of Checking Experiment in Table 3.2-3 for Flip-Flop in       |      |

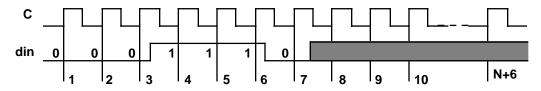

|          | Shift Register Showing Data Values                                     | . 70 |

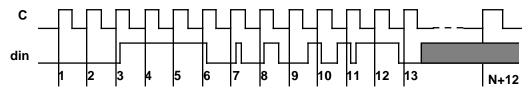

| 3.2.1-2  | Test for Shift Register Flip-Flops (N = Number of Flip-Flops).         | . 70 |

| 3.2.1-3  | Test for Shift Register Flip-Flops With No Constraints on C and din    | . 70 |

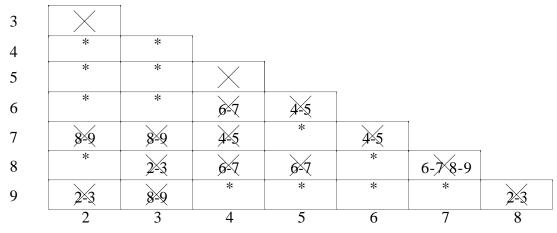

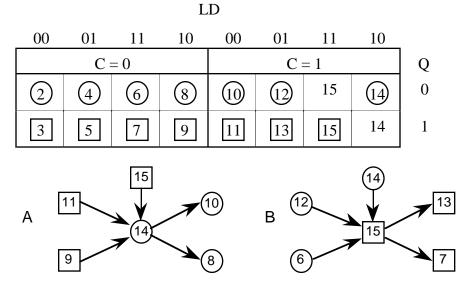

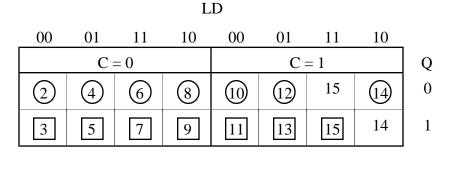

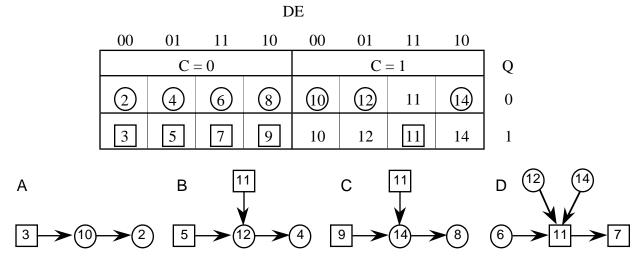

| 3.2.2-1  | Distinguishablity Array for D Flip-Flop Restricted Flow Table          | .71  |

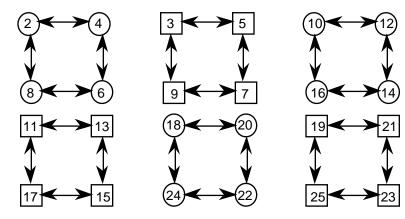

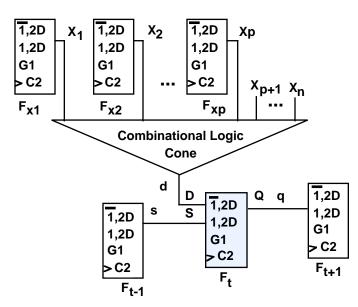

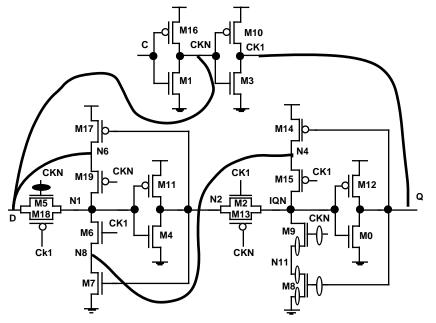

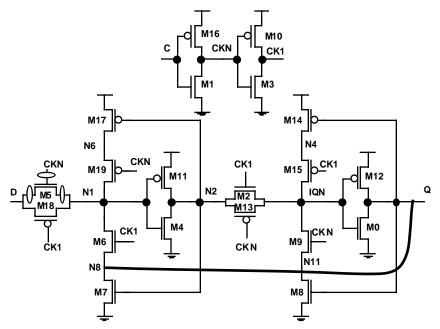

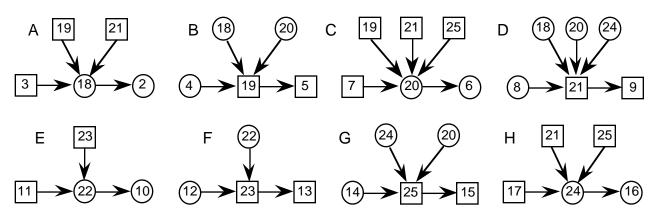

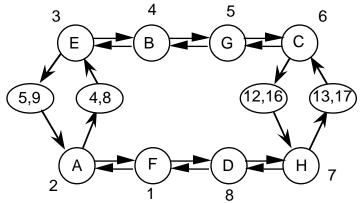

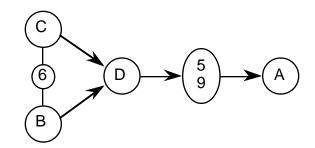

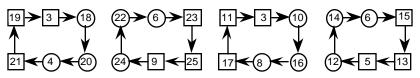

| 3.3.1-1  | MD Flip-Flop Based Scan Chain                                          | . 72 |

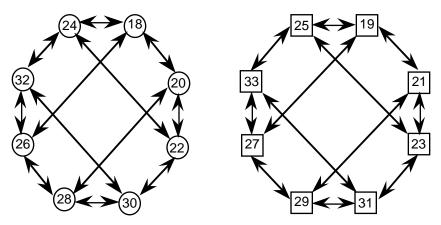

| 3.3.1-2  | Graphs of Transitions Within First Quadrant for Scan Chain MD Flip-    |      |

|          | Flop                                                                   | . 73 |

| 3.3.1-3  | Graphs of Transitions Within Fourth Quadrant for Scan Chain MD Flip-   |      |

|          | Flop                                                                   | . 76 |

| 3.3.1-4  | Graphs of Transitions Between Quadrants for Scan Chain MD Flip-        |      |

|          | Flop                                                                   | . 76 |

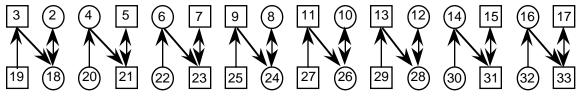

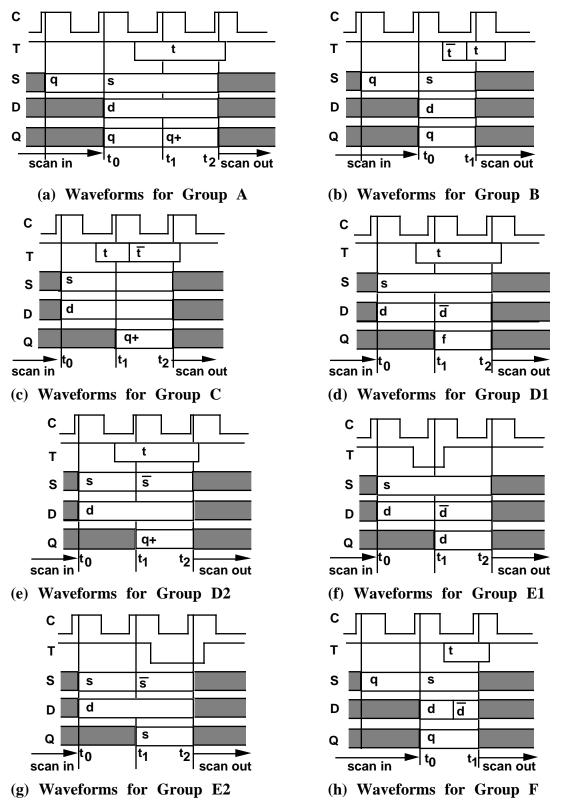

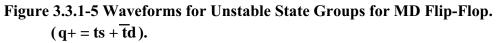

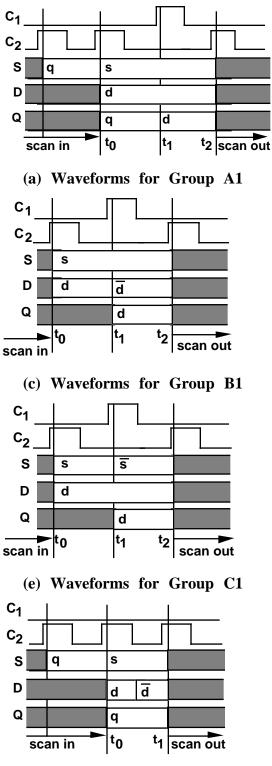

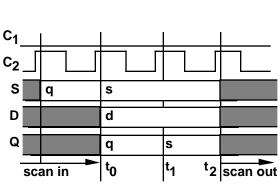

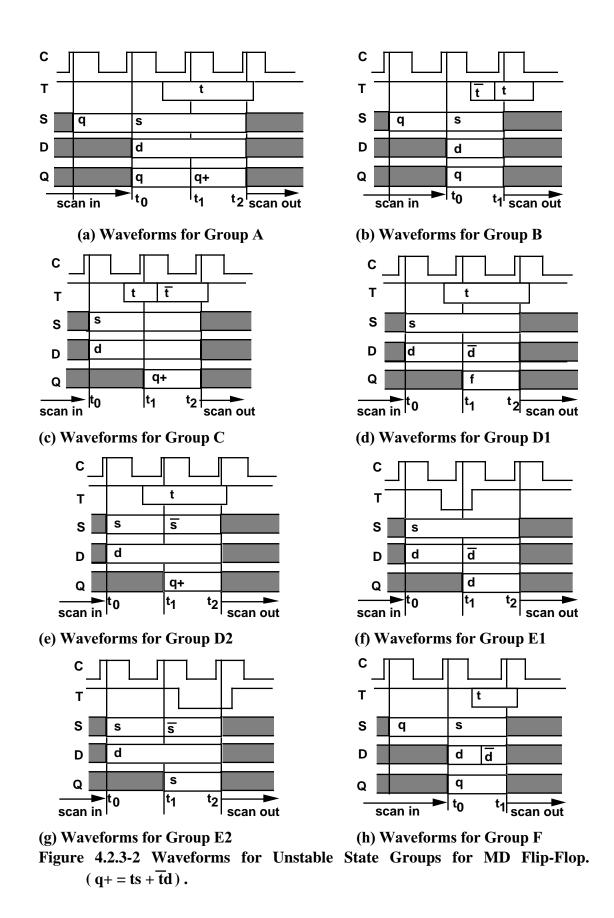

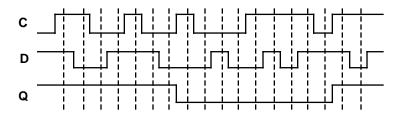

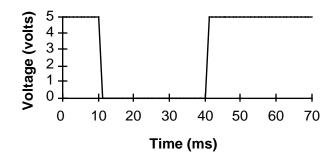

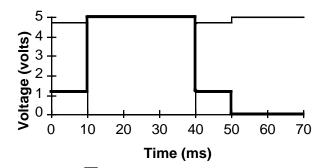

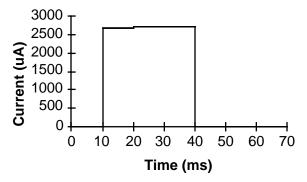

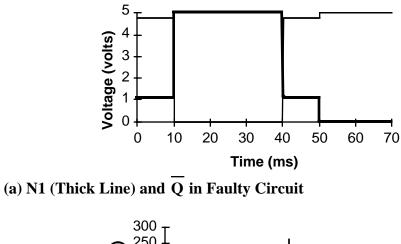

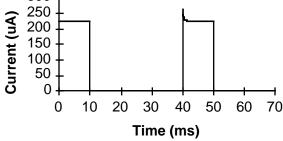

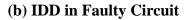

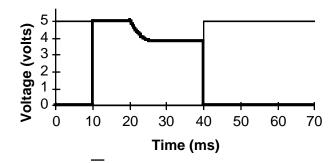

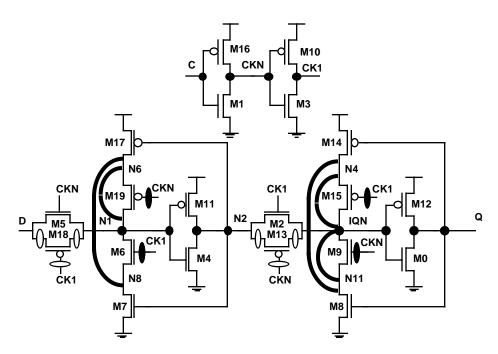

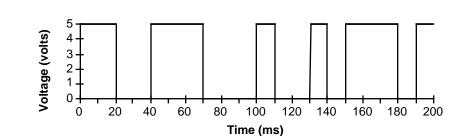

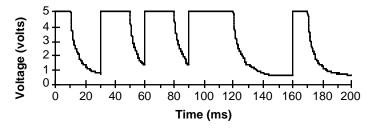

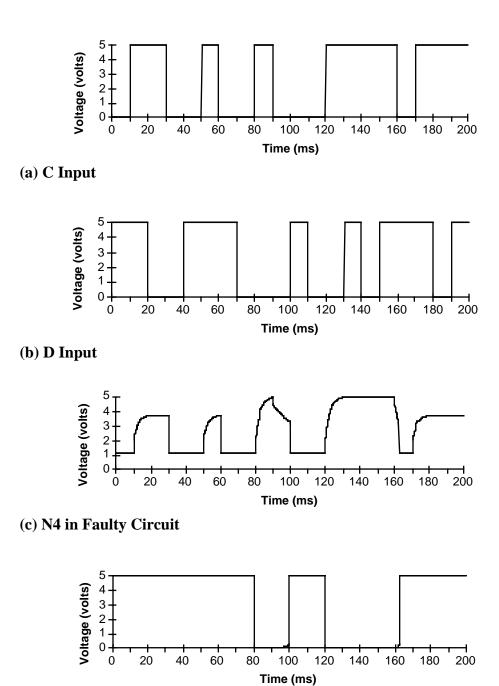

| 3.3.1-5  | Waveforms for Unstable State Groups for MD Flip-Flop                  | 82  |

|----------|-----------------------------------------------------------------------|-----|

| 3.3.1-6  | Part of Circuit Involved With Pattern Generation for Group B          | 83  |

| 3.3.1-7  | Part of Circuit Involved With Two-Cycle Pattern Generation $(T = 1)$  | 84  |

| 3.3.1-8  | Circuit With Ft-1 Driving the Combinational Logic of D.               | 85  |

| 3.3.1-9  | Part of Circuit Involved With Two-Cycle Pattern Generation $(T = 0)$  | 86  |

| 3.3.1-10 | Multiple Test Mode Signals to Capture Flip-Flop Output                | 87  |

| 3.3.1-11 | Path Sensitization to Capture Flip-Flop Output                        | 87  |

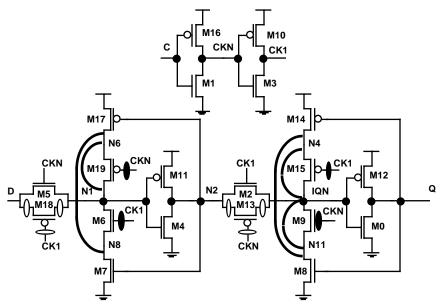

| 3.3.2-1  | TP Flip-Flop Based Scan Chain.                                        | 88  |

| 3.3.2-2  | Graphs of Transitions Within Quadrants for Scan Chain TP Flip-Flop    | 89  |

| 3.3.2-3  | Graphs of Transitions Between Quadrants for Scan Chain TP Flip-       |     |

|          | Flop                                                                  | 89  |

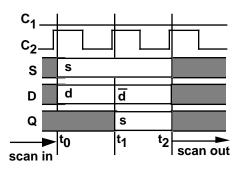

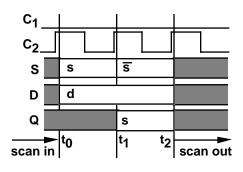

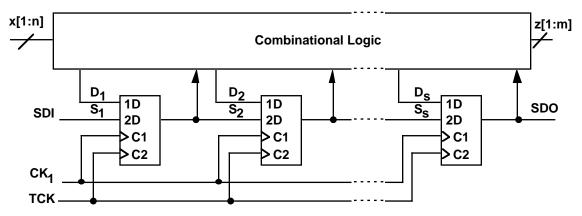

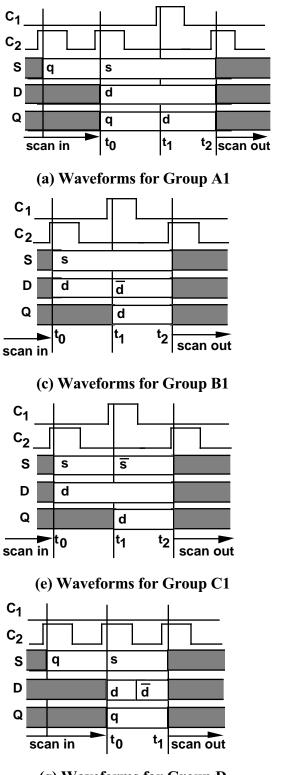

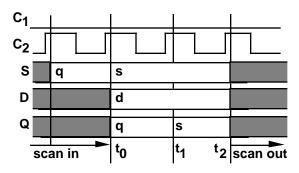

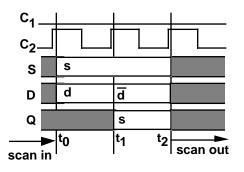

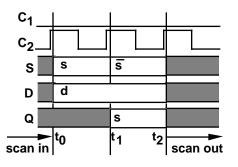

| 3.3.2-4  | Waveforms for Unstable State Groups for TP Flip-Flop                  | 96  |

| 3.3.2-5  | Part of Circuit Involved With Pattern Generation for Waveform With    |     |

|          | No C1 Pulse.                                                          | 97  |

| 3.3.2-6  | Part of Circuit Involved With Pattern Generation for Waveform With    |     |

|          | C1 Pulse.                                                             | 98  |

| 4.1-1    | Circuit to Describe Formula Extraction.                               | 102 |

| 4.1-2    | Circuit to Describe Pattern Generation for Single Cycle               | 103 |

| 4.1-3    | Circuit to Describe Pattern Generation for Shift and Normal Operation | 104 |

| 4.1-5    | Circuit to Describe Single Cycle Changing.                            | 108 |

| 4.2.1-1  | MD-Latch Scan Architecture                                            | 111 |

| 4.2.1-2  | Procedure GenPatsMDLatch() Generates Patterns for a Scan Chain        |     |

|          | MD-Latch.                                                             | 112 |

| 4.2.1-3  | Procedure TestMDL() Generates Patterns for All MD-Latches             | 113 |

| 4.2.1-4  | Waveforms for Applying Test Patterns for MD-Latch Scan Chain.         | 114 |

| 4.2.2-1  | LSSD Architecture.                                                    | 115 |

| 4.2.2-2  | Procedure GenPatsTPLatch() Generates Patterns for a Scan Chain TP-    |     |

|          | Latch                                                                 | 116 |

| 4.2.2-3  | Procedure TestTPL() Generates Patterns for All TP-Latches in Scan     |     |

|          | Chain                                                                 | 116 |

| 4.2.2-4  | Waveforms for Applying Test Patterns for LSSD Scan Chain.             | 117 |

| 4.2.3-1  | MD Flip-Flop Based Scan Architecture.                                 | 118 |

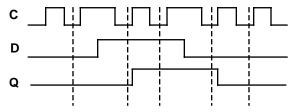

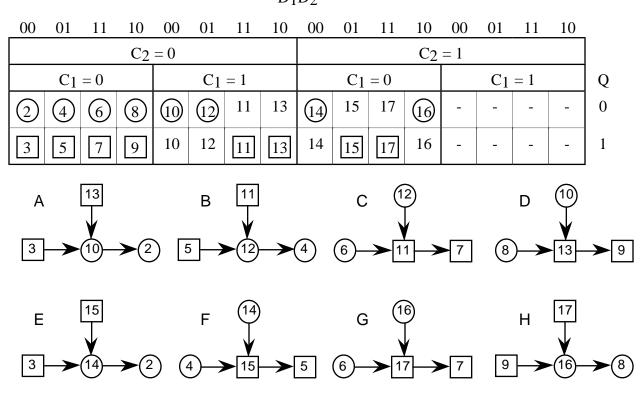

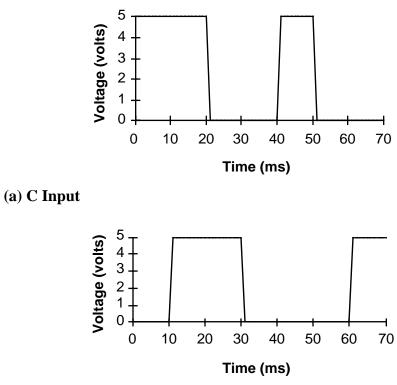

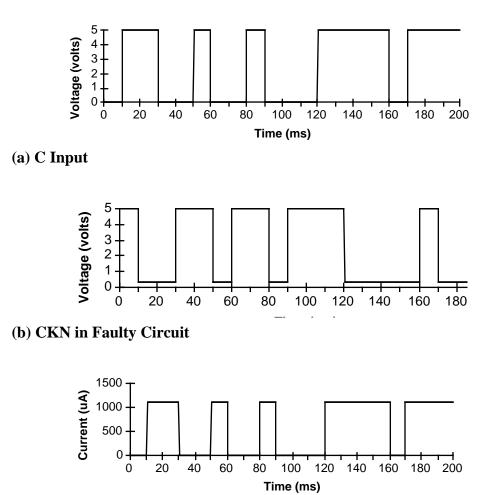

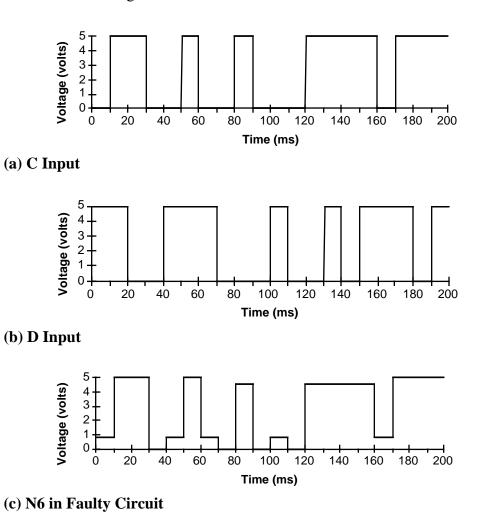

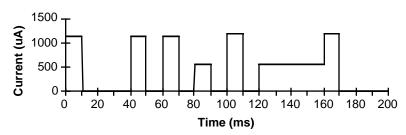

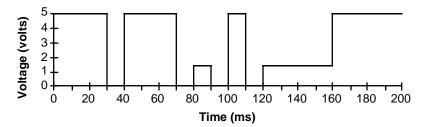

| 4.2.3-2  | Waveforms for Unstable State Groups for MD Flip-Flop                  | 119 |

| 4.2.3-3  | Part of Procedure GenPatsMDFF() Generates Patterns for a Scan Chain   |     |

|          | MD Flip-Flop.                                                         | 121 |

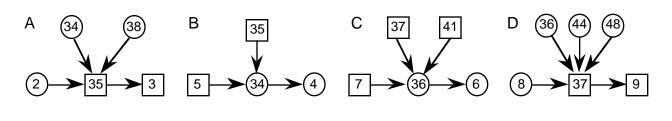

| 4.2.3-4 | Procedure TestMDFF() Generates Patterns for All MD Flip-Flops in      |     |

|---------|-----------------------------------------------------------------------|-----|

|         | Scan Chain                                                            | 122 |

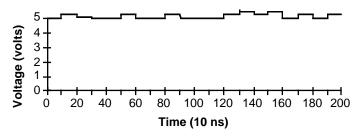

| 4.2.3-5 | Waveforms for Applying Test Patterns for MD Flip-Flop Scan Chain      | 123 |

| 4.2.4-1 | TP Flip-Flop Based Scan Architecture.                                 | 124 |

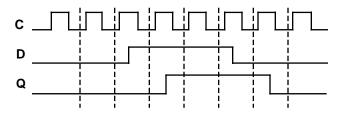

| 4.2.4-2 | Waveforms for Unstable State Groups for TP Flip-Flop                  | 125 |

| 4.2.3-3 | Part of Procedure GenPatsTPFF() Generates Patterns for a Scan Chain   |     |

|         | TP Flip-Flop                                                          | 126 |

| 4.2.3-4 | Procedure TestTPFF() Generates Patterns for All TP Flip-Flops in Scan |     |

|         | Chain                                                                 | 127 |

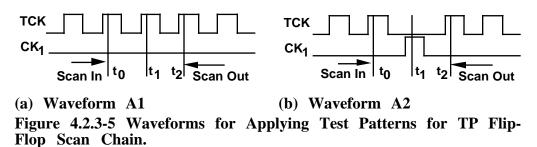

| 4.2.3-5 | Waveforms for Applying Test Patterns for TP Flip-Flop Scan Chain      | 127 |

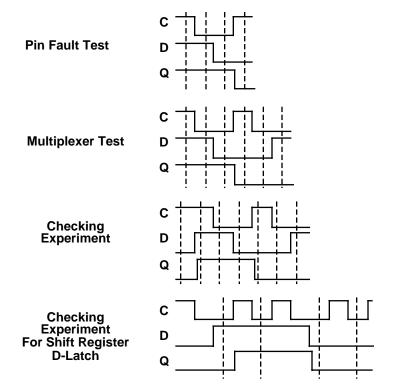

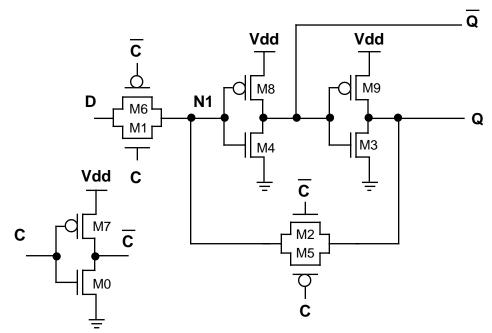

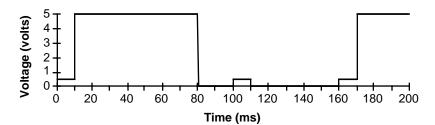

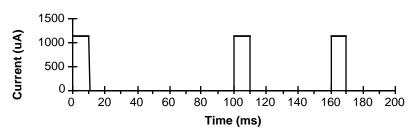

| 5.1-1   | Tests Applied to D-Latch (Dashed Lines Indicate When Output           |     |

|         | Checked).                                                             | 130 |

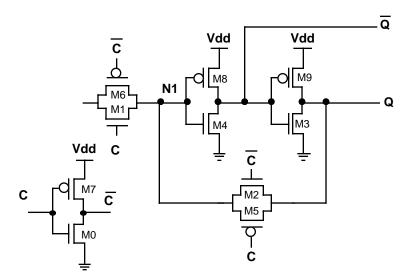

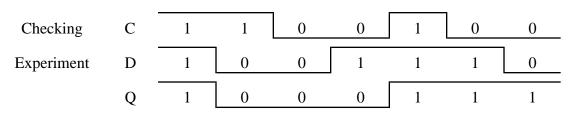

| 5.1-2   | Transmission Gate D-Latch.                                            | 131 |

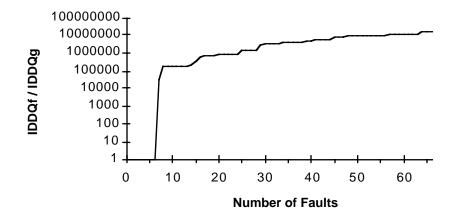

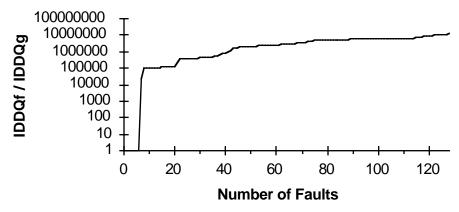

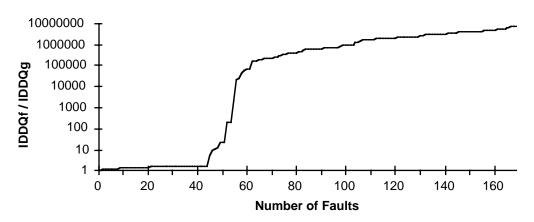

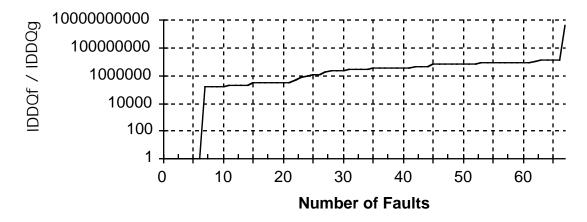

| 5.1-3   | Current Distribution Graph for D-Latch (IDDQg = 320 pA).              | 131 |

| 5.1-4   | Faults Missed by Checking Experiment for D-Latch in Shift Register    | 132 |

| 5.1-5   | Faults Missed by Checking Experiment for D-Latch.                     | 133 |

| 5.1-6   | Faults Missed by Multiplexer Test for D-Latch.                        | 133 |

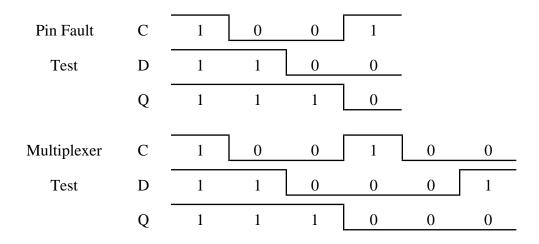

| 5.1-7   | Faults Missed by Pin Fault Test for D-Latch                           | 133 |

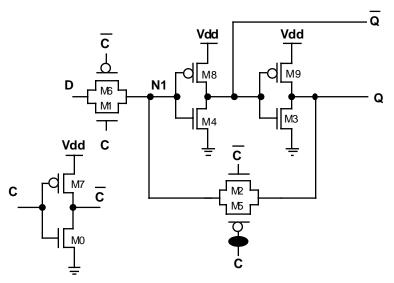

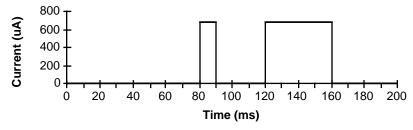

| 5.1-8   | Faults Detected by IDDQ Test Missed by Boolean Test                   | 134 |

| 5.2-1   | Traditional Test for MD-Latch in Scan Chain                           | 135 |

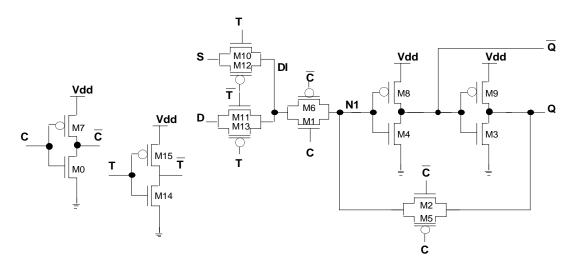

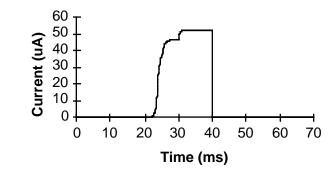

| 5.2-2   | MD-Latch Implementation.                                              | 135 |

| 5.2-3   | Current Distribution Graph for MD-Latch (IDDQg = 487 pA)              | 136 |

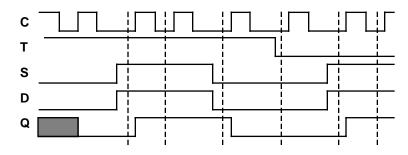

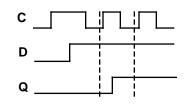

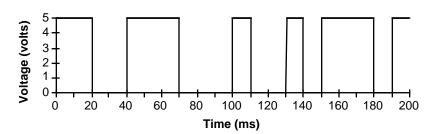

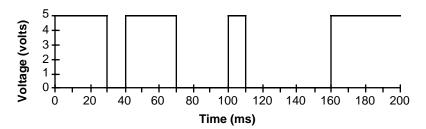

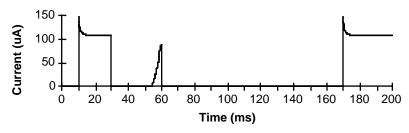

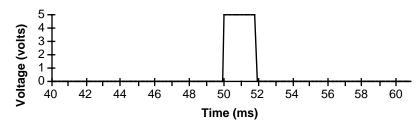

| 5.3-1   | Tests Applied to D Flip-Flop                                          | 137 |

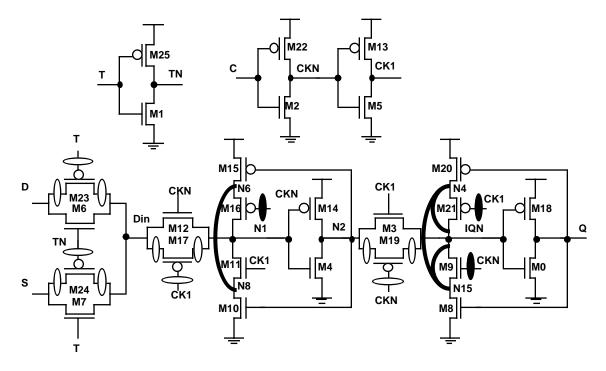

| 5.3-2   | D Flip-Flop Implementation.                                           | 138 |

| 5.3-3   | Current Distribution Graph for D Flip-Flop (IDDQg = 800 pA)           | 138 |

| 5.3-4   | Faults Missed by Pin Fault (10 of them) Test but Detected by Checking |     |

|         | Experiment for D Flip-Flop (Boolean Test Alone)                       | 139 |

| 5.3-5   | Faults Missed by Pin Fault (4 of them) Test Set but Detected by       |     |

|         | Checking Experiment for D Flip-Flop (Boolean and IDDQ Tests           |     |

|         | Used).                                                                | 140 |

| 5.3-6   | Faults Missed by Checking Experiment.                                 | 140 |

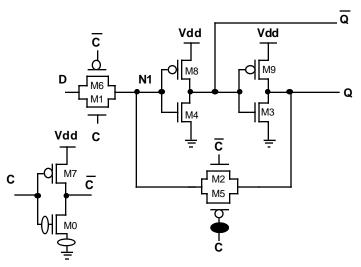

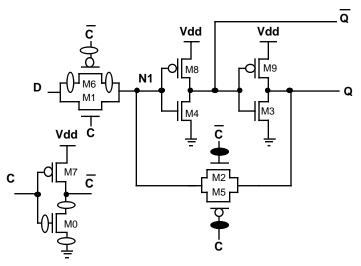

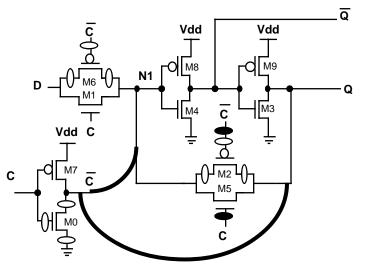

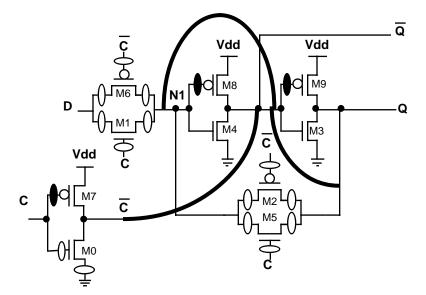

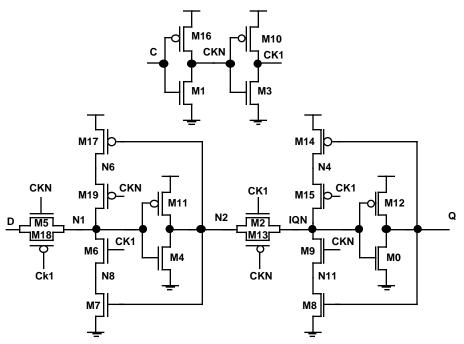

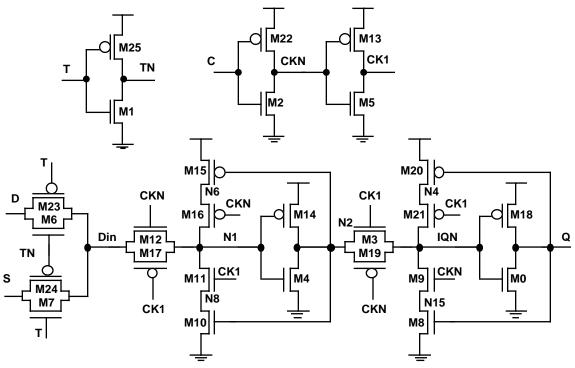

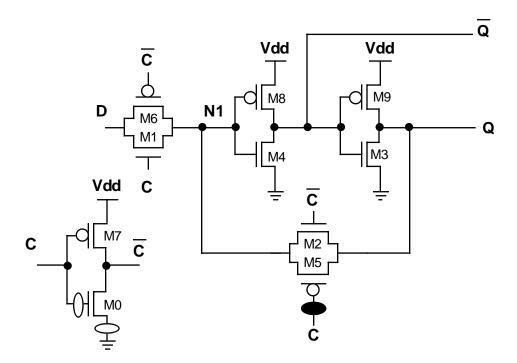

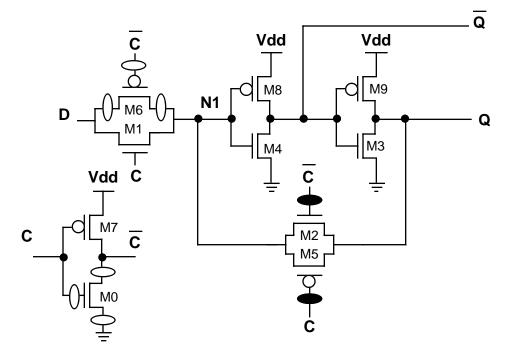

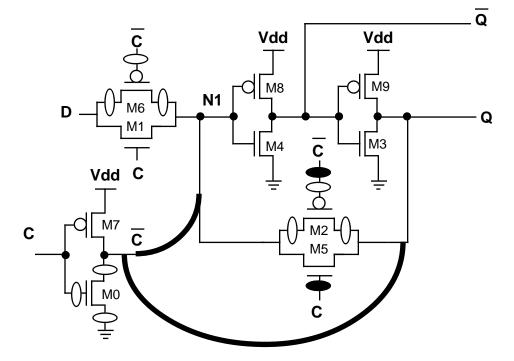

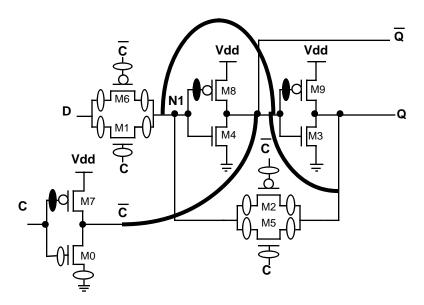

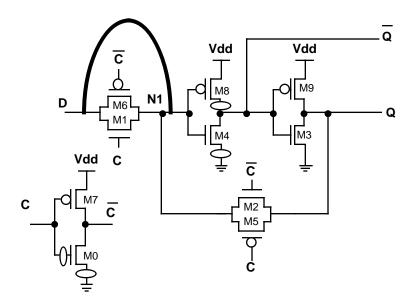

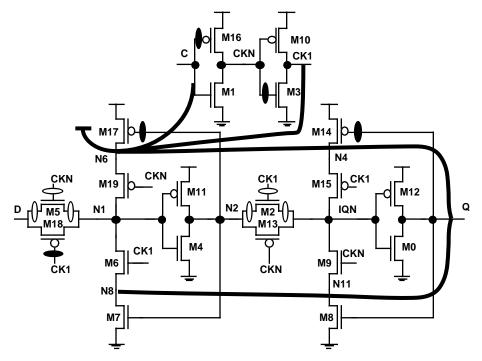

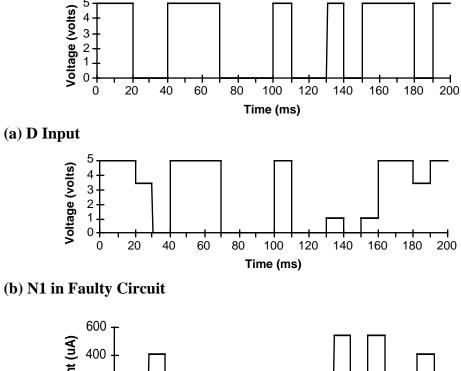

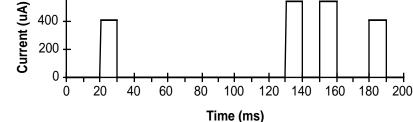

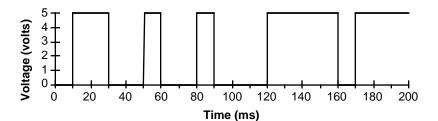

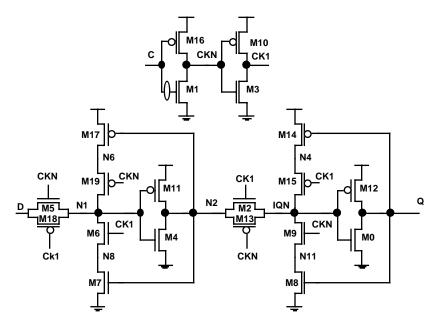

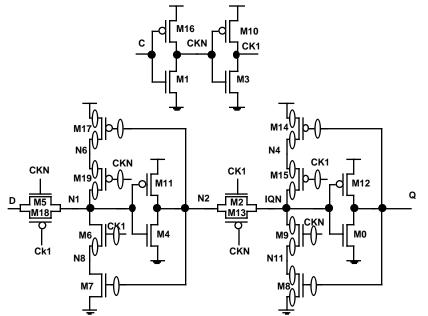

| 5.4-1   | MD Flip-Flop Implementation Used in Simulation                        | 142 |

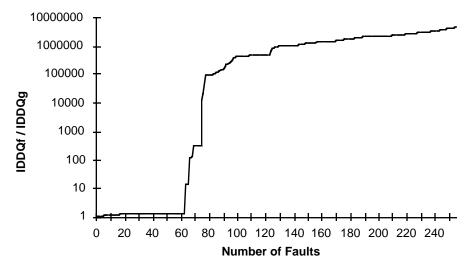

| 5.4-2   | Current Distribution Graph for MD Flip-Flop(IDDQg = 1 nA)             | 143 |

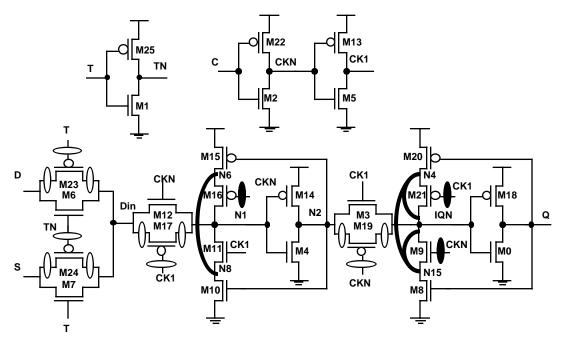

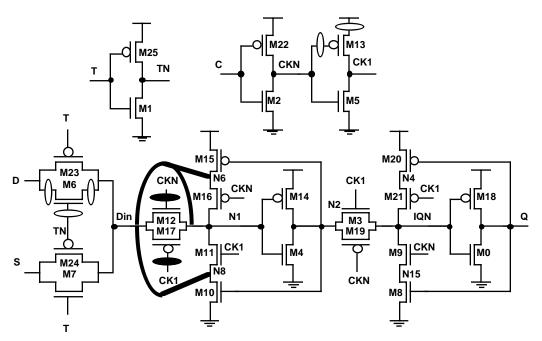

| 5.4-3   | Faults Missed by Checking Experiment of MD Flip-Flop (19 of them)     | 144 |

| 5.4-4   | Faults Missed by Pin Fault Test Detected by Checking Experiment of    |     |

|         | MD Flip-Flop (10 of them).                                            | 144 |

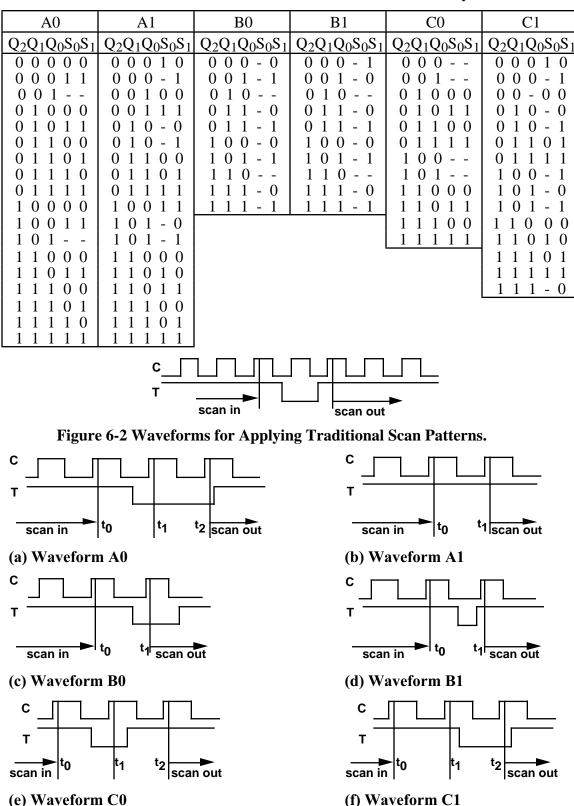

| 6-1 | Circuit for a Three-Bit Binary Counter.                  | 146 |

|-----|----------------------------------------------------------|-----|

| 6-2 | Waveforms for Applying Traditional Scan Patterns         | 148 |

| 6-3 | Waveforms for Applying Checking Experiment Test Patterns | 149 |

# LIST OF TABLES

| Table   | Title                                                                     |    |

|---------|---------------------------------------------------------------------------|----|

| 1-1     | State Table for Circuit in Fig. 1-6                                       | 6  |

| 1-2     | Checking Experiment for State Table of Table 1-1                          | 6  |

| 1-3     | State Table From Checking Experiment in Table 1-2.                        | 6  |

| 2.1-1   | Latches and Their Excitation Functions.                                   | 12 |

| 2.1-2   | A Minimum-Length (6) Checking Experiment for an SR-Latch.                 | 12 |

| 2.1-3   | A Minimum-Length (7) Checking Experiment for a D-Latch.                   | 12 |

| 2.1-4   | A Minimum-Length (14) Checking Experiment for an Asynchronous             |    |

|         | Set/Reset Latch.                                                          | 13 |

| 2.1-5   | A Minimum-Length (26) Checking Experiment for an MD-Latch                 | 13 |

| 2.1-6   | A Minimum-Length (23) Checking Experiment for a TP-Latch                  | 13 |

| 2.1-7   | A Minimum-Length (15) Checking Experiment for a Load Enable               |    |

|         | Latch                                                                     | 13 |

| 2.1-8   | A Minimum-Length (16) Checking Experiment for a D-Enable Latch            | 13 |

| 2.1-9   | A Minimum-Length (13) Checking Experiment for an XOR Input                |    |

|         | Latch                                                                     | 13 |

| 2.1-10  | A Minimum-Length (58) Checking Experiment for a BILBO Latch               | 14 |

| 2.1-11a | A Minimum-Length (25) Checking Experiment for a CBILBO Latch 1            | 14 |

| 2.1-11b | A Minimum-Length (26) Checking Experiment for a CBILBO Latch 2            | 14 |

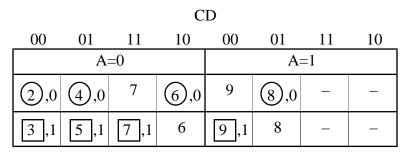

| 2.2-1a  | Two-State Flow Table                                                      | 17 |

| 2.2-1b  | Another Flow Table That Produces Same Output Sequence When                |    |

|         | Table 2.2-1c Sequence is Applied                                          | 17 |

| 2.2-1c  | Sequence That Visits All Total States, But is Not a Checking              |    |

|         | Experiment                                                                | 17 |

| 2.2-2   | Flow Table Fragment Explaining State Triples                              | 18 |

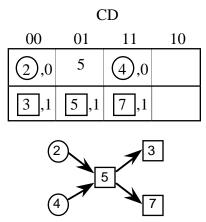

| 2.2-3a  | Two-State Flow Table                                                      | 19 |

| 2.2-3b  | Another Flow Table That Produces the Same Output Sequence When            |    |

|         | Table 2.2-3c Sequence is Applied                                          | 19 |

| 2.2-3c  | Sequence That Visits All Total States, Identifies Unstable States, But is |    |

|         | Not a Checking Experiment                                                 | 19 |

| 2.2-4   | Flow Table Fragment Explaining Links.                                     | 20 |

| 2.2-5   | Flow Table Marked With Checking Sequence                                  | 22 |

| 2.2.1-1 | Flow Table for Two-State SR-Latch.                                        | 27 |

| 2.2.1-2 | Minimum-Length (6) Checking Experiments for Two-State SR-Latch       | . 27 |

|---------|----------------------------------------------------------------------|------|

| 2.2.2-1 | Flow Table for Two-State D-Latch.                                    | . 28 |

| 2.2.2-2 | Minimum-Length (7) Checking Experiments for Two-State D-Latch        | . 28 |

| 2.2.3-1 | Flow Table for Two-State MD-Latch.                                   | . 29 |

| 2.2.3-2 | A Minimum-Length (26) Checking Experiment for MD-Latch               | . 30 |

| 2.2.4-1 | Flow Table for Two-State TP-Latch                                    | . 30 |

| 2.2.4-2 | A Minimum-Length (23) Checking Experiment for TP-Latch.              | . 31 |

| 2.3-1   | Reduced Flow Table for Two-State D-Latch in Shift Register           | . 34 |

| 2.3-2   | Test Sequence for Embedded D-Latch.                                  | . 34 |

| 2.3-3   | Five Cases of Sequences With All Four Transitions.                   | . 35 |

| 2.3-4   | Test Sub-Sequences Applied to Embedded D-Latch                       | . 36 |

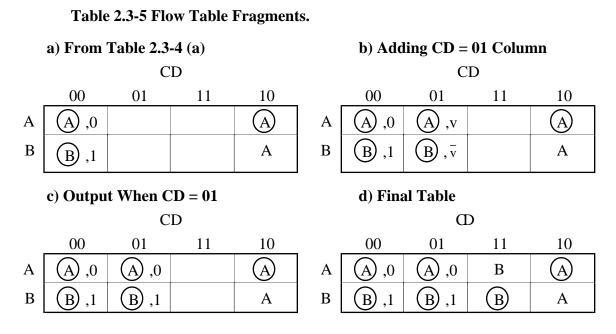

| 2.3-5   | Flow Table Fragments.                                                | . 37 |

| 2.4.1-1 | Reduced Flow Table for Two-State MD-Latch in Scan Chain              | . 39 |

| 2.4.2-1 | Reduced Flow Table for Two-State TP-Latch in Scan Chain.             | . 46 |

| 3.1.1-1 | Primitive Flow Table of D Flip-Flop.                                 | . 52 |

| 3.1.1-2 | Example of Minimum-Length (20) Checking Experiment for D Flip-       |      |

|         | Flop                                                                 | . 54 |

| 3.1.2-1 | Primitive Flow Table of MD-Flip-Flop.                                | . 56 |

| 3.1.2-2 | Example of Minimum-Length (138) Checking Experiment for MD Flip-     |      |

|         | Flop                                                                 | . 57 |

| 3.1.3-1 | Primitive Flow Table of TP Flip-Flop.                                | . 59 |

| 3.1.3-2 | Example of Minimum-Length (90) Checking Experiment for TP Flip-      |      |

|         | Flop                                                                 | . 60 |

| 3.2-1   | Marked-Up Primitive Flow Table for D Flip-Flop in a Shift Register   | . 62 |

| 3.2-2   | Reduced Primitive Flow Table for D Flip-Flop in a Shift Register     | . 63 |

| 3.2-3   | Example of Checking Experiment for D Flip-Flop in Shift Register     | . 64 |

| 3.2-4   | Transition Tour Responses from D Flip-Flop and Table 3.2-5.          | . 64 |

| 3.2-5   | Flow Table That Gives Same Response as Data Transition Tour to Flip- |      |

|         | Flop                                                                 | . 65 |

| 3.2-6   | Primitive Flow Table for Last D Flip-Flop in a Shift Register        | . 66 |

| 3.2-7   | Primitive Flow Table of First D Flip-Flop in Shift Register.         | . 67 |

| 3.2-8   | Example of Checking Experiment for the First D Flip-Flop in Shift    |      |

|         | Register                                                             | . 69 |

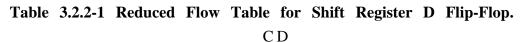

| 3.2.2-1 | Reduced Flow Table for Shift Register D Flip-Flop.                   | .71  |

| 3.3.1-1 | Marked-Up Primitive Flow Table of MD Flip-Flop in Scan Chain         | . 74 |

| 3.3.1-2 | Reduced Primitive Flow Table of MD Flip-Flop in Scan Chain           | . 75 |

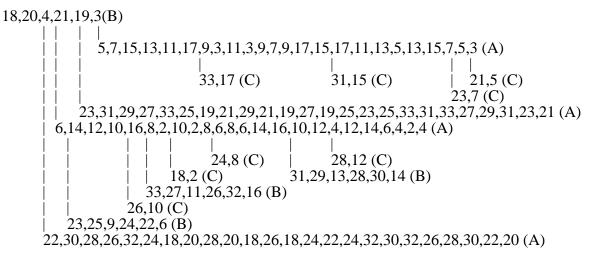

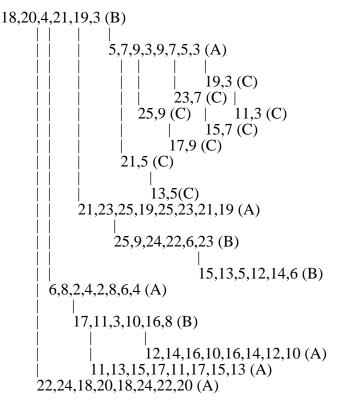

| 3.3.1-3 | Sub-Sequences Required for MD Flip-Flop Checking Experiment    | 81  |

|---------|----------------------------------------------------------------|-----|

| 3.3.2-1 | Marked-Up Primitive Flow Table of TP Flip-Flop in Scan Chain   |     |

| 3.3.2-2 | Reduced Primitive Flow Table of TP Flip-Flop in Scan Chain     | 91  |

| 3.3.2-3 | Sub-Sequences Required for TP Flip-Flop Checking Experiment    |     |

| 4.1-1   | CNF Clauses for Some Equations.                                | 102 |

| 4.2.3-1 | Pattern Tables and Their Groups for MD Flip-Flops.             | 120 |

| 4.2.3-2 | Handling Groups in ATPG for MD Flip-Flop Scan Chain            | 121 |

| 4.2.4-1 | Pattern Tables and Their Groups for TP Flip-Flops.             | 124 |

| 4.2.4-2 | Handling Groups in ATPG for TP Flip-Flop Scan Chain.           | 126 |

| 5.1-1   | Number of Faults Detected in D-Latch (Total Faults = 67)       | 132 |

| 5.1-2   | Flow Table for Two-State D-Latch.                              | 134 |

| 5.2-1   | Number of Faults Detected in MD-Latch (Total Faults = 129)     | 136 |

| 5.3-1   | Number of Faults Detected in D Flip-Flop (Total Faults = 170)  | 139 |

| 5.4-1   | Number of Faults Detected in MD Flip-Flop (Total Faults = 256) | 143 |

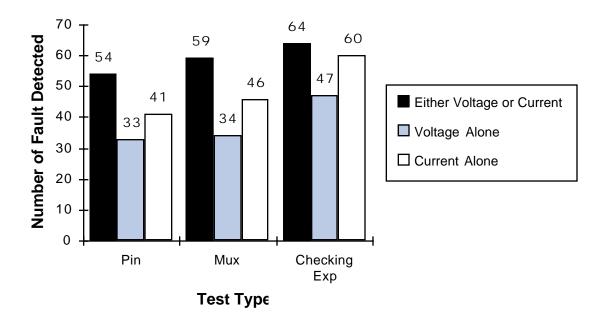

| 6-1     | Stuck-At Patterns for Three-Bit Binary Counter.                | 147 |

| 6-2     | Results of ATPG for Three-Bit Binary Counter                   | 148 |

| 6-3     | Patterns From MDFF ATPG for Three-Bit Binary Counter           | 148 |

| 6-4     | Summary of Simulation Results for Three-Bit Binary Counter     | 149 |

| 6-5     | Number of Patterns for Different Tests.                        | 151 |

| 6-6     | Number of Patterns Divided by Stuck-At Test Length.            | 151 |

## **Chapter 1. Introduction**

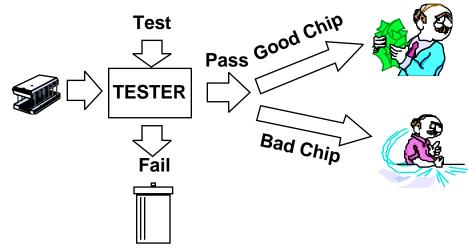

Chips are tested to ensure that defective ones are not shipped to customers. This is important for economic reasons. Using a defective chip in a system may render the entire system defective. In some cases, such as space equipment, it may not be even possible to replace a defective chip once it is operational. Thus, it is important to test chips before they are used, and it is important to test them thoroughly. The test process is illustrated in Fig. 1-1. A chip is placed on the tester, and a test is applied to it. Only chips that pass the manufacturer's test are shipped to the customer. Failed chips are sometimes analyzed to identify manufacturing process problems [Miczo 86]. Depending on how good the test is, some of the chips sent to the customer may be defective. A more thorough test would minimize the number of defective chips shipped to the customer.

A chip is faulty if it contains one or more defects. *Test generation* is the process of producing the test patterns that will identify chips with defects.

Figure 1-1 Test Process.

Test generation depends on the type of circuit being tested. Digital circuits are of two types: combinational and sequential. In combinational circuits the outputs depend only on the present inputs; outputs of sequential circuits depend on past as well as present inputs. There are many tests that can be used for combinational logic. An *exhaustive test* applies all possible patterns to the inputs of the circuit. This approach guarantees that any defect that would change the functionality of the combinational logic, without making it sequential, is detected. However, due to the large number of patterns needed by this technique, other approaches have been used. In pseudo-exhaustive test [McCluskey 86], the circuit is partitioned into smaller blocks, and each of the blocks is tested exhaustively.

For example, in Fig. 1-2a, a small circuit with 6 inputs is shown. An exhaustive test requires 64  $(2^6)$  patterns. With the partitions shown in Fig. 1-2b, only 20 patterns are needed, 8  $(2^3)$  for partition A and 8  $(2^3)$  for partition B, and 4  $(2^2)$  for partition C.

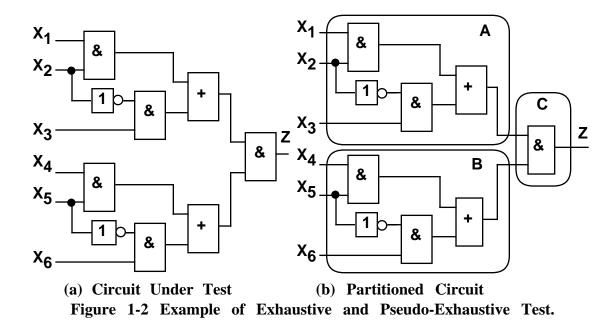

Another approach to reduce the size of an exhaustive test is pseudo-random test [Savir and Bardell 84; Williams 85; Chin and McCluskey 87; McCluskey et. al. 88]. In this test, non-repeating and reproducible random patterns are applied. The fact that the patterns are non-repeating and reproducible makes them not true random patterns. The non-repeating nature has two advantages over true random patterns: saving time since repeating a pattern won't detect more defects, and a small circuit can be used for implementing it. The reproducibility of the patterns makes it possible to "fault grade" the patterns. Typically, a linear feedback shift register (LFSR) is used to generate pseudorandom patterns [McCluskey 86]. An example of such a circuit is shown in Fig. 1-3.

A more direct approach to test generation is to generate patterns for the defects expected in the circuit. However, the difficulty of generating patterns from defects, and the

Figure 1-3 Example of LFSR (Linear Feedback Shift Register).

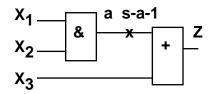

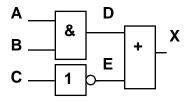

continuing change of technology used for digital design, has lead to the use of fault models as an abstraction of defects. The most commonly used fault model is the *single-stuck fault* model [Abramovici 90]. In this model, one line in the circuit is assumed to be always stuck at 0 or 1. The goal of test generation is to find a pattern that would produce different output when applied to a good and faulty circuit. For example, in the circuit of Fig. 1-4, suppose we need to find a test for line *a* stuck-at 1. First, the input pattern should set line *a* to 0 so that the faulty and fault-free circuits have different behavior. The good circuit will have 0 while the faulty circuit will have 1 due to the fault. Setting line *a* to 0 requires either  $X_1 = 0$  or  $X_2 = 0$ . We also have to make sure that the error in the faulty circuit (i.e., the 1 instead of 0) appears at the primary output (Z). If X<sub>3</sub> is set to 1, then the output of both the good and faulty circuit we should be 1 and we will not detect the fault. By setting X<sub>3</sub> to 0 the output will depend on the value at line *a*. For the good circuit we should see 0 at the output, and for the faulty circuit we should see 1. Therefore, a test for line *a* stuck-at 1 is  $X_1X_2X_3 = -00$  or 0-0. A "-" in a pattern means either 0 or 1 would work.

Figure 1-4 Example of Test Generation Using Stuck-At Fault Model.

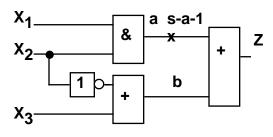

The problem becomes more complicated when we have reconvergent fanout. For example, consider the circuit in Fig. 1-5. As in the previous example, we want a test for line *a* stuck-at 1. We need to set line *a* to 0, which can be done with  $X_1 = 0$  or  $X_2 = 0$ . Suppose we select  $X_2$  to be 0. This would imply that line *b* will be 1. The output of the good and faulty circuit would then be 1, and we would not detect the fault. So, we need to use  $X_1 = 0$ . We also need line *b* to be 0 so that the effect of the fault appears at the primary output. This requires  $X_2 = 1$  and  $X_3 = 0$ .

Figure 1-5 Example of Test Generation for Circuit With Reconvergent Fanout.

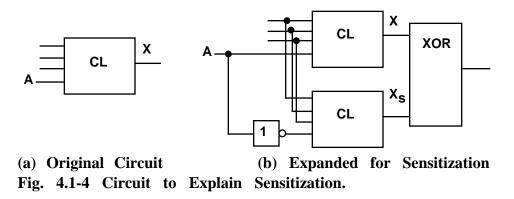

There are several algorithms for generating patterns for combinational circuits based on the single-stuck fault model. The boolean difference is an algebraic method that finds an equation representing tests for a fault [Sellers et. al. 68]. The difficulty of algebraic methods to handle large circuits efficiently has given way to structural methods. One algebraic approach that has proven to be successful for large circuits is boolean satisfiability [Larrabee 89]. This method takes advantage of the fact that only one pattern is really needed to satisfy the boolean equation generated and does not attempt to reduce the algebraic expressions. The first of the structural methods, the D-Algorithm [Roth 66] assigns a D to the faulty line in the circuits, and propagates its effect towards the output, while "justifying" the values on gates that drive the line, similar to what we did in the above example. In the search for a pattern, there are often many choices. In the above example, we had a choice of which AND gate input to set to 0. Our first choice resulted in a conflict with another part of the test. In this case, the other choice was taken, and the process repeated. The process of canceling a choice, and trying another is called *backtracking*. The efficiency of a test generation algorithm depends heavily on the amount of backtracking required before a test is found. PODEM (path oriented decision analysis) was introduced to reduce the amount of backtracking encountered with the D-Algorithm [Goel 81]. In PODEM, values are assigned to the primary inputs successively, until either a pattern is found, or the fault is proven undetectable. An incorrect assignment at the primary input will cause backtracking. However, since there are generally fewer primary inputs than lines in the circuit, the number of backtracks are generally fewer. FAN (fanout oriented) further improved on PODEM by allowing assignments to some fanout nodes as well as primary inputs [Fujiwara and Shimono 83].

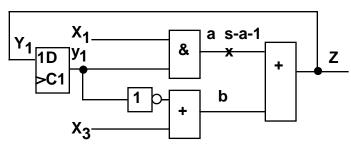

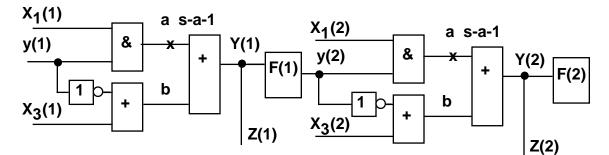

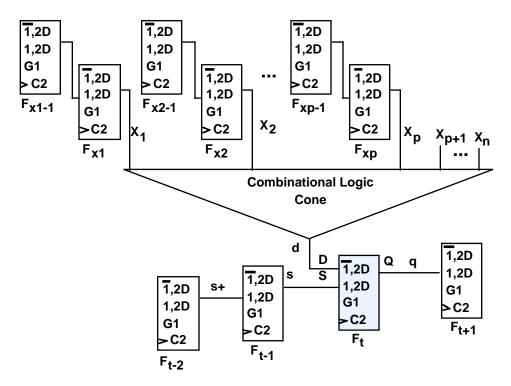

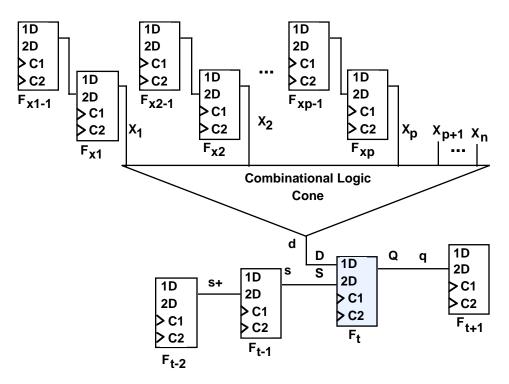

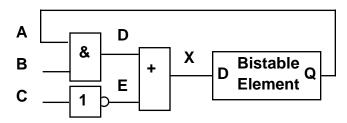

Generating a test for a sequential circuit is much more difficult than for a combinational one, because the output response depends not just on the input but on a sequence of inputs. Mourad [90] gives an excellent survey of the different approaches for sequential test generation. There have been a few attempts ([Kubuo 68; Putzolu and Roth 71; Muth 76]) at extending the combinational test generation algorithms to handle sequential circuits. The basic idea is to replicate the combinational logic multiple times, treating each flip-flop output as a pseudo-input, and flip-flop inputs as pseudo-outputs. For example, consider the circuit in Fig. 1-6. Again we want to find a test for line *a* stuck-at 1. Fig. 1-7 shows the combinational circuit replicated twice. The notation used here is taken from Fujiwara's book [85]. The combinational logic is the same as that of Fig. 1-5, so we would like to use the same pattern  $X_1X_2X_3 = 010$ . However, instead of  $X_2$  as a primary input we have a bistable element. Therefore, starting in time frame 2, we need  $X_1(2)y(2)X_3(2) = 010$ . This implies that we need Y(1) = 1. Y(1) can be set to 1 by

setting  $X_3(1)$  to 1. So, our test requires two consecutive patterns. The first one  $X_1X_3 =$  -1 will make the flip-flop output become 1, and the second pattern  $X_1X_3 = 00$  will detect our fault as before. In this example, we only needed two time frames. In general, many time frames could be needed.

Figure 1-6 Example of Test Generation for Sequential Circuits.

Figure 1-7 Replicating Combinational Logic for Sequential Test Generation.

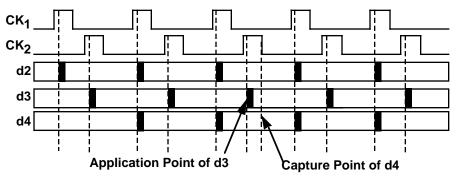

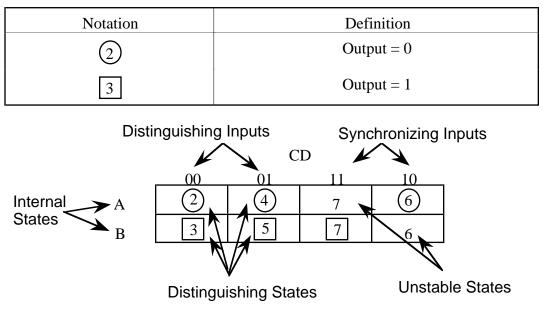

Another approach for testing sequential circuits is to use the state table. Here, a functional description of a sequential circuit is used, rather than the circuit, to find a test. For example, Table 1-1 shows the state table for the circuit in Fig. 1-6. The idea is to find a sequence of inputs that when applied to the circuit would give different output than any other circuit with the same input, outputs, and same number of or fewer states. Such a sequence, a *checking experiment*, contains enough information to reconstruct the state table from the observed output when the sequence is applied. The sequence in Table 1-2 is a checking experiment for the state machine described in Table 1-1. We can prove this by deriving the state table from the sequence. Looking at patterns 2 and 3 of this sequence, we see that the circuit has different outputs when  $X_1X_3 = 00$  is applied. This indicates that there must be two states in the state machine. We call these states A and B and create Table 1-3. States are shown slightly offset from the pattern in Table 1-2, to show the states before and after a pattern has been applied. After pattern 2, we are in state A and after pattern 3 we are in state B. From patterns 2, 3 and 4 we see that applying  $X_1X_3 = 00$  will

switch between the two states. We can thus fill the first column of Table 1-3. Since we assume that there must be at most two states in the circuit,  $X_1X_3 = 00$  can be used as a distinguishing sequence. A *distinguishing sequence* is a sequence that gives a different output sequence for each state. In our example if we apply X  $X_3 = 00$  and see a 1 at the output then we were in state A before applying the distinguishing sequence, and if we see a 0 then we were in state B. In Table 1-2, states followed by the distinguishing sequence  $X_1X_3 = 00$  are highlighted. In pattern 5, we have  $X_1X_3 = 01$ , and see an output of 1. Since we were in state A before this pattern was applied, we can put 1 as the output value in the entry marked (1) in Table 1-3. The pattern is followed by the distinguishing sequences  $(X_1X_3 = 00)$  with an output of 0. This implies that the next state in entry (1) should be B. The rest of the table is filled in the same way. If we map state A to 0 and state B to 1, we get the same table as Table 1-1, proving that the sequence in Table 1-2 really is a checking experiment. A systematic approach for generating a checking experiment is given in Hennie [64] and Friedman and Menon [71]. The main problem with checking experiments is that the number of patterns can be very large for even small circuits, making it impractical for real designs.

Table 1-1 State Table for Circuit in Fig. 1-6.

| $X_1$ | X3 |

|-------|----|

|-------|----|

| У <sub>1</sub> | 00               | 01  | 11  | 10  |  |  |  |  |  |  |  |  |  |

|----------------|------------------|-----|-----|-----|--|--|--|--|--|--|--|--|--|

| 0              | 1,1              | 1,1 | 1,1 | 1,1 |  |  |  |  |  |  |  |  |  |

| 1              | 0,0              | 1,1 | 1,1 | 1,1 |  |  |  |  |  |  |  |  |  |

|                | Y <sub>1</sub> Z |     |     |     |  |  |  |  |  |  |  |  |  |

Table 1-2 Checking Experiment for State Table of Table 1-1.

| Pattern  | 1 | 2  | 3   | 4 | 5   | 6   | 7   | 8 | 9 | 10 | 11  | 12  | 13  | 14  | 15 | 16 | 17  | 18  | 19 |

|----------|---|----|-----|---|-----|-----|-----|---|---|----|-----|-----|-----|-----|----|----|-----|-----|----|

| X1       | 0 | 0  | 0   | 0 | 0   | 0   | 0   | 0 | 0 | 1  | 0   | 0   | 1   | 0   | 1  | 0  | 0   | 1   | 0  |

| X3       | 1 | 0  | 0   | 0 | 1   | 0   | 0   | 1 | 0 | 1  | 0   | 0   | 1   | 0   | 0  | 0  | 0   | 0   | 0  |

| Z        | 1 | 0  | 1   | 0 | 1   | 0   | 1   | 1 | 0 | 1  | 0   | 1   | 1   | 0   | 1  | 0  | 1   | 1   | 0  |

| State    | E | ₿⊿ | A ] | B | A I | ₿ ∦ | A . | В | B | A  | 3 4 | A E | 3 E | 3 A | ł  | 34 | A E | 3 E | 3  |

| Position | 1 |    |     |   |     |     | 2   |   |   | 3  |     | 4   |     |     | 5  |    | 6   |     |    |

#### Table 1-3 State Table From Checking Experiment in Table 1-2.

|   |     | X1      | X3      |         |

|---|-----|---------|---------|---------|

|   | 00  | 01      | 11      | 10      |

| А | B,1 | B,1 (1) | B,1 (3) | B,1 (5) |

| В | A,0 | B,1 (2) | B,1 (4) | B,1 (6) |

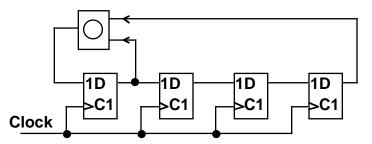

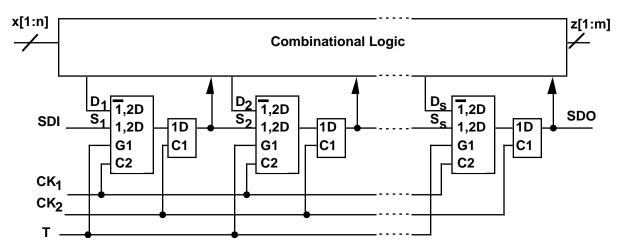

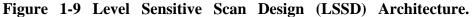

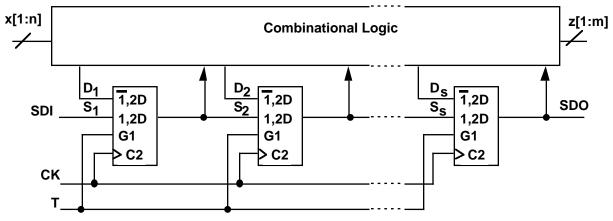

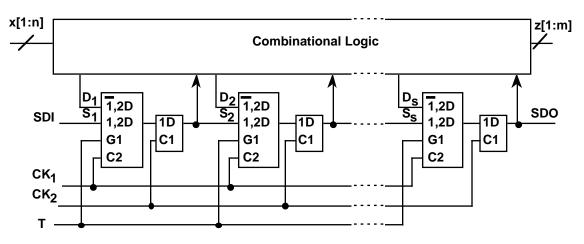

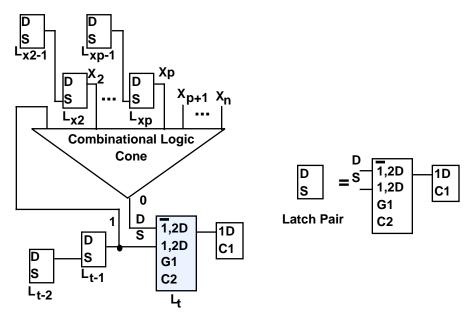

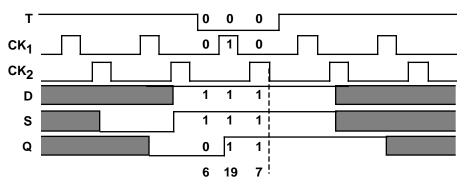

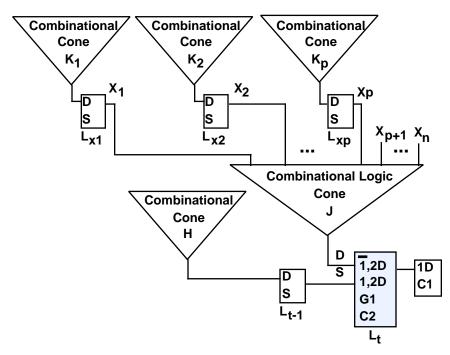

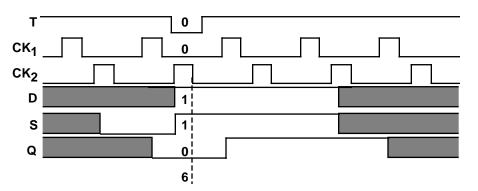

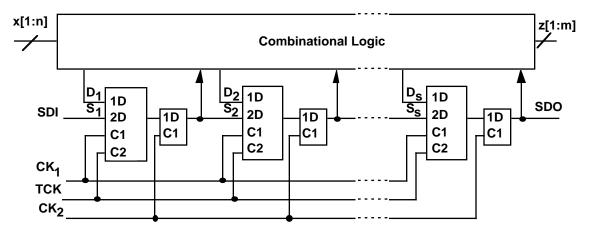

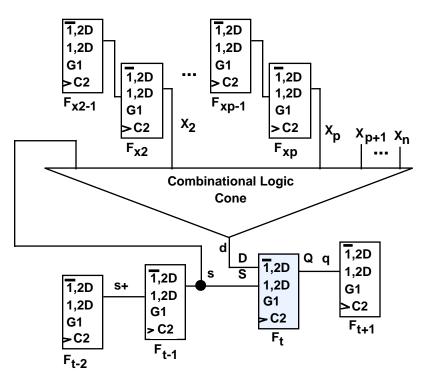

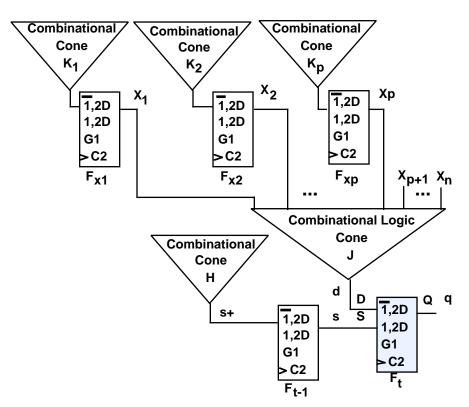

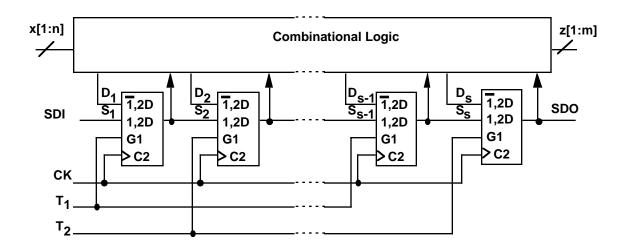

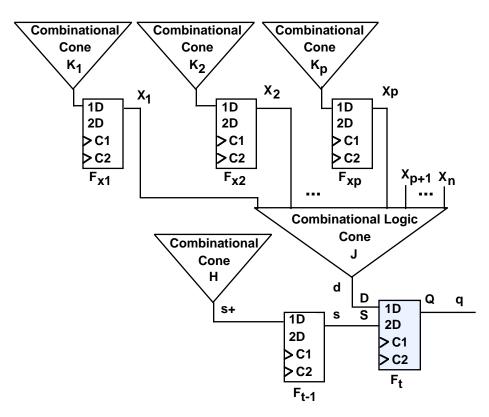

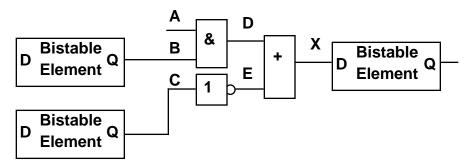

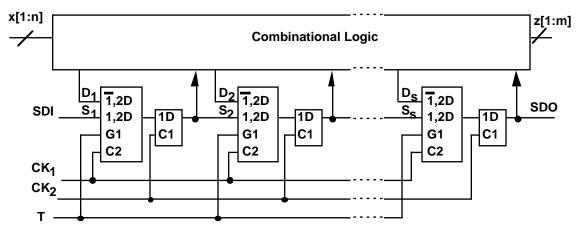

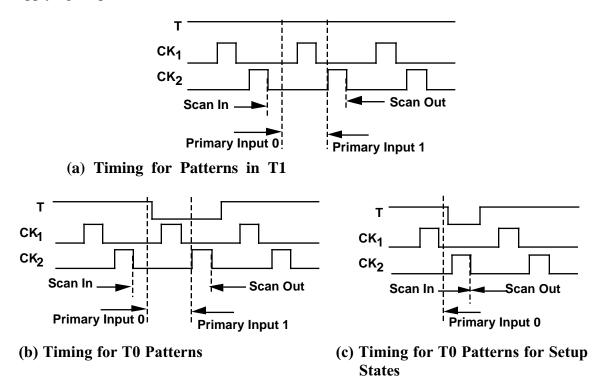

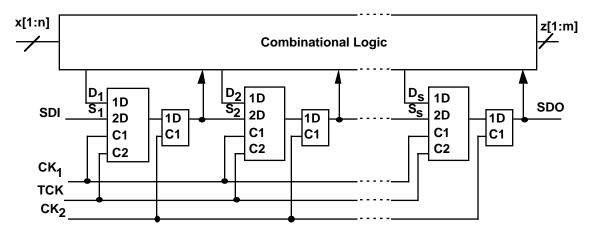

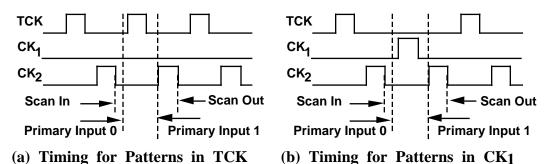

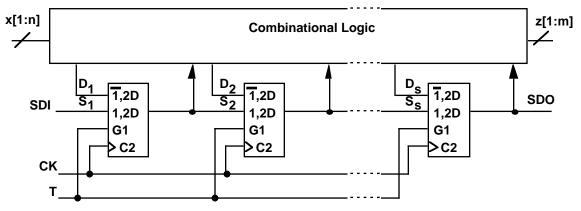

Scan was introduced to overcome the difficulties of sequential test generation described above [Williams and Angel 73; Eichelberger and Williams 77]. The basic idea of scan is to allow easy access to the flip-flops in the design so that patterns can be applied directly to the inputs of the internal combinational logic, and the outputs of the internal combinational logic can be observed from the primary output. This makes it possible to use the methods discussed for combinational circuits on sequential ones. There are several architectures for scan designs [McCluskey 86]. These are shown in Figs. 1-8 through 1-11. There are two modes of operation in any scan design: shift mode and normal mode. In *shift mode*, the scan chain is configured as a shift register to scan data in and out of the bistable elements. In *normal mode*, the bistable elements are configured to get their inputs from the combinational logic and perform normal functional operation of the circuit. In the MD-latch and MD flip-flop architectures, the shift mode is activated by setting T = 1, and normal mode is activated by setting T = 0. In the other two architectures, TCK is used as the clock for shift mode, and CK<sub>1</sub> is used for normal mode.

The combinational logic is tested by scanning in a pattern with the scan chain in shift mode. Values at the primary input are then applied, and values at the primary output are checked. The scan chain is switched to normal mode for one cycle to capture the output of the combinational logic in the bistable elements. Then the scan chain is switched back to shift mode, and the contents of the bistable elements are scanned out and checked at SDO. The next pattern is scanned in while the bistable element contents are being scanned out. The bistable elements themselves are tested by shifting a pattern that applies all four transitions (0->0, 0->1, 1->1 and 1->0) to the bistable elements. An example of such a pattern is 00110.

Figure 1-8 MD-Latch Based Scan Architecture.

Figure 1-11 TP Flip-Flop Based Scan Architecture.

The problem with this method of testing the bistable elements is that it does not address faults within the bistable elements. Experimental results shown in Chapter 5 of this thesis show that this can be a serious problem. However, this is not the first work to show that faults inside bistable elements can be missed by traditional scan tests. Reddy and Reddy [86] derived tests for stuck-open faults in different latch implementations. Lee and Breuer [90] analyzed bridging faults in scan registers, and combined the use of current and voltage tests. Al-Assadi [93] mapped many, but not all, of the internal faults to functional fault models. He also showed that some of the internal faults cannot be mapped to functional fault models.

What is missing from the previous work is an implementation independent test that will detect all the faults in latches and flip-flops, and a method to automatically generate such a test for bistable elements used in scan chains. This is where the work in this thesis begins. We combine the work of checking experiments mentioned earlier, with the work on scan and structural test generation to create a new algorithm that can generate tests for the latches and flip-flops in the scan chain. As mentioned earlier, checking experiments were not practical for real designs. However, we use a checking experiment only for the bistable elements themselves. From the requirements of the checking experiment for the bistable element, an algorithm that generates test patterns was developed. These patterns are scanned in as in the case of tests for the combinational logic, but rather than switching to normal mode for one cycle, the circuit is kept in normal mode for several cycles depending on the type of pattern. This will be discussed in detail in Chapter 4.

There are two types of bistable elements: latches and flip-flops. In latches, when an input value is changed, any effect on the output appears right after the input changes. This property is often called the *transparency property* of latches [McCluskey 86]. Chapter 2 describes the method of generating checking experiments for two-state latches, and shows how checking experiments can be applied to latches embedded in shift registers or scan chains. The other type of bistable elements, flip-flops, do not have the transparency property of the latch. A flip-flop output changes only in response to transition on a control input or a change in an asynchronous input [McCluskey 86]. Chapter 3 describes the method of generating checking experiments for flip-flops, and shows how checking experiments can be applied to flip-flops embedded in shift registers or scan chains. Chapter 4 describes the new test generation algorithm that will apply checking experiments to all the bistable elements in the circuit. The algorithm was implemented in C by modifying an existing combinational test generation program. The reason for selecting an existing test generation program was to show that this new algorithm can be easily implemented by enhancing existing commercial test generation program for real designs.

The effectiveness of the new method can be measured by fault simulating a circuit. The results of fault simulation of individual bistable elements presented in Chapter 5. In Chapter 6 we fault simulate a three-bit binary counter using traditional test patterns and patterns for an MD flip-flop architecture. The results show that many faults are missed by the traditional test. In the same chapter we generate patterns for the ISCAS-89 benchmarks [Brglez et. al. 89]. The number of patterns generated for these circuits indicate that our algorithm will generate a reasonable number of test patterns for real circuits.

### Contributions

Contributions to knowledge, described in this thesis, are summarized as follows:

- 1. Development of a new approach for generating test patterns for bistable elements in a scan chain design. The test patterns guarantee the detection of all faults that do not increase the number of states of the bistable element.

- Implementation of this new approach by modifying an existing stuck-at automatic test pattern generation tool. The implementation was run on all the ISCAS 89 benchmarks, and the results indicate that this new approach is practical for large circuits.

- 3. Introduction of a new method for easily deriving checking experiments for twostate latches, and derivation of a lower bounds on the number of patterns needed for checking experiments of two-state latches.

- 4. Introduction of a new method for deriving checking experiments for bistable elements that are embedded in a circuit, taking into account controllability of the inputs and observability of the outputs.

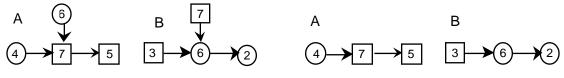

- 5. Derivation of simple tests for bistable elements in shift registers and demonstration that any data sequence that applies all four transitions will apply a checking experiment to a double-rank shift register.

## **Chapter 2. Checking Experiments for Latches**

Latches are memory elements that have the *transparency property*. When an asynchronous input of a latch is changed, any effect on the output appears shortly after the input changes, and when a synchronous input is changed, the output changes shortly after the input changes if the control input is active [McCluskey 86]. This chapter begins with a summary of various latches and checking experiments for them in Section 2.1. The theoretical details for generating checking experiments for two-state latches are given in Section 2.2. Checking experiments for some of the latches are derived in the same section, and checking experiments for the rest are derived in Makar and McCluskey [94]. As most circuits consist of more than just a single latch, we show what happens to a D-latch once it is used in a shift register in Section 2.3. In that section, we show that any data sequence, such as 01100, that applies all four transitions (0->0, 0->1, 1->0 and 1->1) will apply a checking experiment to all the latches in the shift register. In Section 2.4 we apply the same technique of Section 2.3 to MD-latches and TP-latches used in scan chains. We show that there is no simple test that can be applied, and present a technique to generate patterns to test the latches in the scan chain.

#### 2.1 Latches and Their Minimum-Length Checking Experiments

Various latch types are discussed in this section (see Table 2.1-1). The simplest latch type is the SR-latch. An SR-latch is a sequential element that can be set or reset by activating the appropriate input. Even though the SR-latch is still occasionally used, the most commonly used latch today is the D-latch. A D-latch is a sequential element, in which the data input is propagated to the output when the clock is active, otherwise it holds the stored value. A *D*-latch with Asynchronous Set/Reset is a D-latch that can be set or reset when the clock is not active. Scan-paths require latches with two different data sources. These can be either Multiplexed-Data latches or Two-Port latches. A Multiplexed-Data latch (MD-latch) is a D-latch with multiplexed data inputs; a Two-Port *latch* (*TP-latch*) has two control inputs with the data source determined by the active control input [McCluskey 86]. A *Load Enable latch* is a D-latch with a gated control input, and a D-Enable latch is a D-latch with gated data. An XOR Input latch performs an exclusive-or operation on its two data inputs. This latch is commonly used in an LFSR (linear feedback shift register) to generate pseudo-random vectors, and to compress results. Other latches commonly used for BIST (built-in self test) are the Built-In Logic Block Observer latch (BILBO latch), and the Concurrent Built-In Logic Block Observer *latches* (CBILBO latches). The BILBO latch has two data inputs. It can be configured to

load either of the two inputs (one a scan input, and the other for normal operation), load the exclusive-or of the two inputs (for signature analysis), or load 0. The CBILBO latches, an extension of the BILBO latch, are two latches that can operate simultaneously as a pseudo-random pattern generator and a signature analyzer. The two latches are treated separately, with outputs  $Q_1$  and  $Q_2$ . Table 2.1-1 shows the excitation function of each of these latches and the minimum-length of a checking experiment. Minimum-length checking experiments for each of these latches are shown in Tables 2.1-2 through 2.1-11. Details for deriving checking experiments for some of the latches are given in Section 2.2. Details for the rest are given in Makar and McCluskey [94].

| Latch Type                             | Excitation Function                                                                                             | Assumptions       | M* |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------|----|

| SR-Latch                               | $Q = S + \overline{R}q$                                                                                         | SR = 0            | 6  |

| D-Latch                                | Q = CD + Cq                                                                                                     |                   | 7  |

| D-Latch with<br>Asynchronous Set/Reset | $Q = \overline{R} (S + CD + \overline{C}q)$                                                                     | $\mathbf{SR} = 0$ | 14 |

| MD-Latch                               | Q = C (TS + TD) + C q                                                                                           |                   | 26 |

| Two-Port Latch                         | $\mathbf{Q} = \mathbf{C}_1 \mathbf{D}_1 + \mathbf{C}_2 \mathbf{D}_2 + \mathbf{\overline{C}_1 \overline{C}_2 q}$ | $C_1 C_2 = 0$     | 23 |

| Load Enable Latch                      | Q = CLD + (LC)q                                                                                                 |                   | 15 |

| D-Enable Latch                         | $Q = CDE + \overline{C}q$                                                                                       |                   | 16 |

| XOR Input Latch                        | $\mathbf{Q} = \mathbf{C} \ (\mathbf{D} \oplus \mathbf{S}) + \mathbf{C}\mathbf{q}$                               |                   | 13 |

| BILBO Latch                            | $Q = C (B_1 D \oplus \overline{B}_2 S) + \overline{C} q$                                                        |                   | 58 |

| CBILBO Latch                           | $Q_1 = C (\overline{B_1}D \oplus S) + \overline{C} q_1$                                                         |                   | 25 |

|                                        | $Q_2 = C (B_2 S + B_2 D) + C q_2$                                                                               |                   | 26 |

\*M - minimum length (number of test vectors) of checking experiment.

#### Table 2.1-2 A Minimum-Length (6) Checking Experiment for an SR-Latch.

| S | 0 | 0 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|

| R | 1 | 0 | 0 | 0 | 1 | 0 |

| Q | 0 | 0 | 1 | 1 | 0 | 0 |

Table 2.1-3 A Minimum-Length (7) Checking Experiment for a D-Latch.

| С | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

|---|---|---|---|---|---|---|---|

| D | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| Q | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| C | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| D | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| R | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| S | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| Q | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

Table 2.1-4 A Minimum-Length (14) Checking Experiment for an Asynchronous Set/Reset Latch.

Table 2.1-5 A Minimum-Length (26) Checking Experiment for an MD-Latch.

| Т | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| С | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| D | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| S | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| Q | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

Table 2.1-6 A Minimum-Length (23) Checking Experiment for a TP-Latch.

| C <sub>1</sub> | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

|----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| D <sub>1</sub> | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| C2             | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| D2             | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Q              | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

# Table 2.1-7 A Minimum-Length (15) Checking Experiment for a Load Enable Latch.

| L | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| D | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| C | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| Q | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

# Table 2.1-8 A Minimum-Length (16) Checking Experiment for a D-Enable Latch.

| D | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| E | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| C | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| Q | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

# Table 2.1-9 A Minimum-Length (13) Checking Experiment for an XOR Input Latch.

| D | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| С | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| Q | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

# Table 2.1-10 A Minimum-Length (58) Checking Experiment for a BILBO Latch.

| D              | 0           | 0           | 0           | 0           | 0           | 0           | 0                | 0           | 0           | 0      | 1                     | 1           | 1           | 1                | 1                | 1                                                              | 1                                               | 0      | 0           | 0                     | 0           | 0           | 0                     | 0                | 0           | 0      | 1           | 1                | 1                     |

|----------------|-------------|-------------|-------------|-------------|-------------|-------------|------------------|-------------|-------------|--------|-----------------------|-------------|-------------|------------------|------------------|----------------------------------------------------------------|-------------------------------------------------|--------|-------------|-----------------------|-------------|-------------|-----------------------|------------------|-------------|--------|-------------|------------------|-----------------------|

| S              | 0           | 0           | 0           | 0           | 0           | 0           | 1                | 1           | 1           | 0      | 0                     | 0           | 0           | 0                | 0                | 0                                                              | 0                                               | 0      | 0           | 0                     | 0           | 0           | 0                     | 1                | 1           | 1      | 1           | 1                | 1                     |

| B2             | 0           | 0           | 0           | 0           | 0           | 0           | 0                | 0           | 0           | 0      | 0                     | 0           | 0           | 0                | 1                | 1                                                              | 1                                               | 1      | 1           | 1                     | 1           | 1           | 1                     | 1                | 1           | 1      | 1           | 1                | 1                     |

| B <sub>1</sub> | 0           | 1           | 1           | 0           | 0           | 0           | 0                | 0           | 0           | 0      | 0                     | 1           | 1           | 1                | 1                | 1                                                              | 1                                               | 1      | 1           | 1                     | 0           | 0           | 0                     | 0                | 0           | 0      | 0           | 0                | 0                     |

| C              | 1           | 1           | 0           | 0           | 1           | 0           | 0                | 1           | 0           | 0      | 0                     | 0           | 1           | 0                | 0                | 1                                                              | 0                                               | 0      | 1           | 0                     | 0           | 1           | 0                     | 0                | 1           | 0      | 0           | 1                | 0                     |

| 0              | 1           | 0           | 0           | 0           | 1           | 1           | 1                | 0           | 0           | 0      | 0                     | 1           | 0           | 0                | 0                | 1                                                              | 1                                               | 1      | 0           | 0                     | 0           | 1           | 1                     | 1                | 0           | 0      | 0           | 1                | 1                     |

|                | -           | U           | 0           | U           | -           | -           | 1                | U           | U           | 0      | U                     | -           | U           | U                | 0                | -                                                              | -                                               | -      | U           | 0                     | U           | -           | -                     | -                | U           | 0      | 0           | -                | -                     |

| D              | 1           | 1           | 1           | 1           | 1           | 1           | 1                | 1           | 1           | 1      | 1                     | 1           | 1           | 1                | 1                | 1                                                              | 1                                               | 0      | 0           | 0                     | 1           | 1           | 1                     | 1                | 1           | 0      | 0           | 0                | 0                     |

| D<br>S         | 1<br>1      | 1<br>1      | 1<br>1      | 1<br>0      | 1<br>0      | 1<br>0      | 1<br>0           | 1<br>0      | 1<br>0      | 1<br>0 | 1<br>0                | 1           | 1<br>1      | 1<br>1           | 1<br>1           | 1                                                              | 1 1                                             | 0<br>1 | 0<br>1      | 0<br>1                | 1<br>1      | 1           | 1                     | 1                | 1<br>0      | 0<br>0 | 0<br>1      | 0<br>1           | 0<br>1                |

|                | 1<br>1<br>0 | 1<br>1<br>0 | 1<br>1<br>0 | 1           | 1<br>0<br>0 | 1<br>0<br>0 | 1<br>0<br>1      | 1           | 1           | 1      | 1<br>0<br>1           | 1           | 1           | 0<br>1<br>1<br>0 | 1<br>1<br>1      | 1<br>1<br>1                                                    | $\frac{1}{1}$                                   | -      | 0           | 0<br>1<br>1           | 1<br>1<br>1 | 1           | 1<br>1<br>1           | 1<br>1<br>0      | 1           | 0      | 0<br>1<br>0 | 0<br>1<br>0      | 0<br>1<br>0           |

| S              |             | 1<br>1      | 1           | 1<br>0      | -           |             | 1<br>0<br>1<br>0 | 1           | 1<br>0      | 1      | 1<br>0<br>1<br>1      | 1           | 1           | 1                | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1                                               | $\frac{1}{1}$ $\frac{1}{1}$                     | 1      | 0           | 0<br>1<br>1<br>1      | 1           | 1           | 1<br>1<br>1<br>1      | 1<br>1<br>0<br>1 | 1<br>0      | 0      | 0<br>1      | 0<br>1<br>0<br>1 | 0<br>1<br>0<br>1      |

| S<br>B2        | 0           | 1<br>1<br>0 | 1<br>1<br>0 | 1<br>0<br>0 | 0           | 0           | 1                | 1<br>0<br>1 | 1<br>0<br>1 | 1      | 1<br>0<br>1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>0 | 1                | 1<br>1<br>1      | $\begin{array}{c} 1 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1 \end{array}$ | $\frac{1}{1}$<br>$\frac{1}{1}$<br>$\frac{1}{0}$ | 1      | 0<br>1<br>1 | 0<br>1<br>1<br>1<br>0 | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1<br>1<br>0 | -                | 1<br>0<br>0 | 0      | 0<br>1      | 1<br>0           | 0<br>1<br>0<br>1<br>0 |

Table 2.1-11a A Minimum-Length (25) Checking Experiment for a CBILBO Latch 1.

| D  | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S  | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| B1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| C  | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| Q1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

Table 2.1-11b A Minimum-Length (26) Checking Experiment for a CBILBO Latch 2.

| D  | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| B2 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| C  | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| Q2 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

### 2.2 Deriving Checking Experiments for Two-State Latches

All latches described in Table 2.1-1 are typically implemented as two-state latches; the flow tables of these latches have only two rows. In this section, special properties of two-state flow tables are analyzed and a method for generating checking experiments for them is developed. This method was used to generate the checking experiments in Tables 2.1-2 through 2.1-11.

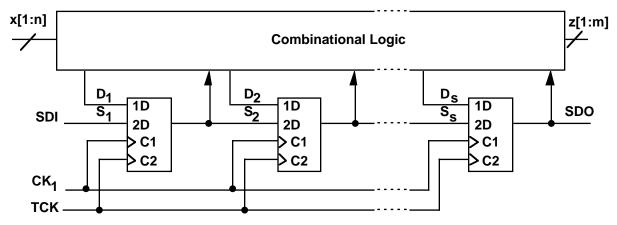

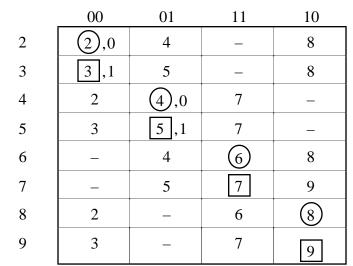

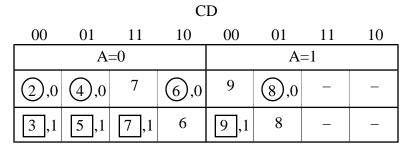

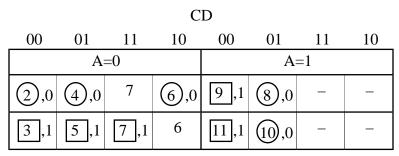

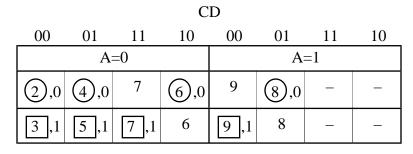

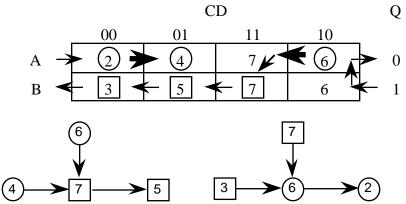

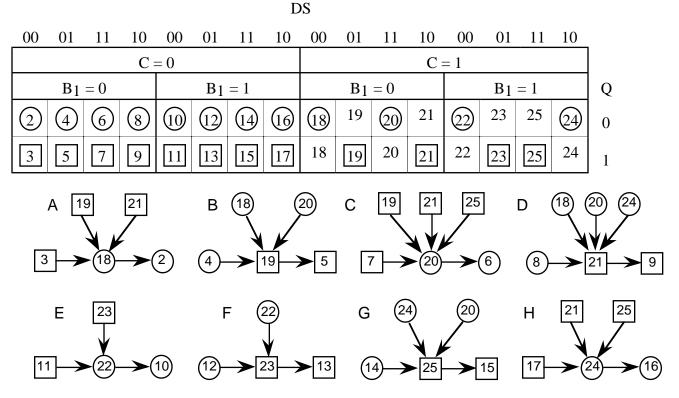

Each cell in a flow table, a *total state*, corresponds to an assignment of values to the circuit inputs and internal states. A total state is an *unstable state* if it causes a change in internal state of the machine. A total state is a *stable state* if the next internal state is the same as the current internal state. In the flow table, a stable state is represented with a number in a circle if its output is 0 and with a number in a square if its output is 1. The numbers of the states start with 2 (0 and 1 are not used to avoid confusion with logic values). For some states the output value may not be observable due to design constraints

(more on this in Section 2.3). For states with observable output, the output value is included after the state. Some total states cannot be reached because of the single-input change restriction on fundamental mode circuits. Such total states are *unspecified states*, and are shown with "–" in the flow tables. A sequence *visits* a total state when the sequence applies the input of the total state while the machine is in the internal state of the total state. A total state is *identified* by a sequence if the sequence provides enough information to reconstruct the corresponding entry in the flow table.