# DESIGN ISSUES IN HIGH PERFORMANCE FLOATING POINT ARITHMETIC UNITS

Stuart Franklin Oberman

Technical Report: CSL-TR-96-711

December 1996

This work was supported by NSF under contract MIP93-13701.

### DESIGN ISSUES IN HIGH PERFORMANCE FLOATING POINT ARITHMETIC UNITS

by Stuart Franklin Oberman **Technical Report: CSL-TR-96-711** December 1996

Computer Systems Laboratory Departments of Electrical Engineering and Computer Science Stanford University Stanford, California 94305-9040

#### Abstract

In recent years computer applications have increased in their computational complexity. The industry-wide usage of performance benchmarks, such as SPECmarks, forces processor designers to pay particular attention to implementation of the floating point unit, or FPU. Special purpose applications, such as high performance graphics rendering systems, have placed further demands on processors. High speed floating point hardware is a requirement to meet these increasing demands. This work examines the state-of-the-art in FPU design and proposes techniques for improving the performance and the performance/area ratio of future FPUs.

In recent FPUs, emphasis has been placed on designing ever-faster adders and multipliers, with division receiving less attention. The design space of FP dividers is large, comprising five different classes of division algorithms: digit recurrence, functional iteration, very high radix, table look-up, and variable latency. While division is an infrequent operation even in floating point intensive applications, it is shown that ignoring its implementation can result in system performance degradation. A high performance FPU requires a fast and efficient adder, multiplier, and divider.

The design question becomes how to best implement the FPU in order to maximize performance given the constraints of silicon die area. The system performance and area impact of functional unit latency is examined for varying instruction issue rates in the context of the SPECfp92 application suite. Performance implications are investigated for shared multiplication hardware, shared square root, on-the-fly rounding and conversion and fused functional units. Due to the importance of low latency FP addition, a variable latency FP addition algorithm has been developed which improves average addition latency by 33% while maintaining single-cycle throughput. To improve the performance and area of linear converging division algorithms, an automated process is proposed for minimizing the complexity of SRT tables. To reduce the average latency of quadratically-converging division algorithms, the technique of reciprocal caching is proposed, along with a method to reduce the latency penalty for exact rounding. A combination of the proposed techniques provides a basis for future high performance floating point units.

Key Words and Phrases: Addition, computer arithmetic, division, floating point, rounding, variable latency

© Copyright 1997 by Stuart Franklin Oberman All Rights Reserved

# Acknowledgments

This work would not have been possible without the help of many wonderful people.

I would like to thank my advisor, Michael Flynn, for all of his technical, financial, and personal support during my years at Stanford. He believed in my abilities from my first day at Stanford, and he has been a source of encouragement ever since.

I would like to thank my other readers Mark Horowitz and Cal Quate for their efforts to review the drafts of this dissertation. Mark Horowitz provided constructive advice and acted as a reality-check for many of my ideas, improving both the content and clarity of this research. Thanks to Martin Morf for the many discussions yielding interesting ideas.

Thanks to Nhon Quach and Grant McFarland. I learned many of the "tricks" of fast floating point from Nhon Quach, and these have influenced the direction of this research. Grant McFarland was always there to discuss a new idea or to read a draft of a paper. Thanks to the other members of Professor Flynn's group for their comments and discussions: Kevin Nowka, Hesham Altwaijry, Dan Zucker, Kevin Rudd, and Steve Fu. Thanks also to the skeptics in the group who kept me honest and often understood the subjects better than I: Gary Bewick, Andrew Zimmerman, Brian Flachs, and John Johnson.

I extend sincere gratitude to my family. To my loving wife, Joy, who sacrificed a more comfortable living, helped support us, and ultimately helped drive me to the completion of this work. To my mother, father, and sister who have always been a tremendous source of encouragement, confidence, and love. This dissertation is dedicated to them.

# Contents

## Acknowledgments

| 1        | Inti | oduct                   | ion                                | 1  |

|----------|------|-------------------------|------------------------------------|----|

|          | 1.1  | Backg                   | ground                             | 1  |

|          | 1.2  | Design                  | n Space                            | 2  |

|          | 1.3  | Arith                   | metic Operations                   | 3  |

|          | 1.4  | Organ                   | nization                           | 4  |

| <b>2</b> | A S  | ystem                   | Perspective                        | 6  |

|          | 2.1  | Introd                  | luction                            | 6  |

|          | 2.2  | Syster                  | m Level Study                      | 7  |

|          |      | 2.2.1                   | Instrumentation                    | 7  |

|          |      | 2.2.2                   | Method of Analysis                 | 8  |

|          | 2.3  | $\operatorname{Result}$ | ts                                 | 9  |

|          |      | 2.3.1                   | Instruction Mix                    | 9  |

|          |      | 2.3.2                   | Compiler Effects                   | 11 |

|          |      | 2.3.3                   | Performance and Area Tradeoffs     | 11 |

|          |      | 2.3.4                   | Shared Multiplier Effects          | 17 |

|          |      | 2.3.5                   | Shared Square Root                 | 19 |

|          |      | 2.3.6                   | On-the-fly Rounding and Conversion | 19 |

|          |      | 2.3.7                   | Consumers of Division Results      | 21 |

|          | 2.4  | Summ                    | nary                               | 23 |

iii

| 3 | Fas | ter FP Addition                        | <b>2</b> |

|---|-----|----------------------------------------|----------|

|   | 3.1 | Introduction                           | . 2      |

|   | 3.2 | FP Addition Algorithms                 | . 2      |

|   |     | 3.2.1 Basic                            | . 2      |

|   |     | 3.2.2 Two-Path                         | . 2      |

|   |     | 3.2.3 Pipelining                       | . 2      |

|   |     | 3.2.4 Combined Rounding                | . 3      |

|   | 3.3 | Variable Latency Algorithm             | . 3      |

|   |     | 3.3.1 Two Cycle                        | . 3      |

|   |     | 3.3.2 One Cycle                        | . 3      |

|   | 3.4 | Performance Results                    | . 3      |

|   | 3.5 | Summary                                | . 4      |

|   | ъ.  |                                        |          |

| 4 |     | ision Algorithms                       | 4        |

|   | 4.1 | Introduction                           |          |

|   | 4.2 | Digit Recurrence Algorithms            |          |

|   |     | 4.2.1 Definitions                      |          |

|   |     | 4.2.2 Implementation of Basic Scheme   |          |

|   |     | 4.2.3 Increasing Performance           |          |

|   |     | 4.2.4 Quotient Conversion              |          |

|   |     | 4.2.5 Rounding                         |          |

|   | 4.3 | Functional Iteration                   |          |

|   |     | 4.3.1 Newton-Raphson                   |          |

|   |     | 4.3.2 Series Expansion                 |          |

|   | 4.4 | Very High Radix Algorithms             | . 6      |

|   |     | 4.4.1 Accurate Quotient Approximations | . 6      |

|   |     | 4.4.2 Short Reciprocal                 | . 7      |

|   |     | 4.4.3 Rounding and Prescaling          | . 7      |

|   | 4.5 | Look-up Tables                         | . 7      |

|   |     | 4.5.1 Direct Approximations            | . 7      |

|   |     | 4.5.2 Linear Approximations            | . 7      |

# vi

|                                   | 4.5.3                                                                                                                                                      | Partial Product Arrays                                                                                                                                                                                                                                                                   |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.6                               | Variab                                                                                                                                                     | ble Latency Algorithms                                                                                                                                                                                                                                                                   |

|                                   | 4.6.1                                                                                                                                                      | Self-Timing 81                                                                                                                                                                                                                                                                           |

|                                   | 4.6.2                                                                                                                                                      | Result Caches                                                                                                                                                                                                                                                                            |

|                                   | 4.6.3                                                                                                                                                      | Speculation of Quotient Digits                                                                                                                                                                                                                                                           |

| 4.7                               | Comp                                                                                                                                                       | arison                                                                                                                                                                                                                                                                                   |

| 4.8                               | Summ                                                                                                                                                       | ary                                                                                                                                                                                                                                                                                      |

| Fast                              | ter SR'                                                                                                                                                    | T Dividers 91                                                                                                                                                                                                                                                                            |

| 5.1                               | Introd                                                                                                                                                     | uction                                                                                                                                                                                                                                                                                   |

| 5.2                               | SRT I                                                                                                                                                      | Division                                                                                                                                                                                                                                                                                 |

| 5.3                               | Implei                                                                                                                                                     | menting SRT Tables                                                                                                                                                                                                                                                                       |

|                                   | 5.3.1                                                                                                                                                      | Divisor and Partial Remainder Estimates                                                                                                                                                                                                                                                  |

|                                   | 5.3.2                                                                                                                                                      | Uncertainty Regions                                                                                                                                                                                                                                                                      |

|                                   | 5.3.3                                                                                                                                                      | Reducing Table Complexity                                                                                                                                                                                                                                                                |

| 5.4                               | Exper                                                                                                                                                      | imental Methodology                                                                                                                                                                                                                                                                      |

|                                   | 5.4.1                                                                                                                                                      | TableGen   98                                                                                                                                                                                                                                                                            |

|                                   | 5.4.2                                                                                                                                                      | Table Synthesis    101                                                                                                                                                                                                                                                                   |

| 5.5                               | Result                                                                                                                                                     | s                                                                                                                                                                                                                                                                                        |

|                                   | 5.5.1                                                                                                                                                      | Same Radix Tradeoffs                                                                                                                                                                                                                                                                     |

|                                   | 5.5.2                                                                                                                                                      | Higher Radix                                                                                                                                                                                                                                                                             |

| 5.6                               | Summ                                                                                                                                                       | ary                                                                                                                                                                                                                                                                                      |

| $\operatorname{Div}$              | ision a                                                                                                                                                    | nd Reciprocal Caches 110                                                                                                                                                                                                                                                                 |

| 6.1                               | Introd                                                                                                                                                     | uction                                                                                                                                                                                                                                                                                   |

|                                   |                                                                                                                                                            |                                                                                                                                                                                                                                                                                          |

| 6.2                               | Recipi                                                                                                                                                     | rocal Caches                                                                                                                                                                                                                                                                             |

| 6.2                               | Recipi<br>6.2.1                                                                                                                                            | rocal Caches                                                                                                                                                                                                                                                                             |

| 6.2                               | 1                                                                                                                                                          | Iterative Division                                                                                                                                                                                                                                                                       |

| 6.2                               | 6.2.1                                                                                                                                                      | Iterative Division111Experimental Methodology112                                                                                                                                                                                                                                         |

| <ul><li>6.2</li><li>6.3</li></ul> | 6.2.1<br>6.2.2<br>6.2.3                                                                                                                                    | Iterative Division111Experimental Methodology112                                                                                                                                                                                                                                         |

|                                   | <ul><li>6.2.1</li><li>6.2.2</li><li>6.2.3</li><li>Division</li></ul>                                                                                       | Iterative Division111Experimental Methodology112Performance112                                                                                                                                                                                                                           |

|                                   | <ul> <li>4.7</li> <li>4.8</li> <li>Fast</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>Div</li> <li>6.1</li> </ul> | 4.6 Variab<br>4.6.1<br>4.6.2<br>4.6.3<br>4.7 Compa<br>4.8 Summ<br>Faster SR'<br>5.1 Introd<br>5.2 SRT I<br>5.3 Implea<br>5.3.1<br>5.3.2<br>5.3 Implea<br>5.3.1<br>5.3.2<br>5.3.3<br>5.4 Experi<br>5.4.1<br>5.4.2<br>5.5 Result<br>5.5.1<br>5.5.2<br>5.6 Summ<br>Division a<br>6.1 Introd |

| <b>7</b> | Fast   | Rounding                                         | 120 |

|----------|--------|--------------------------------------------------|-----|

|          | 7.1    | Introduction                                     | 120 |

|          | 7.2    | IEEE Rounding                                    | 121 |

|          | 7.3    | Division by Functional Iteration                 | 122 |

|          | 7.4    | Previously Implemented Techniques                | 124 |

|          | 7.5    | Reducing the Frequency of Remainder Computations | 126 |

|          |        | 7.5.1 Basic Rounding                             | 126 |

|          |        | 7.5.2 Faster Rounding                            | 130 |

|          |        | 7.5.3 Higher Performance                         | 131 |

|          | 7.6    | Faster Magnitude Comparison                      | 133 |

|          | 7.7    | Summary                                          | 135 |

| 8        | Con    | clusion                                          | 136 |

|          | 8.1    | Summary                                          | 136 |

|          | 8.2    | Future Work                                      | 139 |

| Bi       | ibliog | graphy                                           | 141 |

# viii

# List of Tables

| 2.1 | Effects of compiler optimization                                                                               | 15  |

|-----|----------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Five regions of division latency                                                                               | 17  |

| 4.1 | Summary of algorithms                                                                                          | 86  |

| 4.2 | Latencies for different configurations                                                                         | 88  |

| 5.1 | Gray encoding for maximally redundant radix 4                                                                  | 100 |

| 5.2 | Radix 4 Tradeoffs                                                                                              | 102 |

| 5.3 | Radix 2                                                                                                        | 104 |

| 5.4 | Radix 8                                                                                                        | 105 |

| 5.5 | Radix 16                                                                                                       | 106 |

| 5.6 | Radix 32                                                                                                       | 107 |

| 6.1 | Performance/area tradeoffs for reciprocal caches $\ldots \ldots \ldots \ldots$                                 | 114 |

| 7.1 | Action table for RN rounding mode                                                                              | 122 |

| 7.2 | Action table for basic method $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 128 |

| 7.3 | Action table using two guard bits                                                                              | 132 |

| 7.4 | Sign prediction                                                                                                | 134 |

# List of Figures

| 2.1  | Instruction mix                                                                                           | 10 |

|------|-----------------------------------------------------------------------------------------------------------|----|

| 2.2  | Functional unit stall time distribution                                                                   | 10 |

| 2.3  | Spice with optimization O0 $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 12 |

| 2.4  | Spice with optimization O3 $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$        | 12 |

| 2.5  | Interlock distances: by application and cumulative average $\ldots$ .                                     | 13 |

| 2.6  | Cumulative average add and mul interlock distances                                                        | 13 |

| 2.7  | CPI and area vs division latency - low latency $\ldots \ldots \ldots \ldots$                              | 14 |

| 2.8  | CPI and area vs division latency - full range                                                             | 16 |

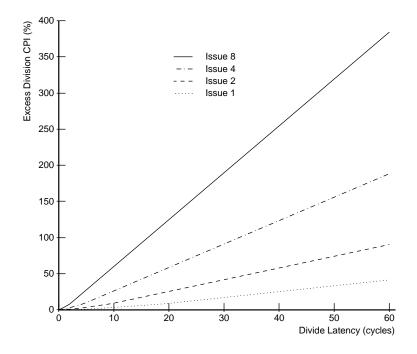

| 2.9  | Excess CPI as a percentage of base CPI for multiple issue processors                                      | 18 |

| 2.10 | Excess CPI due to shared multiplier                                                                       | 18 |

| 2.11 | Effects of on-the-fly rounding and conversion                                                             | 20 |

| 2.12 | Consumers of division results                                                                             | 22 |

| 2.13 | Consumers of multiply results                                                                             | 22 |

| 3.1  | Two path algorithm                                                                                        | 29 |

| 3.2  | Three cycle pipelined adder with combined rounding $\ldots$                                               | 31 |

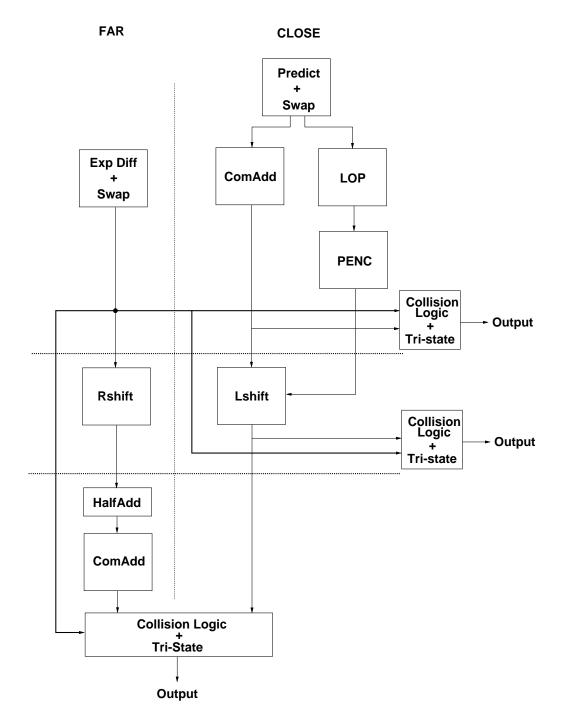

| 3.3  | Two or three cycle variable latency adder                                                                 | 34 |

| 3.4  | One, two, or three cycle variable latency adder                                                           | 36 |

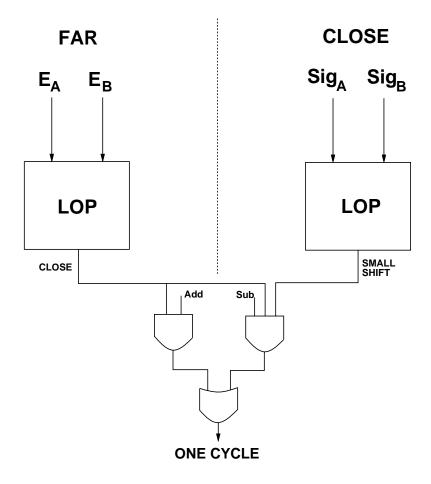

| 3.5  | Additional hardware for one cycle operation prediction $\ldots$                                           | 37 |

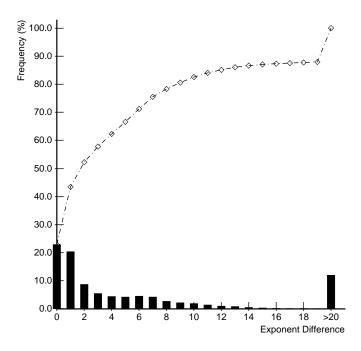

| 3.6  | Histogram of exponent difference                                                                          | 39 |

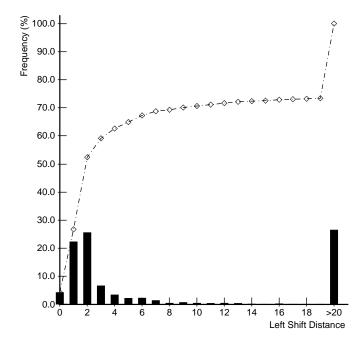

| 3.7  | Histogram of normalizing shift distance                                                                   | 39 |

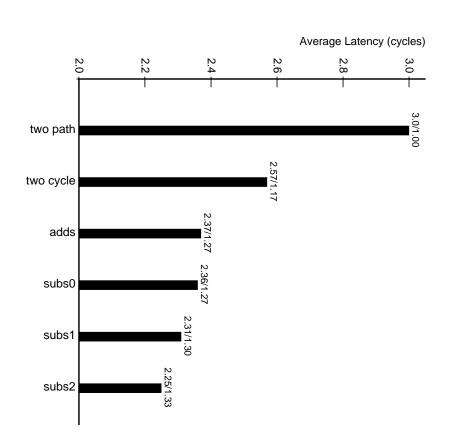

| 3.8  | Performance summary of proposed techniques                                                                | 41 |

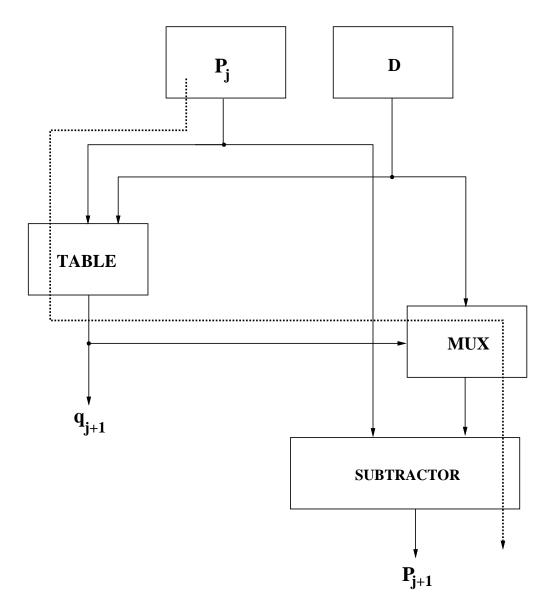

| 4.1  | Basic SRT Divider Topology                                                                                | 47 |

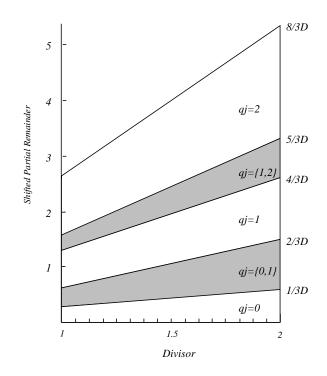

| 4.2 | P-D diagram for radix-4                                                                  | 50  |

|-----|------------------------------------------------------------------------------------------|-----|

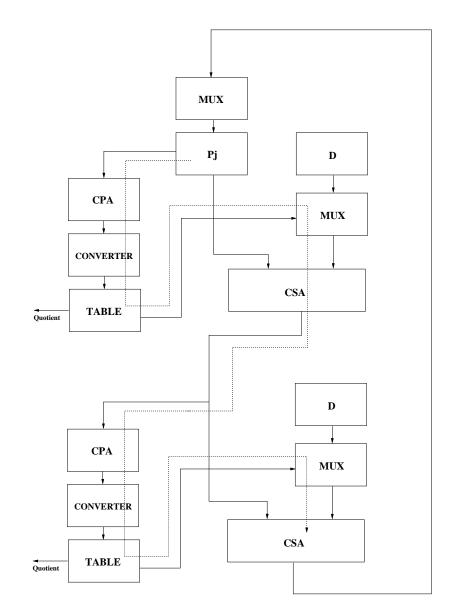

| 4.3 | Higher radix using hardware replication                                                  | 53  |

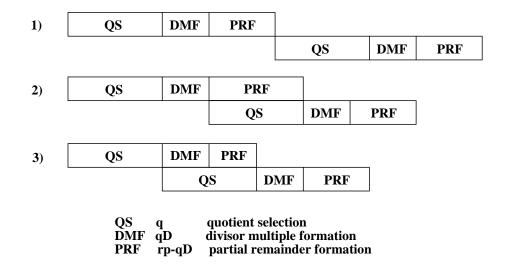

| 4.4 | Three methods of overlapping division components $\ldots \ldots \ldots$                  | 54  |

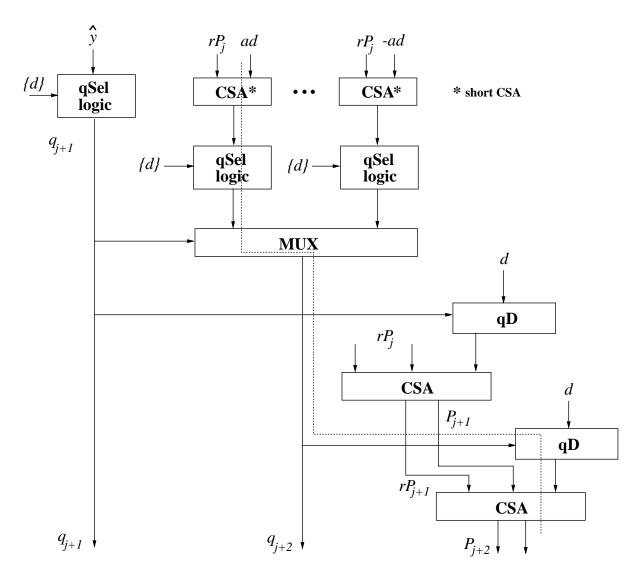

| 4.5 | Higher radix by overlapping quotient selection                                           | 56  |

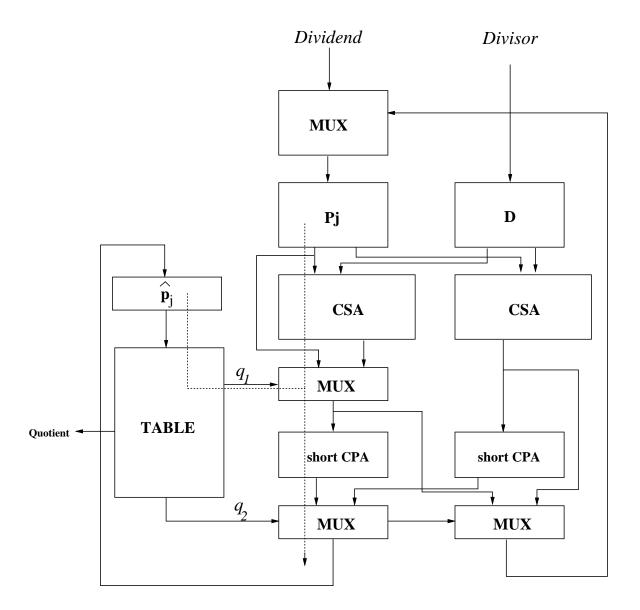

| 4.6 | Radix-4 with overlapped remainder computation                                            | 58  |

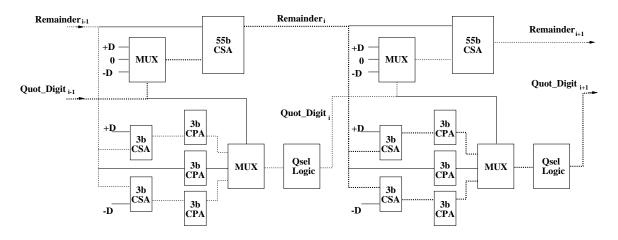

| 4.7 | Two stages of self-timed divider                                                         | 81  |

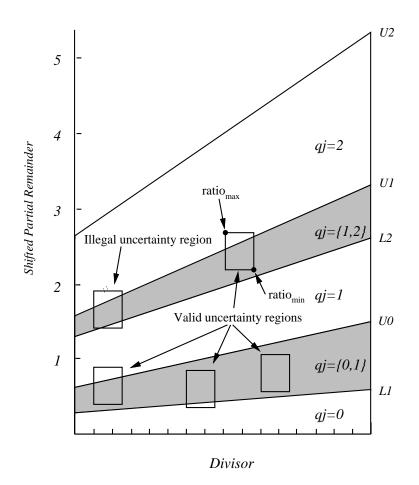

| 5.1 | Uncertainty regions due to divisor and partial remainder estimates                       | 96  |

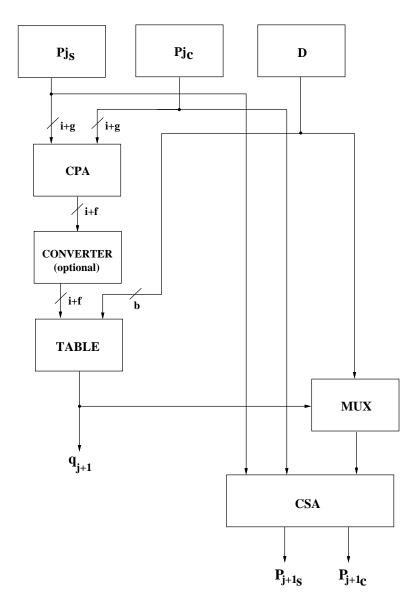

| 5.2 | Components of an SRT divider                                                             | 99  |

| 5.3 | Design flow                                                                              | 100 |

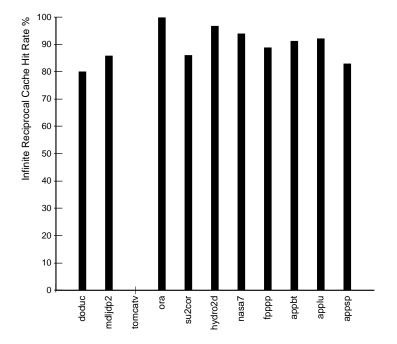

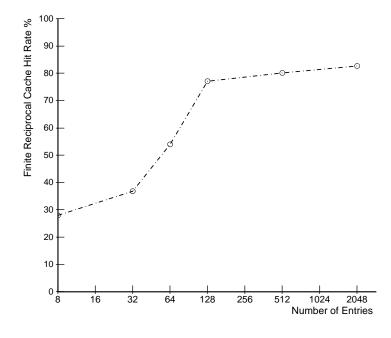

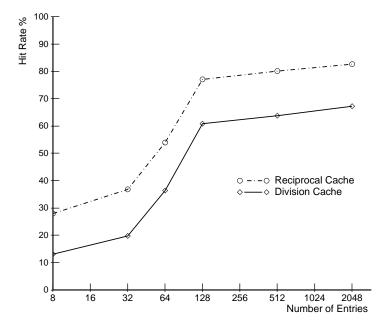

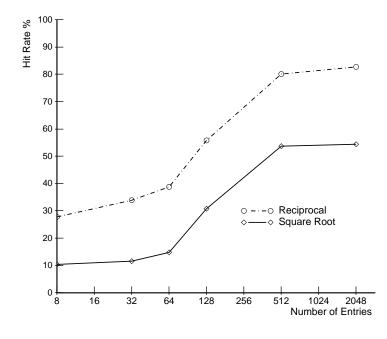

| 6.1 | Hit rates for infinite reciprocal caches                                                 | 113 |

| 6.2 | Hit rates for finite reciprocal caches                                                   | 113 |

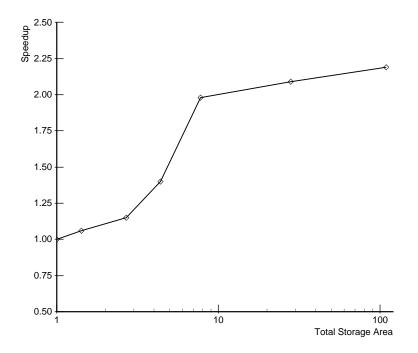

| 6.3 | Speedup from reciprocal caches $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 115 |

| 6.4 | Hit rates for division caches                                                            | 118 |

| 6.5 | Hit rates for reciprocal/square root caches                                              | 118 |

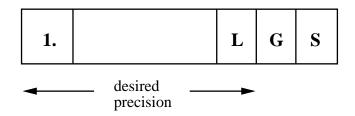

| 7.1 | Significand format before rounding                                                       | 121 |

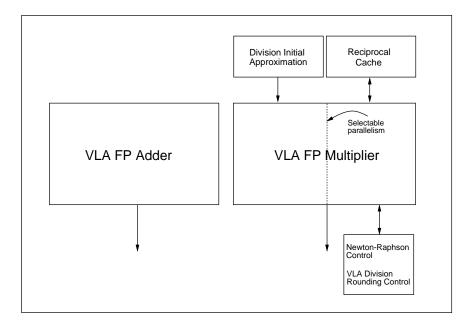

| 8.1 | Example FPU implementation                                                               | 139 |

# Chapter 1

# Introduction

### 1.1 Background

A floating point number representation can simultaneously provide a large range of numbers and a high degree of precision. As a result, a portion of modern microprocessors is often dedicated to hardware for floating point computation. Previously, silicon area constraints have limited the complexity of the floating point unit, or FPU. Advances in integrated circuit fabrication technology have resulted in both smaller feature sizes and increased die areas. Together, these trends have provided a larger transistor budget to the processor designer. It has therefore become possible to implement more sophisticated arithmetic algorithms to achieve higher FPU performance.

Due to the complexity of floating point number systems, hardware implementations of floating point operations are typically slower than integer operations. Many modern computer programs, such as scientific computation, 3D graphics applications, digital signal processing, and system performance benchmarks have a high frequency of floating point operations. The performance of these applications is often limited by the speed of the floating point hardware. For these reasons, high performance FPUs are now both practical and desirable.

The IEEE 754 floating point standard [1] is the most common floating point representation used in modern microprocessors. It dictates the precisions, accuracy, and arithmetic operations that must be implemented in conforming processors. The arithmetic operations include addition, multiplication, division, and square root. The design of a high performance IEEE conforming FPU requires a fast adder, multiplier, divider, and square root unit. This research therefore investigates algorithms and implementations for designing high performance IEEE conforming floating point units.

## 1.2 Design Space

The performance and area of a functional unit depend upon circuit style, logic implementation, and choice of algorithms. The space of current circuit styles ranges from fully-static CMOS designs to hand-optimized self-timed dynamic circuits. Logic design styles range from automatically-synthesized random logic to custom, handselected gates. The widest selection of design choices is available at the algorithmic level, which is the focus of this dissertation.

The three primary parameters in FP functional unit design are latency, cycle time, and area. The functional unit latency is the time required to complete a computation, typically measured in machine cycles. Designs can be either *Fixed Latency (FL)* or Variable Latency (VL). In a FL design, each step of the computation completes in lock-step with a system clock. Further, any given operation completes after a fixed quantity of cycles. The cycle time in a FL design is the maximum time between the input of operands from registers and the latching of new results into the next set of registers. In contrast, VL designs complete after a variable quantity of cycles. This allows a result to be returned possibly sooner than the maximum latency, reducing the average latency. They achieve their variability through either the choice of algorithm (VLA) or choice of circuit design (VLC). VLA designs operate in synchronization with a system clock. However, the total number of cycles required to complete the operation varies depending upon other factors, such as the actual values of the input operands. An example of a non-floating point VLA design is a hierarchical memory system. In such a memory system, the total latency for a LOAD operation depends upon the level in the hierarchy at which the requested data resides. VLC designs need not have any internal synchronization with the rest of the system. Instead, such a design accepts new inputs at one time, and it produces results sometime later, independent of the system clock. A self-timed circuit is an example of a VLC design. Self-timed designs use special circuits to allow for results to be generated as soon as they are available. While self-timed designs reduce the average latency, they often introduce additional complexity, including additional testing requirements and integration issues with synchronous designs.

FL designs can be fully combinational or pipelined. Pipelining is a commonly used technique for increasing the throughput of functional units. A functional unit can be divided into smaller components by introducing explicit registers in-between the components. In this way, the cycle time of the unit becomes the maximum time for any of the components to complete. By increasing the number of components, the cycle time of the unit is decreased at the expense of increasing the latency. The primary motivation for pipelining is to allow for one operation to be initiated and another to be completed in each machine cycle, with more than one operation in progress at any time. As a result, the total latency for a sequence of operations is reduced by exploiting the component-level parallelism. However, the introduction of additional registers to hold the intermediate values contributes overhead in the form of longer cycle times and area. These tradeoffs must be understood for optimal FL and VLA functional unit design.

## **1.3** Arithmetic Operations

The most frequent FP operation is addition. Conceptually, it is the simplest operation, returning either the sum or difference of two FP numbers. In practice, FP adders can be slow due to additional aligning and normalizing shifts, recomplementation, and rounding that may be required. A fast FP adder is vital to the performance of an FPU, and thus techniques to reduce the latency of FP addition are investigated in this dissertation.

Multiplication is typically the next-most frequent FP operation. As a result, high-speed multiplication is also critical to a high performance FPU. Multiplication involves the summation of several shifted partial products, each of which is a product of the multiplicand and one digit of the multiplier. Thus, three steps are required in multiplication: partial product generation, partial product reduction, and final carry-propagate-addition. In practice, the partial products may be formed by direct ANDing of the multiplier digit and the multiplicand, or they may be formed by one of many bit scanning algorithms such as Booth's Algorithm [2]. The partial product reduction is implemented by a series of carry-free adders, which are connected in one of many different topologies ranging from linear arrays to logarithmic trees. The organization of these reduction trees has been the subject of previous research, much of which is summarized in [3], [4], [5], and [6]. The final carry-propagate-addition is an application of integer addition, a topic independent from FPU design [7]. The remaining tradeoffs in multiplier design are: method of partial product generation, topology and circuit design of the reduction tree, and the topology and circuit design of the final carry-propagate adder. These tradeoffs involve the analysis of the delay and area of the specific circuits and layouts in a given technology. As this dissertation focuses primarily on algorithmic tradeoffs in functional unit design, an analysis of the area and performance tradeoffs of FP multipliers is not presented here. Some of these tradeoffs are presented in Al-Twaijry [3].

The least frequently occurring operations in an IEEE FPU are division and square root. However, a slow divider implementation in a high performance FPU can result in performance degradation. The theory of square root computation is very similar to that of division, and thus much of the analysis for division can also be applied to square root units. As the design space of division algorithms and implementations is much larger than that of addition and multiplication, a considerable portion of this dissertation is dedicated to analysis and algorithms for divider design.

### 1.4 Organization

The following chapters detail design issues in FPU design, a VLA algorithm for higher performance FP addition, a taxonomy of division algorithms, and several FL and VL techniques for increasing FP division performance.

Chapter 2 examines the system performance impact of functional unit latencies. It also examines the performance implications of shared multiplication hardware, shared square root, on-the-fly rounding and conversion, and fused functional units. This chapter forms a basis for the FPU performance requirements from a system perspective, and it demonstrates the importance of a lower latency FP divider.

Chapter 3 presents a case study demonstrating the use of a variable latency functional unit to achieve maximum performance. The study proposes a new floating point addition algorithm which reduces the average addition latency while maintaining single cycle throughput. This algorithm achieves higher performance by exploiting the distribution of FP addition operands.

Chapter 4 presents five major classes of division algorithms in order to clarify the design space of division algorithms and implementations. It analyzes the fundamental design tradeoffs in terms of latency, cycle time, and area.

Chapter 5 analyzes in more detail techniques to minimize the complexity of quotient-digit selection tables in SRT division implementations. The quotient-digit selection function is often the major contributor to the cycle time of SRT dividers. By minimizing the delay and area of the quotient-digit selection tables, the performance and area of the overall divider implementation is improved.

Chapter 6 presents two variable latency methods for reducing average division latency: division and reciprocal caches.

Chapter 7 clarifies the methodology for correct IEEE compliant rounding for quadratically-converging division algorithms and proposes techniques to reduce the latency penalty for exact rounding.

Chapter 8 summarizes the results of this research and suggests further areas of floating point research.

# Chapter 2

# A System Perspective

### 2.1 Introduction

In recent FPUs emphasis has been placed on designing ever-faster adders and multipliers, with division and square root receiving less attention. The typical range for addition latency is 2 to 4 cycles, and the range for multiplication is 2 to 8 cycles. In contrast, the latency for double precision division ranges from 6 to 61 cycles, and square root is often far larger [8]. Most emphasis has been placed on improving the performance of addition and multiplication. As the performance gap widened between these two operations and division, floating point algorithms and applications have been slowly rewritten to account for this gap by mitigating the use of division. Thus, current applications and benchmarks are usually written assuming that division is an inherently slow operation and should be used sparingly.

This chapter investigates in detail the relationship between FP functional unit latencies and system performance. The application suites considered for this study included the NAS Parallel Benchmarks [9], the Perfect Benchmarks [10], and the SPECfp92 [11] benchmark suite. An initial analysis of the instruction distribution determined that the SPEC benchmarks had the highest frequency of floating point operations, and they were therefore chosen as the target workload of the study to best reflect the behavior of floating point intensive applications. These applications are used to investigate several questions regarding the implementation of floating point units [12]:

- Does a high-latency division/square root operation cause enough system performance degradation to justify dedicated hardware support?

- How well can a compiler schedule code in order to maximize the distance between floating point result production and consumption?

- What are the effects of increasing the width of instruction issue on effective division latency?

- If hardware support for division and square root unit is warranted and a multiplicationbased algorithm is utilized, should the FP multiplier hardware be shared, or should a dedicated functional unit be designed?

- Should square root share the division hardware?

- What operations most frequently consume division results?

- Is on-the-fly rounding and conversion necessary?

The organization of this chapter is as follows. Section 2 describes the method of obtaining data from the applications. Section 3 presents the results of the study. Section 4 analyzes and summarizes the results.

## 2.2 System Level Study

### 2.2.1 Instrumentation

System performance was evaluated using 11 applications from the SPECfp92 benchmark suite. The applications were each compiled on a DECstation 5000 using the MIPS C and Fortran compilers at each of three levels of optimization: no optimization, O2 optimization, and O3 optimization. O2 performs common subexpression elimination, code motion, strength reduction, code scheduling, and inlining of arithmetic statement functions. O3 performs all of O2's optimizations, but it also implements loop unrolling and other code-size increasing optimizations [13]. Among other things, varying the level of compiler optimization varies the total number of executed instructions and the distance between a division operation and the use of its result. The compilers utilized the MIPS R3000 machine model for all schedules assuming double precision FP latencies of 2 cycles for addition, 5 cycles for multiplication, and 19 cycles for division.

In most traditional computer architectures, a close match exists between highlevel-language semantics and machine-level instructions for floating point operations [14]. Thus, the results obtained on a given architecture are applicable to a wide range of architectures. The results presented were obtained on the MIPS architecture, primarily due to the availability of the flexible program analysis tools pixie and pixstats [15]. Pixie reads an executable file and partitions the program into its basic blocks. It then writes a new version of the executable containing extra instructions to dynamically count the number of times each basic block is executed. The benchmarks use the standard input data sets, and each executes approximately 3 billion instructions. Pixstats is then used to extract performance statistics from the instrumented applications.

### 2.2.2 Method of Analysis

To determine the effects of a floating point operation on overall system performance, the performance degradation due to the operation needs to be determined. This degradation can be expressed in terms of excess CPI, or the CPI due to the result interlock. Excess CPI is a function of the dynamic frequency of the operation, the urgency of its results, and the functional unit latency. The dynamic frequency of an operation is the number of times that a particular operation is executed in the application. The urgency of a result is measured by how soon a subsequent instruction needs to consume the result. To quantify the urgency of results, interlock distances were measured for division results. The interlock distance is the distance between the production of a division result and its consumption by a subsequent instruction. It is clear that the dynamic frequency is solely a function of the application, urgency is a function of the application and the compiler, and functional unit latency depends upon the hardware implementation. The system designer has the most control over the functional unit latency. Through careful design of the processor architecture, though, the designer has some limited influence on the urgency. Adding extra registers and providing for out-of-order instruction execution are two means by which the system designer can influence urgency.

### 2.3 Results

#### 2.3.1 Instruction Mix

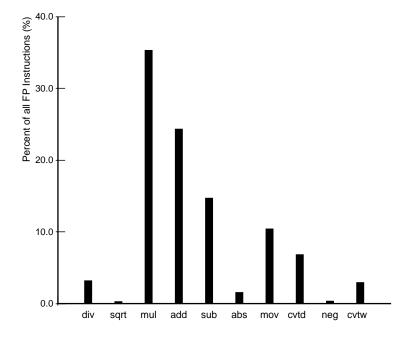

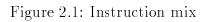

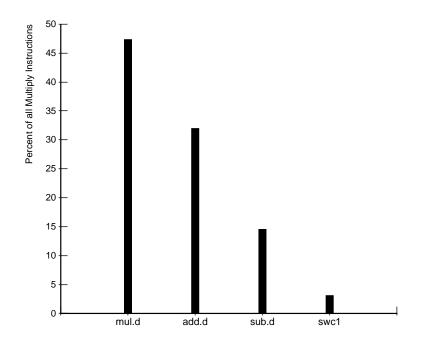

Figure 2.1 shows the average frequency of division and square root operations in the benchmark suite relative to the total number of floating point operations, where the applications have been compiled using O3 optimization. This figure shows that simply in terms of dynamic frequency, division and square root seem to be relatively unimportant instructions, with about 3% of the dynamic floating point instruction count due to division and only 0.33% due to square root. The most common instructions are FP multiply and add, but note that add, subtract, move, and convert operations typically use the FP adder hardware. Thus, FP multiply accounts for 37% of the instructions, and the FP adder is used for 55% of the instructions. However, in terms of latency, division can play a much larger role. By assuming a machine model of a scalar processor, where every division operation has a latency of 20 cycles and the adder and multiplier each have a 3 cycle latency, a distribution of the excess CPI due to FP stall time was formed, shown in figure 2.2. The stall time is the period during which the processor was ready to execute the next instruction, but an interlock on the result of a previous unfinished FP add, multiply, or divide instruction prevented it from continuing. This excess CPI reduces overall performance by increasing the total CPI. Here, FP division accounts for 40% of the performance degradation, FP add accounts for 42%, and multiply accounts for the remaining 18%. Therefore, the performance of division is significant to the overall system performance.

Figure 2.2: Functional unit stall time distribution

#### 2.3.2 Compiler Effects

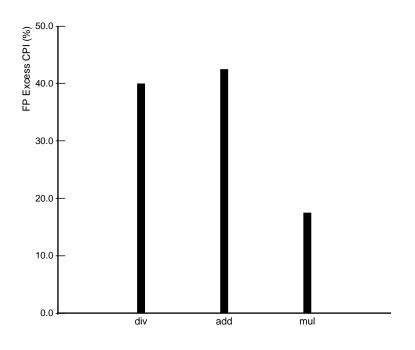

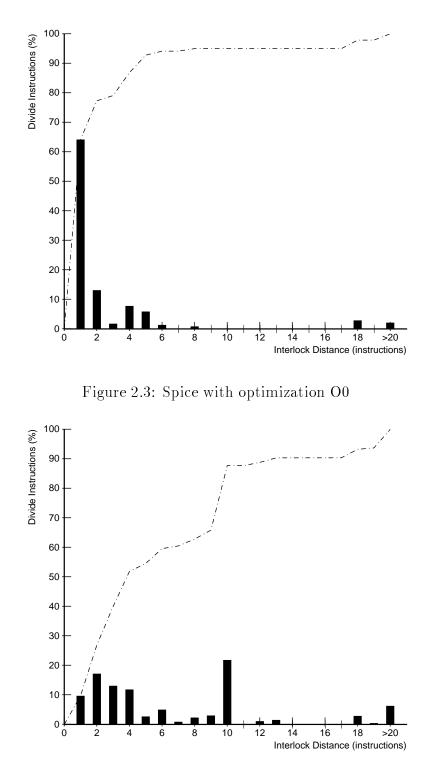

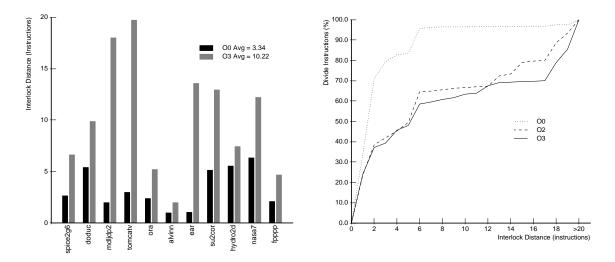

In order to analyze the impact that the compiler can have on improving system performance, the urgency of division results was measured as a function of compiler optimization level. Figure 2.3 shows a histogram of the interlock distances for division instructions at O0, as well as a graph of the cumulative interlock distance for the spice benchmark. Figure 2.4 shows the same data when compiled at O3. Figure 2.5 shows the average interlock distances for all of the applications at both O0 and O3 levels of optimization. By intelligent scheduling and loop unrolling, the compiler is able to expose instruction-level parallelism in the applications, decreasing the urgency of division results. Figure 2.5 shows that the average interlock distance can be increased by a factor of three by compiler optimization.

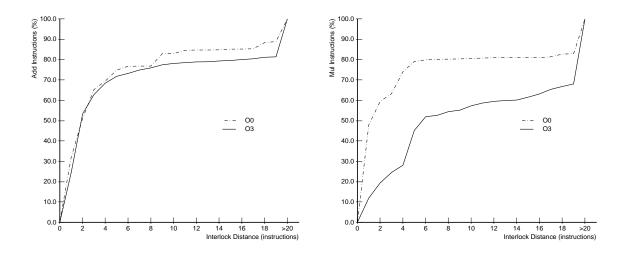

An average of the division interlock distances from all of the benchmarks was formed, weighted by division frequency in each benchmark. This result is also shown in figure 2.5 for the three levels of compiler optimization. In this graph, the curves represent the cumulative percentage of division instructions at each distance. The results from figure 2.5 show that the average interlock distance can be increased to only approximately 10 instructions. Even if the compiler assumed a larger latency, there is little parallelism left to exploit that could further increase the interlock distance and therefore reduce excess CPI. If the compiler scheduled assuming a low latency, the excess CPI could only increase for dividers with higher latencies than that for which the compiler scheduled. This is because the data shows the maximum parallelism available when scheduling for a latency of 19 cycles. If the compiler scheduled for a latency much less than 19 cycles, then it would not be as aggressive in its scheduling, and the interlock distances would be smaller, increasing urgency and therefore excess CPI. The results for division can be compared with those of addition and multiplication, shown in figure 2.6.

### 2.3.3 Performance and Area Tradeoffs

The excess CPI due to division is determined by summing all of the stall cycles due to division interlocks, which is the total penalty, and dividing this quantity by the

Figure 2.4: Spice with optimization O3

Figure 2.5: Interlock distances: by application and cumulative average

Figure 2.6: Cumulative average add and mul interlock distances

Figure 2.7: CPI and area vs division latency - low latency

total number of instructions executed, as shown in equation 2.1.

$$CPI_{div} = \frac{\sum \text{stall time}}{\text{total instructions}}$$

(2.1)

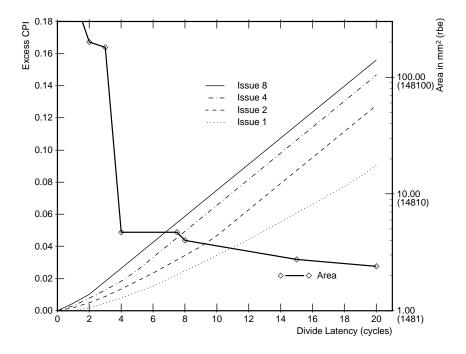

The performance degradation due to division latency is displayed in figure 2.7. This graph shows how the excess CPI due to the division interlocks varies with division unit latency between 1 and 20 cycles for O3 optimization. Varying the optimization level also changed the total number of instructions executed, but left the number of division instructions executed constant. As a result, the fraction of division instructions is also a function of optimization level. While CPI due to division actually increases from O0 to O2, the overall performance at O2 and O3 increases because the total instruction count decreases. This effect is summarized in table 2.1, where the division latency is taken to be 20 cycles.

Figure 2.7 also shows the effect of increasing the number of instructions issued per cycle on excess CPI due to division. To determine the effect of varying instruction issue rate on excess CPI due to division, a model of an underlying architecture must

| Opt Level | Div Freq | Excess CPI |

|-----------|----------|------------|

| 00        | 0.33%    | 0.057      |

| O2        | 0.76%    | 0.093      |

| O3        | 0.79%    | 0.091      |

Table 2.1: Effects of compiler optimization

be assumed. In this study, an optimal superscalar processor is assumed, such that the maximum issue rate is sustainable. This model simplifies the analysis while providing an upper bound on the performance degradation due to division. The issue rate is used to appropriately reduce the interlock distances. As the width of instruction issue increases, urgency of division data increases proportionally. In the worst case, every division result consumer could cause a stall equal to the functional unit latency. The excess CPI for the multiple issue processors is then calculated using the new interlock distances.

Figure 2.7 also shows how area increases as the functional unit latency decreases. The estimation of area is based on reported layouts from [16], [17], [18], all of which have been normalized to  $1.0\mu$ m scalable CMOS layout rules. As division latencies decrease below 4 cycles, a large tradeoff must be made. Either a very large area penalty must be incurred to achieve this latency by utilizing a very high radix division algorithm, or large cycle times may result if an SRT divider is utilized. Several classes of division algorithms, including very high radix division, Newton-Raphson, and SRT division are examined in more detail in chapter 4.

In order to make the comparison of chip areas technology independent, the register bit equivalent (**rbe**) area model of Mulder [19] was used. In this model, one **rbe** equals the area of a one bit storage cell. For the purposes of this study, an **rbe** unit is referenced to a six-transistor static cell with high bandwidth, with an area of  $675f^2$ , where f is the minimum feature size. The area required for 1 static RAM bit, as would be used used in an on-chip cache, is about 0.6 **rbe**. Since all areas are normalized to an  $f = 1.0 \mu m$  process,  $1 mm^2 = 1481$  **rbe**.

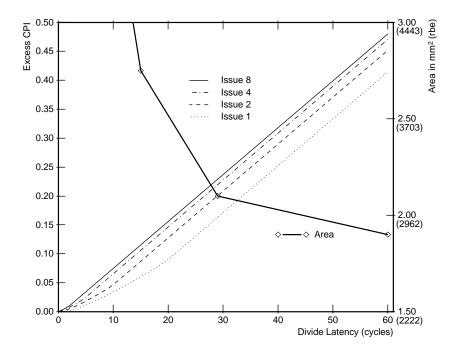

Figure 2.8 shows excess CPI versus division latency over a larger range of latencies.

Figure 2.8: CPI and area vs division latency - full range

This graph can roughly be divided into five regions. Table 2.2 shows that inexpensive 1-bit SRT schemes use little area but can contribute in the worst case up to 0.50 CPI in wide-issue machines. Increasing the radix of SRT implementations involves an increase in area, but with a decrease in excess CPI. The region corresponding to 4-bit SRT schemes also represents the performance of typical multiplication-based division implementations, such as Newton-Raphson or series expansion [20]. The additional area required in such implementations is difficult to quantify, as implementations to date have shared existing multipliers, adding control hardware to allow for the shared functionality. At a minimum, such implementations require a starting approximation table that provides at least an 8 bit initial approximation. Such a table occupies a minimum of 2 Kbits, or 1230 rbe. The final region consists of very-high radix dividers of the form presented in [18] and [21]. To achieve this performance with CPI < 0.01, large area is required for very large look-up tables, often over 500,000 rbe.

To better understand the effects of division latency on the system performance of

| Divider Type  | Latency (cycles) | Excess CPI    | Area (rbe) |

|---------------|------------------|---------------|------------|

| 1-Bit SRT     | > 40             | < 0.5         | < 3000     |

| 2-Bit SRT     | [20, 40]         | [0.10,  0.32] | 3110       |

| 4-Bit SRT     | [10, 20]         | [0.04,  0.10] | 4070       |

| 8-Bit SRT and | [4, 10]          | [0.01,  0.07] | 6665       |

| Self-Timed    |                  |               |            |

| Very-High     | < 4              | < 0.01        | > 100,000  |

| Radix         |                  |               |            |

Table 2.2: Five regions of division latency

multiple issue processors, the excess CPI due to division can be expressed as a percentage of the base processor CPI. Figure 2.9 shows this relationship quantitatively. As instruction width increases, the degradation of system performance markedly increases. Not only does increasing the width of instruction issue reduce the average interlock distance, but the penalty for a division interlock relative to the processor issue rate dramatically increases. A slow divider in a wide-issue processor can easily reduce system performance by half.

### 2.3.4 Shared Multiplier Effects

If a multiplication-based division algorithm is chosen, such as Newton-Raphson or series expansion, it must be decided whether to use a dedicated multiplier or to share the existing multiplier hardware. The area of a well-designed 3 cycle FP multiplier is around 11 mm<sup>2</sup>, again using the 1.0 $\mu$ m process. Adding this much area may not be always desirable. If an existing multiplier is shared, this has two effects. First, the latency through the multiplier likely increases due to the modifications necessary to support the division operation. Second, multiply operations may be stalled due to conflicts with division operations sharing the multiplier.

The effect of this on excess CPI is shown in figure 2.10. The results are based on an average of all of the applications when scheduled with O3. In all cases for a division latency less than 20 cycles, the excess CPI is less than 0.07. For reasonable

Figure 2.9: Excess CPI as a percentage of base CPI for multiple issue processors

Figure 2.10: Excess CPI due to shared multiplier

implementations of multiplication-based division, with a latency of approximately 13 cycles, the actual penalty is 0.02 < CPI < 0.04. For these applications, the penalty incurred for sharing an existing multiplier is not large due to the relatively low frequency of division operations. For special classes of applications, such as certain graphics applications, division and multiplication frequencies could be higher, requiring a separate division unit to achieve high performance.

#### 2.3.5 Shared Square Root

The recurrence equation for square root is very close in form to that of division for both subtractive and multiplicative algorithms. Accordingly, division hardware can be implemented with additional functionality to perform square root computation. The design tradeoff then becomes whether a possible increase in hardware complexity and/or cycle time can be justified by an increase in overall performance.

The results of this study show that floating point square root on the average accounts for 0.087% of all executed instructions. This is a factor of 9.1 less than division. To avoid significant performance degradation due to square root, the latency of square root should be no worse than a factor 9.1 greater than division. However, any hardware implementation of square root more than likely meets this requirement. Even a simple 1 bit per iteration square root would contribute only 0.05 CPI for a scalar processor. Accordingly, these results suggest that the square root implementation does not need to have the same performance as the divider, and the sharing of division hardware is not crucial to achieving high system performance. Only if the additional area is small and the cycle time impact is negligible should division and square root share the same hardware.

### 2.3.6 On-the-fly Rounding and Conversion

In a nonrestoring division implementations such as SRT, an extra cycle is often required after the division operation completes. In SRT, the quotient is typically collected in a representation where the digits can take on both positive and negative values. Thus, at some point, all of the values must be combined and converted into

Figure 2.11: Effects of on-the-fly rounding and conversion

a standard representation. This requires a full-width addition, which can be a slow operation. To conform to the IEEE standard, it is necessary to round the result. This, too, can require a slow addition.

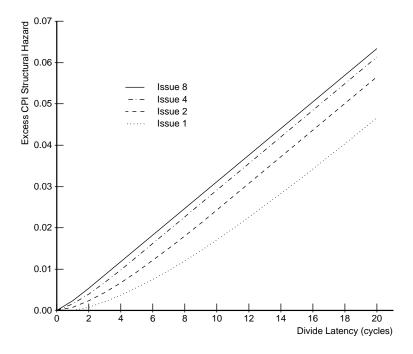

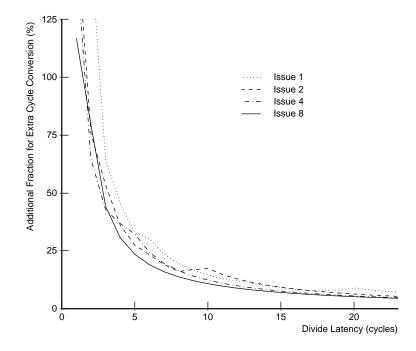

Techniques exist for performing this rounding and conversion "on-the-fly," and therefore the extra cycle may not be needed [22]. Because of the complexity of this scheme, the designer may not wish to add the additional required hardware. Figure 2.11 shows the performance impact of requiring an additional cycle after the division operation completes. For division latencies greater than 10 cycles, less than 20% of the total division penalty in CPI is due to the extra cycle. At very low division latencies, where the latency is less than or equal to 4 cycles, the penalty for requiring the additional cycle is obviously much larger, often greater than 50% of the total division penalty.

### 2.3.7 Consumers of Division Results

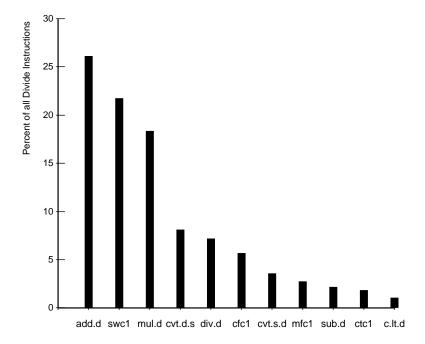

In order to reduce the effective penalty due to division, consider which operations actually use division results. Figure 2.12 is a histogram of instructions that consume division results.

This can be compared with the histogram for multiply results, shown in figure 2.13. For multiply results, the biggest users are multiply and add instructions. Since both *add.d* and *sub.d* use the FP adder, the FP adder is the consumer for nearly 50% of the multiply results. Accordingly, fused operations such as multiply-accumulate are useful. Because the multiply-add pattern occurs frequently in such applications and it does not require much more hardware than the separate functional units, fused multiply-adders are often used in modern processors.

Looking at the consumers of division results, the FP adder is the largest consumer with 27% of the results. The second biggest consumer is the store operation with 23% of the results. It is possible to overcome the penalties due to a division-store interlock, though, with other architectural implementations. A limited number of registers can require a division result to be spilled to memory through a store instruction. By either adding registers or register renaming, it may be possible to reduce the urgency due to store.

While the percentage of division results that the adder consumes is not as high as for multiply results, it is still the largest user. A designer could consider the implementation of a fused divide-add instruction to increase performance. In division implementations where on-the-fly conversion and rounding is not used, an extra addition cycle exists for this purpose. It may be possible to make this a three-way addition, with the third operand coming from a subsequent add instruction. Because this operand is known soon after the instruction is decoded, it can be sent to the the three-way adder immediately. Thus, a fused divide-add unit could provide additional performance.

Figure 2.12: Consumers of division results

Figure 2.13: Consumers of multiply results

### 2.4 Summary

This chapter has investigated the issues of designing an FP divider in the context of an entire system. The frequency and interlock distance of division instructions in SPECfp92 benchmarks have been determined, along with other useful measurements, in order to answer several questions regarding the implementation of a floating point divider.

The data shows that for the slowest hardware divider, with a latency greater than 60 cycles, the CPI penalty can reach 0.50. To achieve good system performance, some form of hardware division is required. However, at very low divider latencies, two problems arise. The area required increases exponentially or cycle time becomes impractical. There is a knee in the area/performance curve near 10 cycles. Dividers with lower latencies do not provide significant system performance benefits, and their areas are too large to be justified.

The compiler can decrease the urgency of division results. Most of the performance gain is in performing basic compiler optimizations, at the level of O2. Only marginal improvement is gained by further optimization. The average interlock distance increases by a factor of three by using compiler optimization. Accordingly, for scalar processors, a division latency of 10 cycles or less can be tolerated.

Increasing the number of instructions issued per cycle also increases the urgency of division results. Increasing the number of instructions issued per cycle to 2 causes a 38% increase in excess CPI, increasing to 4 causes a 94% increase in excess CPI, and increasing to 8 causes a 120% increase in excess CPI. Further, as the width of instruction issue increases, the excess CPI due to division increases even faster. Wide issue machines utilize the instruction-level parallelism in applications by issuing multiple instructions every cycle. While this has the effect of decreasing the base CPI of the processor, it exposes the functional unit latencies to a greater degree and accentuates the effects of slow functional units.

In most situations, an existing FP multiplier can be shared when using a multiplication based division algorithm. The results show that for a division latency of around 13 cycles, the CPI penalty is between 0.025 and 0.040. While the CPI penalty is low when the multiplier is shared and modified to also perform division, the designer must also consider effects on the multiplier which could have an impact on cycle time.

On-the-fly rounding and conversion is not essential for all division implementations. For division latencies greater than 10 cycles, the lack of on-the-fly rounding and conversion does not account for a significant fraction of the excess CPI, and, as a result, is not required. However, for very high performance implementations where the area and complexity are already large, this method is a practical means of further reducing division latency.

Addition and store operations are the most common consumers of division results. Accordingly, the design of a fused divide-add unit is one means of achieving additional system performance.

While division is typically an infrequent operation even in floating point intensive applications, ignoring its implementation can result in system performance degradation.

# Chapter 3

# **Faster FP Addition**

## 3.1 Introduction

Chapter 2 shows that the most frequent FP operations are addition and subtraction, and together they account for over half of the total FP operations in typical scientific applications. Both addition and subtraction use the FP adder. Techniques to reduce the latency and increase the throughput of the FP adder have therefore been the subject of much previous research.

Due to its many serial component operations, FP addition can have a longer latency than FP multiplication. Pipelining is a commonly used method to increase the throughput of the adder, but it does not reduce the latency. Previous research has provided algorithms to reduce the latency by performing some of the operations in parallel. This parallelism is achieved at the cost of additional hardware. The minimum achievable latency using such algorithms in high clock-rate microprocessors has been three cycles, with a throughput of one cycle.

To further reduce the latency, we observe that not all of the components are needed for all input operands. Two VLA techniques are proposed to take advantage of this to reduce the average addition latency [23]. To effectively use average latency, the processor must be able to exploit a variable latency functional unit. The processor might use some form of dynamic instruction scheduling with out-of-order execution in order to use the reduced latency and achieve maximum system performance.

## 3.2 FP Addition Algorithms

FP addition comprises several individual operations. Higher performance is achieved by reducing the maximum number of serial operations in the critical path of the algorithm. The following sections summarize the results of previous research in the evolution of high-performance floating-point addition algorithms. Throughout this study, the analysis assumes IEEE double precision operands (a 64 bit word, comprising a 1 bit sign, an 11 bit biased exponent, and a 52 bit significand, with one hidden significand bit [1]).

## 3.2.1 Basic

The straightforward addition algorithm Basic requires the most serial operations. It has the following steps [24]:

- 1. Exponent subtraction: Perform subtraction of the exponents to form the absolute difference  $|E_a - E_b| = d$ .

- 2. Alignment: Right shift the significand of the smaller operand by d bits. The larger exponent is denoted  $E_f$ .

- 3. Significand addition: Perform addition or subtraction according to the effective operation, which is a function of the opcode and the signs of the operands.

- 4. Conversion: Convert the significand result, when negative, to a sign-magnitude representation. The conversion requires a two's complement operation, including an addition step.

- 5. Leading-one detection: Determine the amount of left shift needed in the case of subtraction yielding cancellation. For addition, determine whether or not a 1 bit right is required. Priority encode (PENC) the result to drive the normalizing shifter.

- 6. Normalization: Normalize the significand and update  $E_f$  appropriately.

7. Rounding: Round the final result by conditionally adding 1 ulp as required by the IEEE standard. If rounding causes an overflow, perform a 1 bit right shift and increment  $E_f$ .

The latency of this algorithm is large, due to its many long length components. It contains two full-length shifts, in steps 2 and 6. It also contains three full-length significand additions, in steps 3, 4 and 7.

## 3.2.2 Two-Path

Several improvements can be made to *Basic* in order to reduce its total latency. These improvements come typically at the cost of adding additional hardware. These improvements are based on noting certain characteristics of FP addition/subtraction computation:

- 1. The sign of the exponent difference determines which of the two operands is larger. By swapping the operands such that the smaller operand is always subtracted from the larger operand, the conversion in step 4 is eliminated in all cases except for equal exponents. In the case of equal exponents, it is possible that the result of step 3 may be negative. Only in this event could a conversion step be required. Because there would be no initial aligning shift, the result after subtraction would be exact and there will be no rounding. Thus, the conversion addition in step 4 and the rounding addition in step 7 become mutually exclusive by appropriately swapping the operands. This eliminates one of the three carrypropagate addition delays.

- 2. In the case of effective addition, there is never any cancellation of the results. Accordingly, only one full-length shift, an initial aligning shift, can ever be needed. For subtraction, two cases need to be distinguished. First, when the exponent difference d > 1, a full-length aligning shift may be needed. However, the result never requires more than a 1 bit left shift. Similarly if  $d \leq 1$ , no full-length aligning shift is necessary, but a full-length normalizing shift may be required in the case of subtraction. In this case, the 1 bit aligning shift and the

conditional swap can be predicted from the low-order two bits of the exponents, reducing the latency of this path. Thus, the full-length alignment shift and the full-length normalizing shift are mutually exclusive, and only one such shift need ever appear on the critical path. These two cases can be denoted *CLOSE* for  $d \leq 1$ , and *FAR* for d > 1, where each path comprises only one full-length shift [25].

3. Rather than using leading-one-detection after the completion of the significand addition, it is possible to predict the number of leading zeros in the result directly from the input operands. This leading-one-prediction (LOP) can therefore proceed in parallel with the significand addition using specialized hard-ware [26],[27].

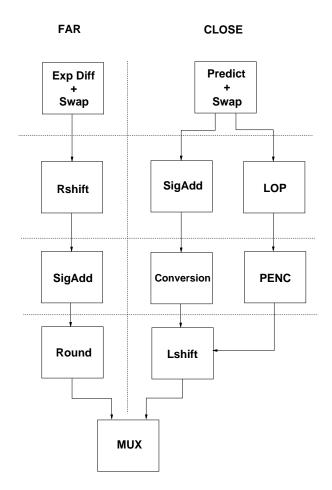

An improved adder takes advantage of these three cases. It implements the significand datapath in two parts: the *CLOSE* path and *FAR* path. At a minimum, the cost for this added performance is an additional significand adder and a multiplexor to select between the two paths for the final result. Adders based on this algorithm have been used in several commercial designs [28],[29],[30]. A block diagram of the improved *Two Path* algorithm is shown in figure 3.1.

## 3.2.3 Pipelining

To increase the throughput of the adder, a standard technique is to pipeline the unit such that each pipeline stage comprises the smallest possible atomic operation. While an FP addition may require several cycles to return a result, a new operation can begin each cycle, providing maximum throughput. Figure 3.1 shows how the adder is typically divided in a pipelined implementation. It is clear that this algorithm fits well into a four cycle pipeline for a high-speed processor with a cycle time between 10 and 20 gates. The limiting factors on the cycle time are the delay of the significand adder (SigAdd) in the second and third stages, and the delay of the final stage to select the true result and drive it onto a result bus. The first stage has the least amount of computation; the *FAR* path has the delay of at least one 11 bit adder and two multiplexors, while the *CLOSE* path has only the delay of the 2 bit exponent

Figure 3.1: Two path algorithm

prediction logic and one multiplexor. Due to the large atomic operations in the second stage, the full-length shifter and significand adder, it is unlikely that the two stages can be merged, requiring four distinct pipeline stages.

When the cycle time of the processor is significantly larger than that required for the FP adder, it is possible to combine pipeline stages, reducing the overall latency in machine cycles but leaving the latency in time relatively constant. Commercial superscalar processors, such as Sun UltraSparc [31], often have larger cycle times, resulting in a reduced FP addition latency in machine cycles when using the TwoPath algorithm. In contrast, superpipelined processors, such as DEC Alpha [32], have shorter cycle times and have at least a four cycle FP addition latency. For the rest of this study, it is assumed that the FP adder cycle time is limited to contain only one large atomic operation, such that the pipelined implementation of Two Pathrequires four stages.

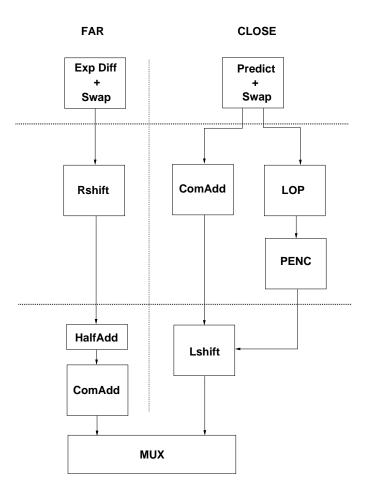

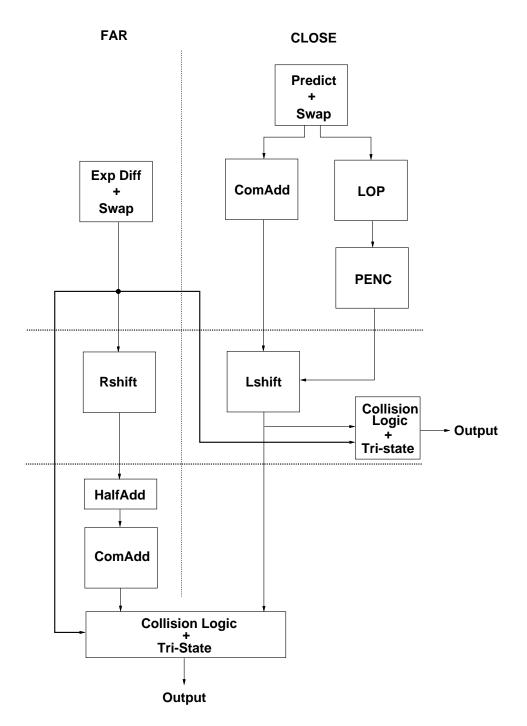

## 3.2.4 Combined Rounding

A further optimization can be made to the Two Path algorithm to reduce the number of serial operations. This optimization is based upon the realization that the rounding step occurs very late in the computation, and it only modifies the result by a small amount. By precomputing all possible required results in advance, rounding and conversion can be reduced to the selection of the correct result, as described by Quach [33],[34]. Specifically, for the IEEE round to nearest (RN) rounding mode, the computation of A + B and A + B + 1 is sufficient to account for all possible rounding and conversion possibilities. Incorporating this optimization into Two Path requires that each significand adder compute both sum and sum+1, typically through the use of a compound adder (ComAdd). A compound adder is a special adder that computes sum and sum+1 while sharing some internal hardware to reduce the size. Selection of the true result is accomplished by analyzing the rounding bits, and then selecting either of the two results. The rounding bits are the sign, LSB, guard, and sticky bits. This optimization removes one significand addition step. For pipelined implementations, this can reduce the number of pipeline stages from four to three. The cost of this improvement is that the significand adders in both paths must be modified to produce both sum and sum+1.

For the two directed IEEE rounding modes round to positive and minus infinity (RP and RM), it is also necessary to compute A + B + 2. The rounding addition of 1 ulp may cause an overflow, requiring a 1 bit normalizing right-shift. This is not a problem in the case of RN, as the guard bit must be 1 for rounding to be required. Accordingly, the addition of 1 ulp will be added to the guard bit, causing a carry-out into the next most significant bit which, after normalization, is the LSB. However, for the directed rounding modes, the guard bit need not be 1. Thus, the explicit addition sum+2 is required for correct rounding in the event of overflow requiring a 1 bit normalizing right shift. In [33], it is proposed to use a row of half-adders above the

Figure 3.2: Three cycle pipelined adder with combined rounding