# VALIDATION TOOLS FOR COMPLEX DIGITAL DESIGNS

Chian-Min Richard Ho

Technical Report No. CSL-TR-96-708

December 1996

This research was funded by ARPA Contract DABT63-94-C-0054 and Rockwell Semiconductor.

© Copyright by Chian-Min Richard Ho 1996 All Rights Reserved

| •                           | s dissertation and that in my opinion it is fully adequate, ssertation for the degree of Doctor of Philosophy. |

|-----------------------------|----------------------------------------------------------------------------------------------------------------|

| Mark A.                     | Horowitz (Principal Advisor)                                                                                   |

| -                           | s dissertation and that in my opinion it is fully adequate ssertation for the degree of Doctor of Philosophy.  |

| David L.                    | Dill                                                                                                           |

| <u> </u>                    | s dissertation and that in my opinion it is fully adequate ssertation for the degree of Doctor of Philosophy.  |

|                             | e Olukotun                                                                                                     |

| Approved for the University | y Committee on Graduate Studies:                                                                               |

|                             |                                                                                                                |

#### **Abstract**

The functional validation of a state-of-the-art digital design is usually a laborious, ad hoc and open-ended task. Many circuits, and especially modern processors, are too complex to be formally verified in their entirety. Instead, simulation of a register transfer level (RTL) model is used to determine whether the design conforms to the specification for a particular set of test vectors which will hopefully cover all the important and interesting corner cases of the design. Unfortunately, creating a good test vector suite is difficult.

This research explores techniques to make the validation task more systematic, automated and efficient. This can be accomplished by using information embedded in the RTL model to extract the set of "interesting behaviors" of the design, represented as interacting finite state machines (FSM). These behaviors include things like multiple or concurrent events, rare corner cases and long control paths, combinations of which tend to lead to bugs. If all of these interesting behaviors of the RTL could be tested in simulation, the degree of confidence that the design is correct would be substantially higher. This work provides two tools towards this end. First, a test vector generator is described that uses this information to produce a series of test vectors that will exercise all the implemented behaviors of the design in RTL simulation. Secondly, the information can be used as the basis for coverage analysis of a pre-existing test vector suite. The degree to which a test vector suite covers the important tests is known as the *coverage* of the suite. Previous coverage metrics have relied on measures such as the number of toggles on a node in the circuit or code block execution counts. These metrics often give good first order indications of how thorough each part of a circuit has been exercised by test vectors. However, they do not usually give an accurate picture of whether the important test cases involving multiple or concurrent events have been exercised. In this thesis, a new method is proposed of analyzing test vector suite coverage based on projecting a minimized control state graph onto control signals that enter the datapath part of the design, yielding a meaningful metric and providing detailed feedback to the designers about missing tests.

The fundamental problem facing any technique that uses state exploration, as these do, is state space explosion. The exponential growth of the state graph limits the complexity of the models that can be dealt with. Two techniques are proposed to minimize this

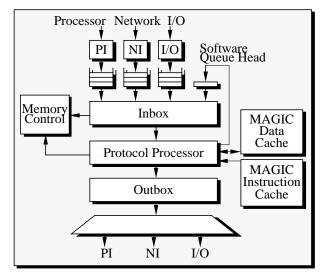

problem; first, a dynamic state graph pruning algorithm based on static analysis of the model structure to provide an exact minimization and second, approximation of the state graph with an estimation of the state space in a more compact representation. These techniques help delay the onset of state explosion, allowing useful information to be obtained and utilized by designers, even for complex designs. Results and practical experiences of applying these techniques to the design of the node controller (MAGIC) of the Stanford FLASH Multiprocessor project are given.

# Acknowledgments

I arrived at Stanford University in the Fall of 1990 with only a vague notion of wanting to earn a Doctorate Degree, not knowing what exactly I wanted to work on or how to set about it. I thrashed about for a year trying to find direction. Then I persuaded Mark Horowitz to become my advisor, and I think that was probably my best decision at Stanford. Mark has not only been a source of excellent advice, enlightening discussions and excellent questions, but has also been an enormous well-spring of encouragement over the years.

My thanks and appreciation also go out to David Dill, for all his patience and tutorship. My conversations with Dave always helped put my work in context and often led to further ideas and refinements.

I also with to thank Kunle Olukotun for bravely agreeing to serve on my Reading Committee at a time when this dissertation was still a vague jumble of ideas.

This work grew as part of the Stanford FLASH Multiprocessor project and I am indebted to its team members for their friendship and humor. In no particular order: Jeff Kuskin, Dave Ofelt, Mark Heinrich, John Heinlein, Jules Bergmann, Dave Nakahira, Joel Baxter, Ravi Sound, Hema Kapadia, Shankar Govindaraju, Rich Simoni, Ziyad Hakura.

I want to thank my parents and brother Jenson for always believing in me and encouraging me to keep pushing forward with my work.

But most of all, I want to thank my new bride Sandy, whose eternal patience, loving smiles, and tender words made everything possible.

# **Table of Contents**

| Abstract                                                                                                                                                                                                                                               | iv                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Acknowledgments                                                                                                                                                                                                                                        | vi                               |

| Γable of Contents                                                                                                                                                                                                                                      | vii                              |

| List of Tables                                                                                                                                                                                                                                         | X                                |

| List of Figures                                                                                                                                                                                                                                        | xi                               |

| Chapter 1. Introduction                                                                                                                                                                                                                                | 1                                |

| 1.1 Overview of Thesis                                                                                                                                                                                                                                 | . 3                              |

| Chapter 2. Background                                                                                                                                                                                                                                  | 6                                |

| 2.1 Design Validation through Simulation  2.1.1 Validation Test Vectors  2.1.2 Measuring Validation.  2.2 Formal Hardware Verification  2.2.1 Reachability Analysis  2.2.2 Equivalence Checking with Logic  2.3 Using Formal Techniques in Validation. | 11<br>13<br>15<br>16<br>17       |

| Chapter 3. Capturing Interesting Test Behaviors                                                                                                                                                                                                        | 20                               |

| 3.1 Focus on Control Logic 3.2 Validation Methodology based on Control Interactions. 3.3 RTL-to-FSM Translation 3.3.1 Semantic Issues 3.3.2 Identifying Control-Logic 3.3.3 Abstracting the Design. 3.4 State-Enumeration Tool 3.5 Discussion.         | 21<br>24<br>25<br>28<br>29<br>32 |

| Chapter 4. Validation Vector Generation                                                                                                                                                                                                                | 35                               |

| 4.1 Paths through the State Graph                                                                                                                                                                                                                      | 37                               |

| 4.3 Undetectable Bugs                                                                                                                                                                                                                                  | 40                               |

| 4.4 Stanford FLASH Memory Controller Example            | 42        |

|---------------------------------------------------------|-----------|

| 4.4.1 Protocol Processor Test Generation                | 44        |

| 4.4.2 Protocol Processor Bugs                           | 46        |

| 4.5 Related Work                                        | 49        |

| 4.6 Discussion                                          | 49        |

| Chapter 5. Validation Coverage Analysis                 | 52        |

| 5.1 Graph Redundancies                                  | 53        |

| 5.2 Graph pruning using Static Analysis for Don't Cares | 54        |

| 5.2.1 Static Analysis of Kill Sets                      | 56        |

| 5.2.2 Dynamic Pruning with Don't Cares                  | 57        |

| 5.3 Control Events                                      | 63        |

| 5.3.1 Coverage Property                                 |           |

| 5.3.2 Control Event Graph                               | 66        |

| 5.4 Over-Generalized Environment                        | 68        |

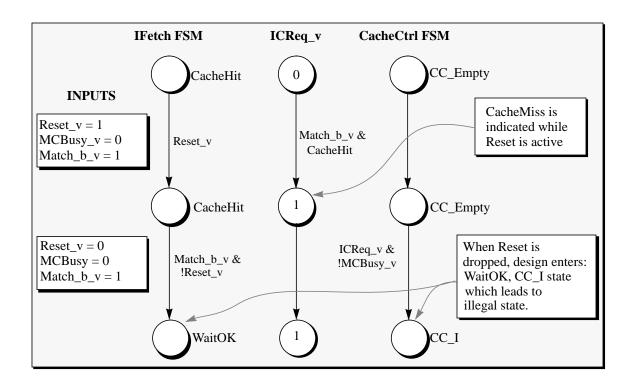

| 5.4.1 Case 1: Illegal Sequence from Reset               |           |

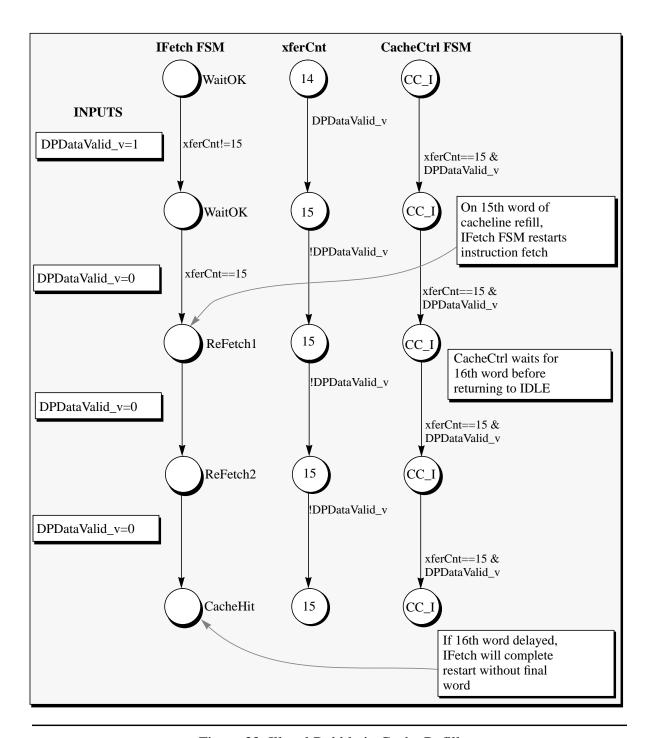

| 5.4.2 Case 2: No Bubble in Cache Refill                 | 71        |

|                                                         | 71<br>74  |

| 3.3 Incremental reedback                                | /4        |

| <b>Chapter 6. Coping with State Space Explosion</b>     | <b>76</b> |

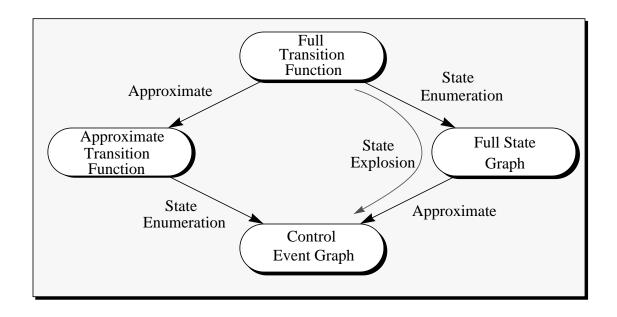

| 6.1 State Graph Approximation                           | 77        |

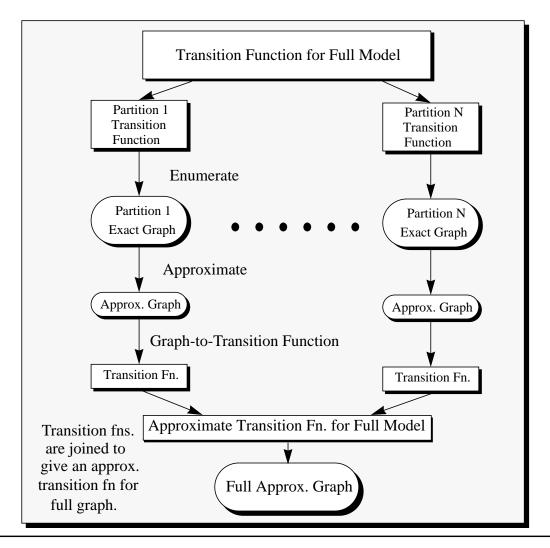

| 6.2 Approximation from Exact Partitions                 | 78        |

| 6.2.1 Exact Partitions Algorithm                        | 78        |

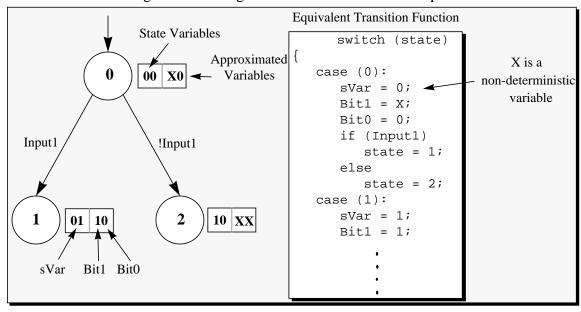

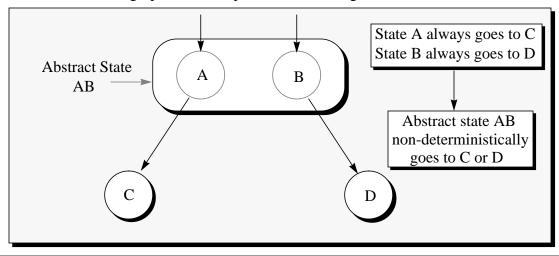

| 6.3 Approximating the Transition Function               | 83        |

| 6.3.1 Choice of Approximation Variables                 | 84        |

| 6.4 Related Work in State Graph Approximation           | 85        |

| 6.4.1 Other Approximation Techniques for Validation     | 86        |

| 6.5 FLASH Coverage Results                              | 87        |

| Chapter 7. Conclusions                                  | 89        |

| References                                              | 94        |

# **List of Tables**

| Table 1. Errata Classification of MIPS R4000              |

|-----------------------------------------------------------|

| Table 2. PP Instruction Classes                           |

| Table 3. PP State Enumeration Results                     |

| Table 4. Test Vector Generation Statistics                |

| Table 5. Synopsis of Discovered Bugs                      |

| Table 6. Dynamic Pruning Results (5MByte Hash Table)      |

| Table 7. State variable kill sets comparison 61           |

| Table 8. Constraints in Approximated Instr. Fetch Unit 81 |

| Table 9. Different Approximated Variables for Inbox       |

| Table 10. Coverage Results                                |

# **List of Figures**

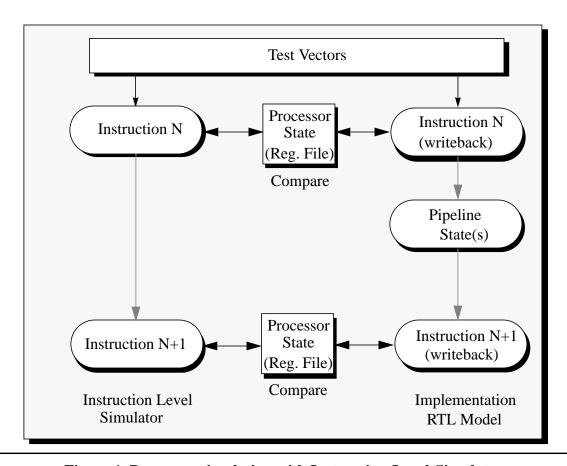

| Figure 1. Processor simulation with Instruction-Level-Simulator               | . 9 |

|-------------------------------------------------------------------------------|-----|

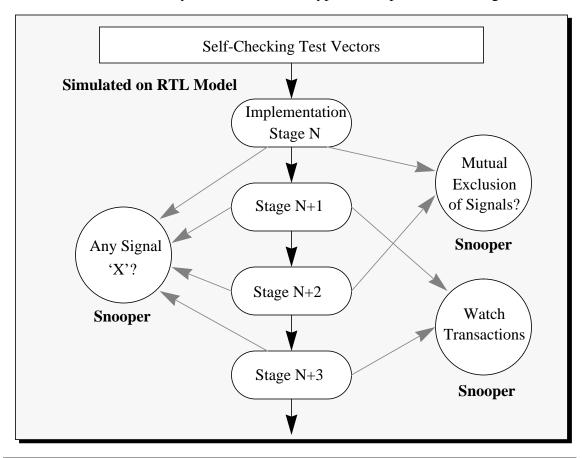

| Figure 2. Simulation with Self-Checking Vectors and Snoopers                  | 10  |

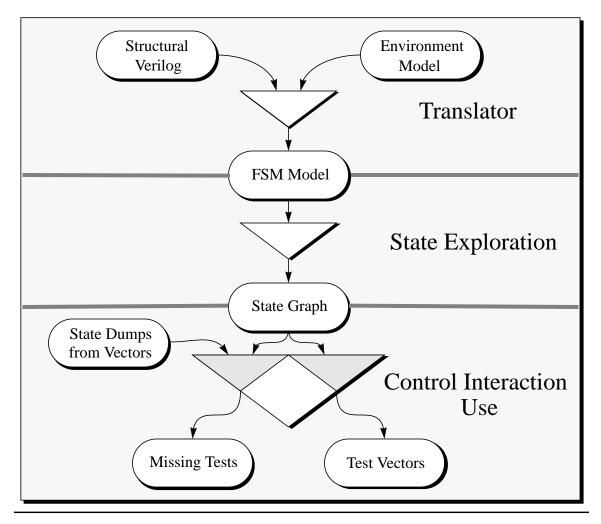

| Figure 3. Validation Methodology based on Control Interactions                | 22  |

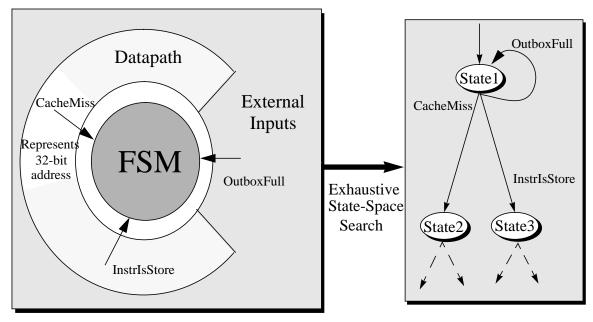

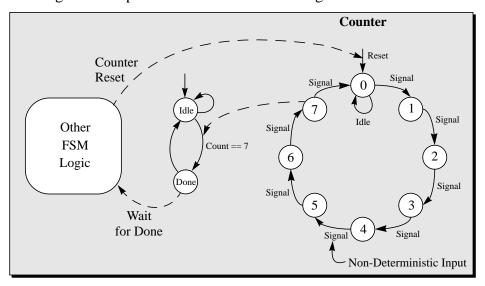

| Figure 4. Non-deterministic Environment                                       | 23  |

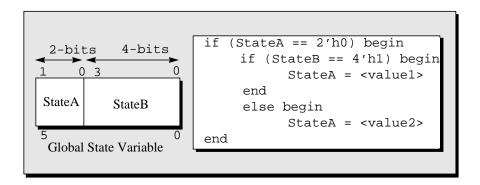

| Figure 5. Problematic MPP State Assignment                                    | 26  |

| Figure 6. Breaking up state-to-state assignments in MPP                       | 27  |

| Figure 7. Code examples of transparent latch (a) and edge-triggered flop (b). | 28  |

| Figure 8. State Annotation Example                                            | 29  |

| Figure 9. Transitive Fan-In Algorithm                                         | 30  |

| Figure 10. Murφ State-Space Exploration Algorithm                             | 33  |

| Figure 11. Tour Generation Algorithm                                          | 36  |

| Figure 12. Converting Transition Edge to Test-Vector                          | 37  |

| Figure 13. Sample Transition Condition Mapping                                | 39  |

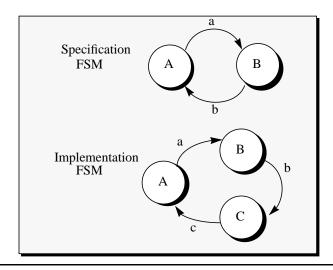

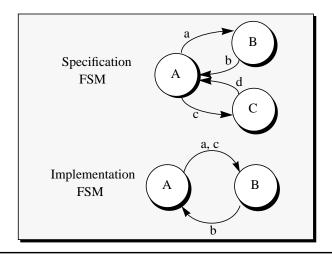

| Figure 14. Erroneous FSM Implementation with more Behaviors                   | 41  |

| Figure 15. Erroneous FSM Implementation with fewer Behaviors                  | 42  |

| Figure 16. MAGIC Block Diagram                                                | 43  |

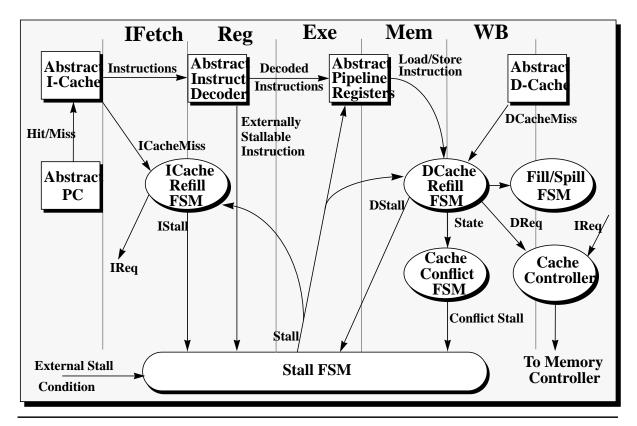

| Figure 17. PP Abstract FSM model                                              | 45  |

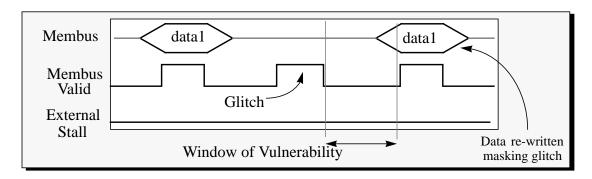

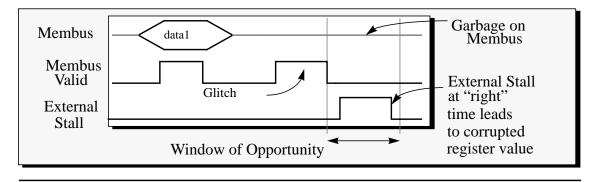

| Figure 18. Bug #5 Timing Diagram (Glitch Masked)                              | 48  |

| Figure 19. Bug #5 Timing Diagram (Garbage written)                            | 48  |

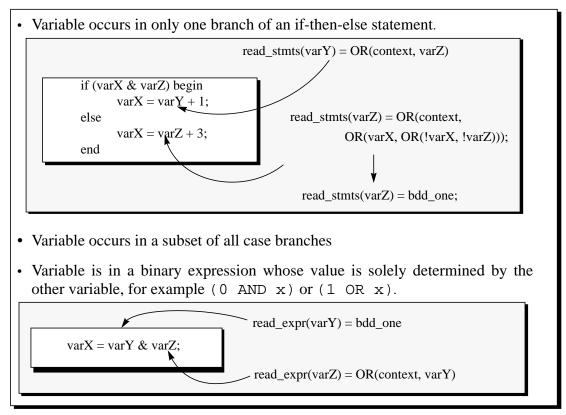

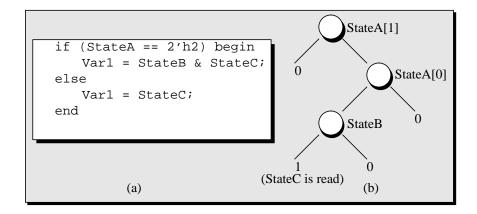

| Figure 20. Don't Care variable due to code structure                          | 55  |

| Figure 21. List of RTL Structures where a Kill-Set may be possible            | 56  |

| Figure 22. Static Analysis for Kill Sets                                      | 57  |

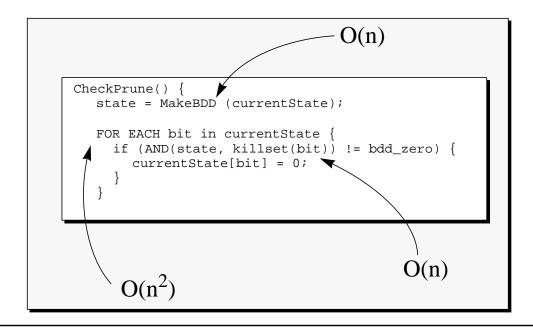

| Figure 23. Dynamic Pruning Algorithm                                          | 58  |

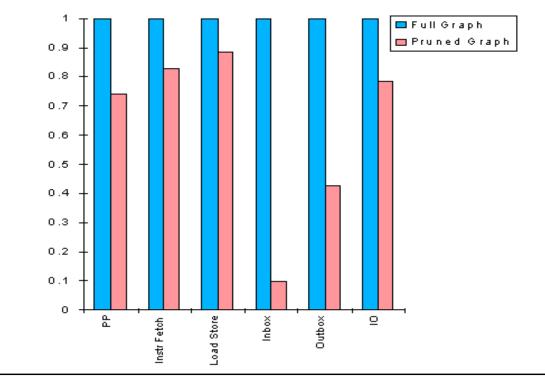

| Figure 24. Relative Pruned State-Space Size                                   | 59  |

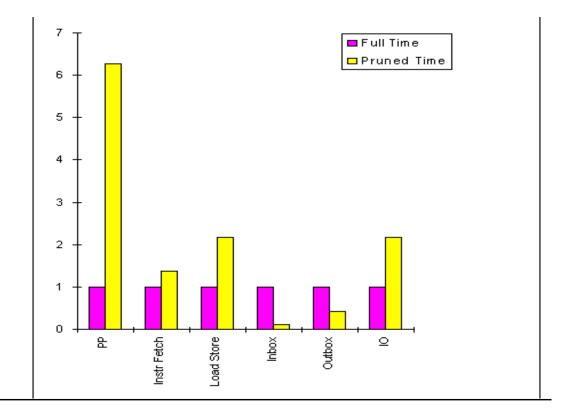

| Figure 25. Relative Running Times                                             | 60  |

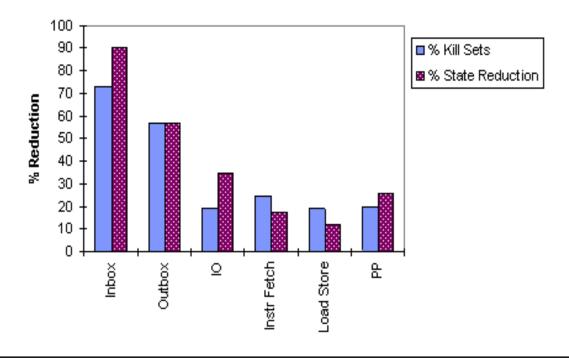

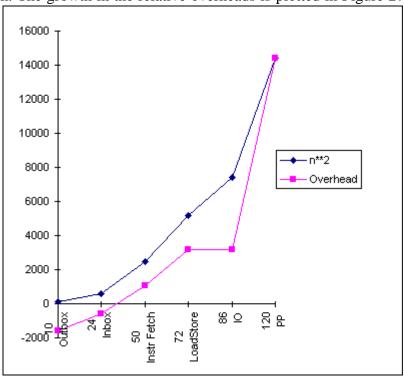

| Figure 26. Correlation of kill sets and state reduction                       | 61  |

| Figure 27. Growth of Relative Overhead                                        | 62  |

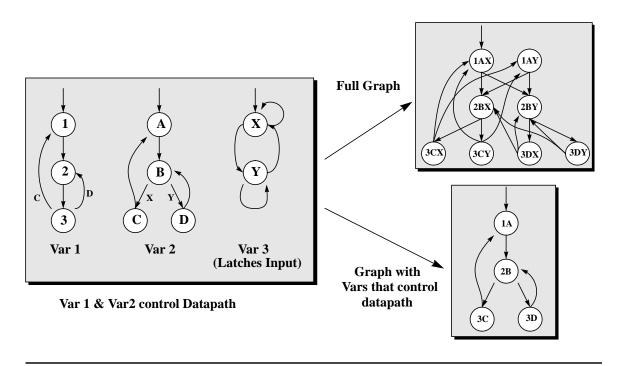

| Figure 28. Example of State Graph Redundancy                                  | 64  |

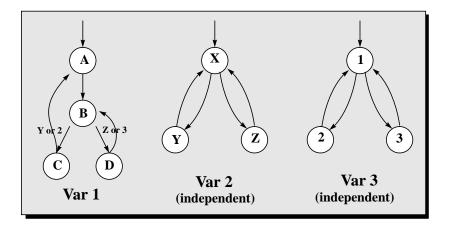

| Figure 29. Independent State Variables                                        | 66  |

| Figure 30. Counter fed by Non-Deterministic Input                             | 68  |

| Figure 31. Illegal Sequence from Reset                        | 70 |

|---------------------------------------------------------------|----|

| Figure 32. Illegal Bubble in Cache Refill                     | 72 |

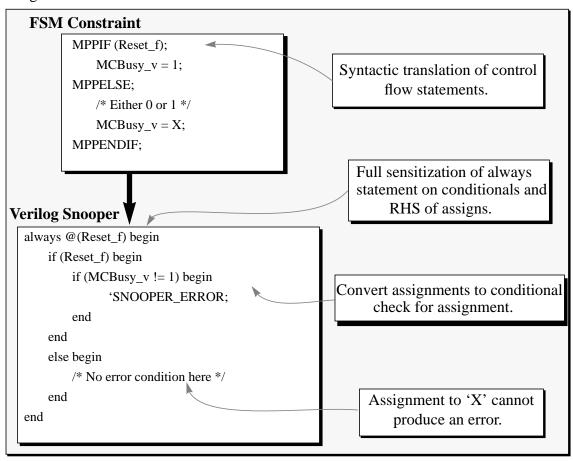

| Figure 33. Converting a Constraint to a Snooper               | 73 |

| Figure 34. Approximating the State Graph                      | 78 |

| Figure 35. Approximation of Exact Partitions                  | 79 |

| Figure 36. Conversion of State-Graph to Transition Function   | 80 |

| Figure 37. Approximating Graph leads to Non-deterministic FSM | 81 |

| Figure 38. Non-deterministic FSM                              | 82 |

# **Chapter 1. Introduction**

Ongoing semiconductor process technology improvements are resulting in progressively smaller feature sizes and continually better yields. This trend has given circuit designers more silicon area on each die in which to pack ever increasing amounts of functionality. As a result, digital designs are progressively becoming faster and more complex. These trends make the task of verifying that the design is free of functional bugs increasingly difficult. Larger designs tend to have more concurrent interactions, all of which require testing. And as the number of these interactions grow, the ability of humans to track and think up tests for them diminishes. At the same time, business considerations such as time-to-market pressure designers to produce working silicon in the fewest number of *tapeouts* (sending the design for fabrication). There is also pressure to avoid a negative public image that results from a serious bug getting into a shipping product [Mer94]. The result of these trends is that functional correctness checking poses an increasingly hard and important challenge to design teams.

One approach to this problem is to use formal verification techniques, discussed in more detail in Chapter 2. These strive to show categorically that a property is true or not true in a design. They show a great deal of promise and have successfully verified many important properties of large designs. However, because of issues of complexity, statespace or representation size, these techniques have tended to work with models of designs that are either relatively small or have been abstracted in order to focus on one aspect of the verification problem. There remain unresolved issues when working with many of the

large designs produced by the semiconductor industry. These unresolved issues have prevented the widespread adoption of formal techniques for functional correctness proofs.

In the absence of a method to completely verify designs, simulation of a detailed register transfer level (RTL) description has been utilized. Simulation cannot realistically be expected to exhaustively test all the operations of a non-trivial design, but with a set of well-designed test vectors, it can provide a certain confidence level. Unfortunately, since simulation is relatively slow, of the order of hundreds of cycles per second or slower, and well-designed test vectors are hard to create, this *validation task* often consumes as much resources as the design process. The introduction of cycle-based simulators and hardware emulation technology [GBC+95] will alleviate this problem to some extent, but achieving exhaustive simulation is impossible. Even at a speed of 100MHz, which is aggressive with existing technology, it would take approximately 325 years to exhaustively simulate a small design of about 300 bits of state.

Current validation techniques rely heavily on test cases that are composed by the designer to stress particular functions of the design. These tests, sometimes called *directed tests*, are meant to exercise the circuit through all its important functionality by directing the simulation towards what are considered interesting situations. These include all variations of the basic functionality of the design as well as combinations of different functions which can occur concurrently. A good suite of validation tests will be able to exercise the design through all its basic functions and many of its more complex, concurrent functions. Unfortunately, the job of thinking up and writing tests for all the combinations of concurrent functions is a difficult and laborious one for a human designer. And quite often, a complex or rare situation that is overlooked by the designer, resulting in incorrect operation, may also be overlooked by the test writer, leaving a bug in the design.

To deal with this possibility, many designers also employ *pseudo-random* test vectors in simulation after basic functionality has been checked with directed tests. The goal is to inject randomness into as many of the inputs of a design as possible to stir up situations missed by the designer and the directed tests. A typical example for processor designs is to randomly assert exceptions. Pseudo-random tests have proven to be very effective at finding bugs, by causing situations to occur in simulation that were missed by the test writer.

Together, directed and pseudo-random tests, run in simulation, form the backbone of the traditional validation methodology. Although they do a reasonable job, the difficulty of making these test vectors effective grows as designs grow more complex. The limitation is that it is infeasible for a human to figure out all the possible interactions that require testing in a non-trivial design. On the other hand, pseudo-random tests provide the ability to stochastically reach lots of the interactions, but cannot guarantee that all will be reached in a reasonable amount of time. It is also difficult to know how many of the interactions have been tested with pseudo-random vectors, making it hard to decide when to stop. There remains a gap between the desired correctness confidence level for many designs and current validation techniques.

#### 1.1 Overview of Thesis

What is needed is some form of instrumentation to guide and measure the validation process so that progress can be judged quantitatively. One such measure is the reachable product state space of the control finite state machines (FSM). In simple terms, the FSMs of a design encode its behaviors. Each individual FSM controls one aspect of the design's behavior. The combination of all the FSMs acting in concert on all the inputs determine the global behavior of a design. Although many errors arise because individual FSMs or the combinational logic derived from them are wrong, these tend to be easy to discover in simulation by directed tests aimed at basic functionality. However, when two or more FSMs communicate or jointly control a behavior, then the task of testing each such interaction manually becomes hard. Apart from the combinatorial explosion of cases, it is frequently difficult to keep track of and create each in a test vector.

Though it is often hard to find all the interactions in a design manually, this information is encoded in the register transfer level (RTL) model of a design, which is a detailed description of the intended implementation. It would be very useful if this information could be utilized automatically with minimal user assistance. Then, validation tools could use this information either to create tests or to measure coverage. It turns out that for designs that try to separate control and datapath sections, such extraction of the control FSMs mostly automatically is possible. In fact, if the RTL is written in a synthesizable subset of a hardware description language (HDL), such as Verilog [TM91], then this extraction is relatively straightforward. The non-trivial aspect is identification of which

logic constitutes control and which datapath. The approach taken in this work is to obtain hints from the designer, and is described in Chapter 3.

Once the control FSMs have been extracted, the global behavior of the design can be found by enumerating all the possible states that the communicating FSMs can reach. This is a technique used in formal verification to prove properties about every state of a design. For validation work, the important information is the reachable state space. Each state in the global state graph represents an interaction between the FSMs. Hence, it provides a map of all the interactions in the design. If the simulated test vectors manage to reach every state and edge of the global state graph, then the confidence level of its correctness would be high. For this work, the FSM enumeration tool is derived from work done in [DDH+92] and is described in Chapter 3.

Using the full global state space of the control FSMs provides a quantitative measure of test vector completeness with respect to implemented FSM interactions. If the state space can be found exactly, this not only provides a way to measure testing progress, but can provide a map of how to test those interactions. If the inputs to the control FSM model correspond to inputs to the RTL design that can be manipulated by test vectors, then it is possible to generate test vectors automatically that would cause the RTL to follow a particular path through the global state space. Chapter 4 discusses an example of this type of test vector generation and its limitations.

Unfortunately, test vector generation is not possible for all designs for several reasons, including explosion of the global state space, the inability to provide correctness checking using these vectors in some designs, and the inability to control some inputs needed by this type of test vector. In cases where these issues cannot be overcome, the global state space can still provide a useful measure of the completeness of functional testing, in other words, coverage analysis.

The experience of using this method of coverage analysis in a real design example, the node controller of the FLASH multiprocessor [KOH+94], demonstrates that coverage information about state space can be overwhelming when presented directly without filtering for relevance. This makes it difficult to use in a practical setting. This observation leads to a method, presented in Chapter 5, that projects the full state space onto the signals that directly affect the datapath portion of the design. Using this projection on the state

space leads to incremental coverage feedback that pinpoints the missing tests in their simplest forms, which is easier to use.

Using the full control FSM state space for test vector generation and coverage analysis is appealing from a completeness viewpoint. However, for many realistic and interesting designs, the global state space of the control FSMs is too large to be found and manipulated with reasonable computing resources. The state space explosion problem plagues all formal verification techniques that attempt to find the reachable states of a model. However, validation uses the state space in a less strict manner than formal verification generally does. It is not always necessary to retain the full global state space to obtain useful coverage information, especially basic coverage information. Hence, it is still productive to approximate the state space with one that requires less memory and runtime but retains properties of the full space. The basic idea is to retain the state variables that the designer believes will interact in interesting ways, and remove variables that have small impacts on the full state space. The problem is that the approximate state graph will either miss real states or create states that do not really exist in the full state graph. Heuristics and issues related to approximation of the state space are discussed in Chapter 6, along with some results of coverage analysis using an approximation of the state space of some of the units of FLASH. These show that despite errors in the approximation, useful information can still be obtained to guide the validation task for complex designs.

The remaining chapters describe in detail the process and the practical experiences of using automatically extracted control state to guide and assist validation.

# Chapter 2. Background

This chapter first reviews the most common methods of validation in use today to better understand the nature of the problem and the limitations of current simulation based approaches. To try to provide better validation, some researchers have taken a different approach to the problem and used formal methods to try to definitively prove properties about the design. These are described next. While this group has made enormous progress, there are still a number of problems when trying to prove properties of real implementations and some of these limitations are also discussed. Though both approaches have significant limitations, using techniques from formal verification to aid simulation looks like a promising new area. One such approach is described in the following chapters, using design examples from the FLASH project.

## 2.1 Design Validation through Simulation

When using simulation for validation, the first question that needs to be answered is how the designer can tell when the simulation is correct, or more to the point, when it is incorrect. This choice of simulation framework can determine the type of validation test vectors that can be used.

There are two common simulation frameworks used for design validation. In the first framework, called the *co-simulation* framework, a second, possibly more abstract, executable model is written without reference to the RTL. This is often called a *golden model*. The two models are then co-simulated using the same set of test vectors and the resulting

operations are compared for equality. The assumption is that a bug in one model will not appear in the other. In other words, bugs will not be correlated in the two models. Hence, every non-equality, or mismatch, is tracked down to discover which model is incorrect. This framework is convenient because the two models check each other's correctness. There is no need to have test vectors that check for specific results, which are difficult to write. Instead, much simpler tests, such as the pseudo-random test vectors that are discussed in the next section, can be used which simply exercise the design. This makes these tests amenable to automatic generation.

However, this framework puts many stringent requirements on the two models being used. The first is that the two models must have state that can be compared for equivalence. This can be difficult to achieve for many designs. If the two models are at different abstraction levels, state that exists in one model may not exist or may not correspond exactly in the other model. For example, an implementation of a design with pipelined operations will likely have state that does not correspond exactly with state in a non-pipelined model of the design.

The second requirement is that there must exist synchronization points at which the corresponding state of the two models can be compared for equivalence. At these points, any transient states of the models have been resolved and comparison can occur. In the simplest cases, a single event can signal such a state, for example, the writeback stage of a processor design. In other cases, the synchronization point is more complex and may involve history of the operations. One natural way to think about synchronization points is to consider them as the end of some abstract operation of the design. The comparison then checks that the operation was performed correctly. This is an especially good perspective if one of the models represents the operation more abstractly than the other. In such a view, complex synchronization points arise because different operations may have different termination events, which can be used to recognize the end of the operation; and they have optimizations that can start the next operation without passing through an idle state. This tends to make the synchronization point a complex condition that needs to examine the history of operations.

The third requirement is that arbitration points in the design match up exactly in the two models for both to perform the same sequence of operations. Specifically, in a design that performs arbitration, the arrival sequence, and possibly arrival times, of data to the

arbitration logic is important to ensure that the two models stay in agreement about the correct operation. If the arbitration point makes different decisions in the two models, all notions of state comparison is lost thereafter. For arbitration logic to make the same decision, at the minimum, it is necessary to preserve the same partial order of data arrival. If the two models are both cycle accurate, this is not too difficult. However, when one model is more abstract than the other, the exact timing of data arrival may be lost in the more abstract model, resulting in different decisions.

With these requirements, making two models agree for all legal input sequences is a difficult task. In many cases, it is tantamount to writing two detailed implementation models. In addition, the two models need to be written without reference to the other for the assumption about uncorrelated bugs to be true. For many designs, creating two models that meet these requirements is prohibitively expensive in terms of resources. So, despite the advantage that test vector creation is simpler with this framework, it is not in widespread use for general circuits. But for circuits where these requirements are met, it can be a very powerful validation tool.

One large class of designs where this framework is feasible and in widespread use is processor designs. For these circuits, instruction-level simulators can be used to compare architectural state, namely the register file, the program counter and the processor status register. The synchronization point is usually when data is written back to the register file. And in general, there are no difficult arbiters in the design. A typical setup of this framework is shown in Figure 1. Such a framework is extremely amenable to pseudo-random and other automatic test vector generation methods.

In the many cases where the co-simulation framework cannot be applied, the second simulation framework, called the *self-checking* framework, can be used, in which test vectors are self-checking. That is, the test vectors are encoded with a way to check for expected results. In this case, only the RTL implementation model is simulated. This removes the need to develop a second model for co-simulation. However, the burden of correctness checking now falls on the test vectors themselves, which must perform checks on expected data values during and at the end of each test to ensure correctness. This has disadvantages: first, it is much harder to write such test vectors that make meaningful checks after complex sequences of operations. These tests are sufficiently hard that it becomes extremely difficult to create an automatic test vector generator. This makes it one

Figure 1. Processor simulation with Instruction-Level-Simulator

of the bottlenecks of current validation efforts. To create a good suite of such self-checking test vectors requires a large team of test writers to work for many months, an expensive, error-prone and time-consuming step in the design process. Secondly, such test vectors will usually require maintenance during the design process to keep up with design changes so that they will continue to provide the correct expected result and that they continue to test the circuit. A third problem is that errors that arise during the test may not show up until long after they occur in the circuit, either because the erroneous result takes a while to show up in state that can be checked, or because tests tend to perform their checks after long sequences of operations. This makes debugging harder. In addition, a related serious disadvantage is that it is possible for errors to arise in the design and not be caught in the checks made by the test vector. In particular, it is difficult to hand-write test vectors that check all possible failure conditions in a non-trivial design. Many errors may actually occur but not get caught with the directed check performed by the test vector.

To address this last disadvantage, RTL simulation in this framework is often supplemented with simulation code, called *snoopers*, that check for error conditions during simulation of the test vectors. Snoopers are simply designer provided checkers that monitor signals and signal combinations in the RTL during simulation. They have the ability to check the detailed operation of the design and can indicate errors close to the source. These are usually not too difficult to write since they are generally localized and small. In addition, unlike a co-simulation model, these checkers do not need to model the expected behavior of the design, they just have to check for obvious errors. Examples are checks for mutual exclusion of signals, absence of unknown, or 'X', values and state consistency checks. Although there is no method to ensure that all possible snoopers have been provided by the designers, they provide valuable additional checks on the design that supplement the self-checks done by the test vectors. A typical set up is shown in Figure 2.

Figure 2. Simulation with Self-Checking Vectors and Snoopers

Given these two general paradigms, the choice of a simulation framework is basically the choice of how to determine correctness of the test vectors that will be simulated. The co-simulation framework generally provides good checking across large parts of a design, but has many difficult requirements that must be satisfied for it to work. If these requirements can be met, this is clearly the better validation framework. An example using this framework is the processor portion of the Stanford FLASH project, which is described in more detail in Chapter 4.

The self-checking framework is much easier to setup initially than a co-simulation one, but suffers from less complete correctness checking, even with the addition of snoopers. However, for many general circuits, excluding processor designs, this is the more common framework in use because of the difficulty of creating a golden model. Since it is difficult to create an automatic self-checking test vector generator, coverage analysis can be performed instead to assist test writers achieve better validation results with this framework, and this is described in Chapter 5.

#### **2.1.1 Validation Test Vectors**

When validating a design with simulation, the quality of the results depends in large part on the test vectors that are run in the simulation. For a bug in the design to be found, the test vectors must exercise the erroneous logic. Good quality directed test vectors are time consuming to produce by hand, but in general, this is the only method of obtaining test vectors that can be used with the self-checking framework. These tests are generally difficult to write because the test writer must have detailed knowledge of the design implementation in order to successfully exercise all the corner cases and subsequently determine what the correct result should be. For complex interactions between multiple control sections of a design, it is even harder to fully consider all possible outcomes and craft tests that can exercise them. The biggest danger is that an important interaction is overlooked and never tested. This is a common mistake that leads to bugs which are only discovered much later in the design process, when it is more expensive to fix. Hence it is important to have a method of determining whether important test cases have been overlooked when using hand-written directed tests.

When a co-simulation framework is used, automatic test vector generators can be utilized to a greater extent. These techniques generally use some form of pseudo-randomization to create many tests from a single test description. There are numerous examples of

test vector generation in this manner: [ABD+91], [ABG+92], [And92], [KN95], [MSY+95] and [WGK90]. These produce random test patterns, which are possibly targeted or *biased* towards certain simulation events. Biasing simply raises the probability of rare events or interactions with the hope of stirring up untested situations. For example, if an input to a design that is being generated has 10 possible values, then a fair distribution would produce each of the possible values with equal likelihood. But if the generator is biased towards 1 of the values, then that value would appear more frequently in the stream of generated values. In this way, the test vectors can be directed towards particular events. These events are normally worry cases identified by the designer as requiring extra testing due to the complexity of the section of logic handling that input value.

Typically, random tests are simulated for hundreds of millions of cycles. When they are usable, that is, when a co-simulation framework is feasible, random generators have the advantage of being relatively simple to set up and can find most of the obvious and many of the complex bugs in a design quickly. A lot of their power stems from the fact that they can generate test interactions not thought of by test writers and designers. This comes about simply because these tests put together lots of random interactions. Over a long period of generation, the probability of exercising many of the complex interactions increases. And in theory, if test generation can proceed indefinitely, all possible interactions should eventually be created. Of course, this is not possible in a real design environment with finite resources. In addition, without some other method to assist, there is no good way to measure the progress of random test vectors in order to estimate when and if certain interactions will get tested. Hence, pseudo-random test vectors, although extremely useful validation tools, are not a systematic method to validate a design.

A second class of automatic test vector generators are constraint based ones, which try to be a little smarter in their choice of random values. The AVPGen system, [CI92], [CIJ+93] and [CIJ+94], uses templates of constraints to create tests that stress a design in corner-cases. The basic idea here is that tests are written in a slightly more abstract form, where exact values of variables and inputs are not fixed in the test description. Instead, constraints are placed on the variables, which are kept symbolically. Test vectors can then be generated from these templates by pseudo-randomly assigning actual values, that meet the constraints, to the symbolic variables. The templates can also be interleaved as directed by the test writer to test event interleavings. A constraint solver is used to resolve constraints from the templates being interleaved to produce a series of new templates

which can then be used for further generation. Typically, various small stress cases are written in the form of test templates. For example, one template may specify a pipelined-microprocessor instruction sequence that forces data-dependencies across cycles. Then, different templates are composed and the constraints of each template are resolved. An actual test sequence is then created by taking the templates and assigning random values to the unconstrained components. This technique can be utilized in both the co-simulation framework and the self-checking one since the basic set of test templates, which are handwritten, may be self-checking.

The power of this technique is that it allows a test writer to think up corner cases and create templates for them. The constraint solver is then responsible for interleaving them and finally assigning actual values to form the test vectors. This late binding of values is powerful because it allows the same templates to be used with many different actual test values. One way to look at this technique is as a method to introduce randomness into hand-written directed tests. The randomness takes the form of different interleavings of templates and the form of different actual values of variables. The shortcoming of this technique is that it still requires design knowledge from humans to create meaningful test templates. It is useful in that the work of each test writer is multiplied into several possible tests, but it still does not provide a method to systematically find all the interactions in a design that need to be tested. This, like all the techniques described so far, leaves open the possibility that important test cases are not exercised with no way to alert the test writer of this fact. The next section talks about techniques to measure validation progress. This is important to validation since the current test vector creation techniques, just described, cannot give any indication of how well they are doing or whether they are testing interesting things.

#### 2.1.2 Measuring Validation

When test vectors are simulated, it is necessary to check whether they really do exercise the design as intended. Sometimes, vectors do not set the necessary conditions, or the design undergoes changes, making the vectors ineffective at testing the interactions they were originally designed for. In addition, the decision to tapeout, though often dependent on market forces, should really be made based on projected completion of the validation task. There are several ways this can be tracked and these are discussed next.

One commonly used method is to track the bug discovery rate and when it becomes flat and low for some length of time, the design is fabricated, [Cla90]. This metric is highly dependent on the quality of the test vectors, since it assumes a constant stream of different, high quality vectors. Only if this is provided will this measure be truly representative of the degree of design completion. The problem is that the rate of creating new, good quality test vectors almost never stays constant. Usually, whenever a new method of test vector creation is tried, a burst of bugs are found since new methods have a good chance of exercising new interactions. As use of the new test creation method matures, the bug rate drops until the next method is introduced. Hence, bug discovery rate is a better productivity measure than a validation completion measure. It certainly does not say anything about which interactions in a design have been tested and which have not.

Other linear metrics, like node-toggle, line, or code-block coverage, used in [And92], [KN95], [WGK90] and [WT95], provide some indication of whether all parts of a design have been tested. Node-toggle coverage measures whether each node in a circuit has been exercised and how often during validation. Clearly, a node that has never toggled indicates logic that has never been tested. In general, this is not good for validation. But even after all nodes have been toggled at least once, this measure can be useful to get a better balance of toggles across nodes in a circuit. This would help ensure that all parts of a circuit received about equal amounts of testing, to a first order.

Line and code-block coverage are similar to node-toggle coverage, except that they measure execution of lines or code-blocks<sup>1</sup> in the RTL description during tests. The information content is fundamentally equivalent to node-toggle coverage. If any line or code-block of the RTL description is not executed, this will generally translate into one or more nodes that do not toggle. One extension to line coverage is branch-taken coverage. This tracks the direction taken at each branch in the RTL code. This provides more information about the behavior of the design. For example, if one code-block can be reached from two different branches, then branch-taken coverage will indicate whether the code-block has been reached from both points, something that line and code-block coverage would not indicate.

<sup>&</sup>lt;sup>1</sup>A code-block is a basic block of the RTL description.

Although these measures are based on the linear coverage of code rather than the function of the design, they provide a good baseline measure of testing completeness. While they cannot indicate accurately whether logic interactions have been tested, they do ensure coverage of basic functionality before such interactions are considered. If these basic measures do not indicate high coverage, then further, more detailed interaction coverage measures as described in Chapter 5, will not provide much additional useful information. They will indicate a slew of missing cases, simply because one basic test may have been missing. In this situation, it is easier to identify the basic case with the basic coverage metrics, then proceed to the complex interactions involving that basic case.

Once basic measures have indicated good coverage, more probing measures can be used to guide the later stages of validation. One such method attempts to measure validation coverage in a manner analogous to the stuck-at faults of manufacturing fault test coverage [KS92]. In this technique, design errors are specified which represent types of errors that may occur in RTL, for example, using the wrong gate in a combinational circuit. This is the analog of stuck-at-faults, which model possible manufacturing defects. A design is analyzed to determine where all the design errors may exist, that is, where each of the design errors could possibly be found in the design. Then, analysis measures how many of the design errors can be detected by a test vector suite. Coverage improves with this technique when test suites are capable of uncovering more of the design errors. Conceptually, this approach is appealing because it tries to identify where errors may occur and then grades the test vectors based on their ability to exercise that code. The largest problem with this approach is developing a credible set of design errors. In fault coverage, the stuck-at fault model has a basis in manufacturing defects, lending credence to the methodology. However, design errors do not have a widely accepted corresponding phenomenon which they model. In addition, it is not clear that exercising all such design errors is feasible using a finite amount of resources.

#### 2.2 Formal Hardware Verification

The previous section described the most common approaches to validation currently available using simulation. The biggest problem is that there is no systematic technique to create test vectors that can exercise all the complex interactions in a design. Coverage analysis can guide test vector creation to areas where more testing is required, but current

techniques provide practical information only up to single FSM arc coverage. Complex interactions can still be missed.

One response to these problems is to use formal verification techniques. These attempt to categorically prove or disprove properties about a design. This is in contrast to validation by simulation, which can never categorically declare a correct design, since a complex design can never be exhaustively simulated. If one of these formal verification methods can be applied, it provides a powerful and definitive statement. However, most have limitations, so it is important to understand when each technique can be applied and what results can be expected.

#### 2.2.1 Reachability Analysis

One of the simplest formal techniques is to take a description of a design and find all the possible states that it can ever get into. This state space exploration [BZ83], provides a straightforward method of exploring the range of possible behaviors of a system and checking whether any of the resulting states violates a *safety property*<sup>2</sup>. This technique is powerful since it checks every reachable state in a system for an error. There is no doubt when this technique returns an answer, unlike validation, which can never return a doubt-free answer of "no errors found". In addition, one of the by-products of the state exploration is usually a sequence from the reset state to any error states, which helps debugging greatly. Such techniques are extremely useful for checking properties of protocols [PD96]. The main drawback is that often, the state space grows too large to handle, a phenomenon known as *state space explosion*. State space explosion occurs because every additional bit added to the state description potentially doubles the state space. There have been techniques developed that can find reductions in the state space that needs to be explored without compromising the property check [IpD93], but these also are best applied to protocol verification.

An alternative to using an explicit representation to store the set of reachable states is to use binary decision diagrams (BDD) [Bry86]. BDDs are a compact and canonical representation of a boolean expression. They can be used to implicitly store the set of reachable states found in state space exploration. When done in this way, reachability analysis is called symbolic because each BDD may represent a large number of states. In many cases,

<sup>&</sup>lt;sup>2</sup>A safety property is an assertion that must hold in every state.

this can extend the size of the state space that can be explored far beyond the size that can be explicitly represented. There are also algorithms that can directly operate on BDDs to formally verify properties, a process known as model checking. Model checking is the verification of properties, some of which may involve paths of the state graph and not just states, against the design. This is utilized with success in [Lon93], [CYF94] and [CGH+95]. In model checking work with BDDs, *temporal logic* properties can also be checked. Temporal logic is a means to express properties which are true over a period of time. These temporal properties look for problems such as *livelock* (no forward progress) and process *starvation* (execution fairness between processes).

Although BDDs have the advantage that they have the potential to represent large numbers of states using very little memory, they too can suffer from a type of explosion. The size of the BDDs needed to represent a design is dependent on the order of the variables in the BDD. With a bad ordering, the size can grow exponentially large. The biggest problem related to this is that it can be very difficult to predict in advance the size of the BDDs required for a particular design. Even relatively small designs can experience a BDD blow-up. This can make the usefulness of BDDs limited unless their use is carefully crafted to preclude this.

#### 2.2.2 Equivalence Checking with Logic

Another formal approach, one that does not attempt to use properties of the state space of a design is the work of [BuD94] and [JDB95]. These attempt to prove the equivalence of two models of a design, one written with implementation details such as pipelines, and one without. Fundamentally, this is a formalization of the co-simulation method of validation, which also compares two models for equivalence. The difference is that this technique attempts to prove it for all possible input values to the design. To reduce the complexity of the task, they use a logic of *uninterpreted functions* to create the two models. An uninterpreted function treats operations, such as add or shift, as black boxes and does not try to evaluate it, which reduces the complexity of the equivalence check. In this way, datapath operations are abstracted, that is, they are not evaluated. Instead, the operation is simply carried along in the logic expression of the operation. A *validity checker*, which decides whether two logic expressions are equal, then proves that the two models are equivalent, thus showing that the implementation (pipelined model) is correct with respect to the specification (unpipelined model).

This work attempts to avoid the state explosion problem of reachability analysis completely. Instead of considering states, it examines possible operations. It is powerful because it can show equivalence for all inputs of a design. However, it is not yet ready for widespread usage for a couple of reasons. First, the explosion problem, though not in terms of states, still arises in checking of equivalence of the logic expressions, which can take a very long time and use a great deal of memory. Secondly, and possibly more importantly, this method requires two models of a design to be written in a special logic. This amount of work seems prohibitively high, especially since some abstraction of the design must occur in order to make the technique feasible. This introduces the possibility of errors being masked or introduced by the abstraction.

Another use of logic has been to utilize *theorem provers* to show that a formal description of the design satisfies a set of properties. A theorem prover takes a description of a design as a set of axioms which state properties of the design. It then accepts queries about other properties which the designer wants to know, for example, whether it is result of an operation can ever be wrong. The theorem prover then uses inference rules to determine the answer to the query. This has been done in [Cyr94] and [MLK96]. These methods are difficult for designers to use because they require familiarity with the logic language and theorem proving techniques. Though powerful, these cannot be utilized in a normal design environment yet.

#### 2.3 Using Formal Techniques in Validation

At the beginning of this chapter, we saw that the hard problem with using simulation for validation is the task of creating good test vectors that can exercise all the complex interactions in a design. None of the current methods can reliably get close to this goal. The first aspect of this problem is just knowing which interactions have been missed by test vectors. Current coverage measures provide basic measures but stop short of being able to accurately identify complex interactions that need to be tested. The end result is that currently, validation tends to be an ad hoc and unreliable method to fully test designs. Formal verification techniques were proposed to solve many of these problems. And although they have made great strides forward, none as yet has shown the capability of handling large design implementations in a general way.

A possible hybrid approach is to try to borrow formal techniques to help the validation task. This holds the possibility that some of the properties of formal verification, such as completeness, can be introduced into validation. Current validation practices lack a good measure of which interactions need testing and which have been tested. One possible approach is to use reachability analysis, or state space enumeration, to quantify the interactions in the control logic of a design. This would provide a definitive and meaningful measure of validation progress. This was done in [HMA95] and [HH96]. In [HMA95], the basic technique is described which extracts the control FSMs from an RTL description. Coverage is then measured in terms of arc coverage of the global control FSM, which is found by symbolic reachability analysis. This provides a comprehensive coverage metric of all the interactions in a design, as will be described in Chapter 3. However, when applied to large designs as in [HH96], this metric turns out to be too conservative. In order to achieve good coverage numbers on this metric, a redundant number of tests need to be simulated. This dilutes the quality of the metric and makes the validation task unnecessarily lengthy. Instead, the common practical implementation of this technique is to measure coverage on single FSMs. Like the basic coverage measures, this is useful and necessary. And like the basic coverage measures, it also does not provide enough information about the complex interactions in a design that need testing. The work in this thesis extends these ideas and attempts to address the issue of deriving a usable, quality coverage metric.

Although the problem of state space explosion arises when state space enumeration is used, validation utilizes the state space information in a less rigid manner than formal verification. This leads to possible reduction and approximation methods that can not be effectively used in formal verification. As will be seen in later chapters, sometimes the exact state space can be reduced and still retain important information for validation. In this way, validation can be guided much more effectively than with any current method. This will be discussed in Chapter 5. But first, the process of extracting useful validation information is described in detail in the next chapter.

# **Chapter 3. Capturing Interesting Test Behaviors**

As the previous chapter showed, the critical problem for simulation based validation is the creation of stimulus vectors that fully exercise the design. This chapter shows one approach for obtaining the needed information for vector generation by extracting the control flow directly from the implementation description. This is done by translating the RTL to a set of cooperating finite-state-machines (FSMs), and consequently finding all the states that are reachable from reset. This global state graph contains *all* the possible behaviors of the design. We focus on trying to exercise the machine through the control state since the control bugs are usually the hardest ones to find, as Section 3.1 shows. To exercise the machine through all possible control interactions is a two step process: extracting the control logic and then finding all possible transitions. These steps are described in Section 3.3 and Section 3.4. Uses of the transition information to generate test vectors and for coverage analysis are described in the following chapters.

#### 3.1 Focus on Control Logic

Common wisdom from practicing hardware designers involved in microprocessor design is that the majority of bugs that were found only after silicon was produced was the result of multiple, rare and unexpected control interactions. The published errata lists for the MIPS R4000 [Mips94] gives some evidence to back this assertion. The errata represent those bugs which not only made it to silicon, but also slipped through to production. These are the bugs that cost the most, both in terms of the cost of an addition spin of silicon and also in terms of delayed time-to-market and are a good target for validation tools.

The bugs can be classified into three categories: the first represent those due to an error in the datapath section of the design; the second due to isolated errors in the control logic; and the third arise when multiple control actions or events occur concurrently. The results of this classification are shown in Table 1.

Table 1. Errata Classification of MIPS R4000

| Bug Class                   | Number of | % of Total |

|-----------------------------|-----------|------------|

|                             | Bugs      |            |

| Pipeline/Datapath ONLY bugs | 3         | 6.5%       |

| Single Control Logic Bugs   | 17        | 37.0%      |

| Multiple Event Bugs         | 26        | 56.5%      |

| Total Reported Errata       | 46        | 100.0%     |

Multiple event bugs are difficult to find because they require several control interactions to occur in a particular sequence or with some specific timing relation. Creating test vectors that can exercise *all* such situations is difficult with random-generators and nearly impossible when hand-written. Given the large number of difficult bugs that occur due to control interactions, we target our validation tools to try to cover this area more completely.

## 3.2 Validation Methodology based on Control Interactions

The approach described here is to capture the control logic description from the RTL description. This is then used to find all the possible control interactions in the logic. And finally, this information can be used for validation: either test vector generation or coverage analysis based on control interactions. These steps are shown in Figure 3.

In the first step, the **translator** extracts the pertinent control logic FSMs from an RTL description written in Verilog. The assumption made here is that the Verilog already has a coarse partitioning for synthesis into control and datapath sections. Verilog that does not satisfy this assumption can be translated, but would require more designer input to ensure that a good partition of control and datapath is obtained. Then, to extract the minimal control logic from the control section, the user is asked to annotate the Verilog further with comment-embedded directives that highlight some of the important state variables in the control logic. The translator then applies a *transitive fan-in* algorithm to capture the logic which those state variables depend on. The transitive fan-in algorithm simply finds all the

Figure 3. Validation Methodology based on Control Interactions

logic that sets the value of the highlighted state variables. It then iterates, looking for the logic that sets that logic and so forth. The process stops at the module boundary of the control logic, based on the coarse partitioning for synthesis. The extracted logic is then combined with a description of the environment of the FSM model.

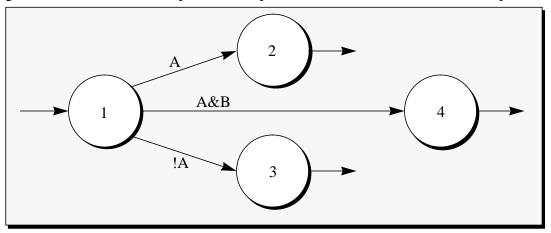

The environment acts as an input generator to the FSM model of the control logic. In general, these inputs are either primary inputs to the design, or they represent signals from the datapath, which is not captured by the translator. The most general environment is one which generates any input at any time, known as a *non-deterministic* environment. In the

context of finding the global state-graph, non-determinism means trying all possible input sequences in all cycles, shown in Figure 4.

Figure 4. Non-deterministic Environment

The non-deterministic (ND) environment can also provide an abstraction of the interface. For example, a 32-bit address to a cache in a processor design can often be abstractly represented by an ND environment that provides a single bit indicating whether the address will cause a hit or a miss in the cache. This models the control logic effects of the address on the cache by a single bit, as illustrated by the *CacheMiss* signal shown in Figure 4. This often simplifies the control logic model of a design. This is discussed in more detail later in this chapter. The ND environment provides the most generality since it captures all possible behaviors of the FSM model. If a test vector suite manages to exercise all interactions of the FSM model under the full ND environment, we can conservatively assume good coverage of the control interactions. As we will see in Section 5.4, sometimes the ND environment is too general and leads to control behaviors that are not possible in the hardware. When this situation arises, extra constraints can be placed on the environment in the form of input generators that do not take all possible values on every cycle.

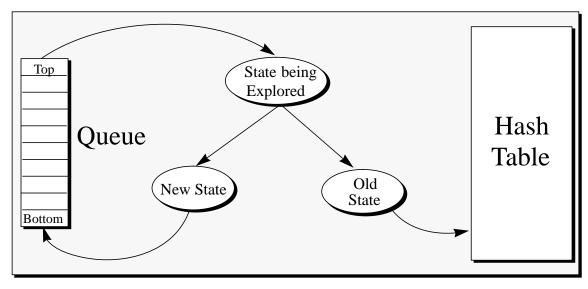

The second step of the methodology is state space exploration of the control FSMs. For this, the FSM description language used is a descendant of Murφ [DDH+92] called

MPP (Mur $\phi$  ++). MPP takes the FSM description of the system and finds all its reachable states from reset. It produces a global state graph and hash table of states which are used in the third step. These first two steps serve to capture the control logic interactions and are described in detail in Section 3.3 and Section 3.4.

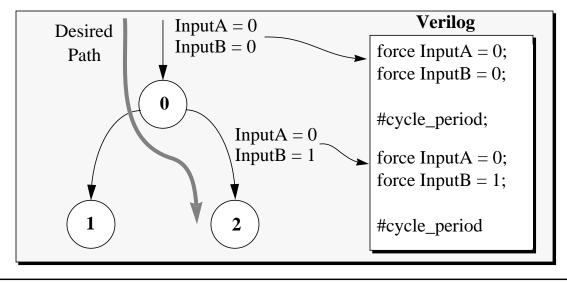

The third step in the toolset uses the control logic interactions to either generate test vectors or to perform coverage analysis. To generate vectors, paths through the control graph are found that improve the testing coverage. Each edge of this path results in the generation of a single test vector. This process and algorithm are presented in Chapter 4.

To calculate coverage, the program reads state dumps from a test suite run in simulation on the RTL. These state transitions are marked on the control graph and the individual state variables, giving a coverage metric. Detailed feedback is given to the designers in the form of transition edges not exercised. This process and some of the practical problems encountered applying this algorithm to the models in the FLASH project are described in Chapter 5.

#### 3.3 RTL-to-FSM Translation

One shortcoming of many of today's formal verification techniques is that many require re-writing the design in a particular language. This introduces the possibility that errors are missed or introduced in the translation step. This is especially true where the translation also incorporates an abstraction step. The possibility of error in the translation step can be avoided with the use of an automatic translator, as used in the HSIS and VIS suite of tools [Ber93], [CYB93]. These translate a model written in a hardware description language (HDL), such as Verilog [TM91], to intermediate languages used in further processing. Direct translation offers a more faithful representation of the design, as well as the ability to more easily track changes.

Hence, the first step in capturing control logic interactions is to translate the Verilog description of the design into an FSM modeling language<sup>1</sup>. The translator takes synthesizable Verilog as input, and produces MPP code as output. For the most part, translation

<sup>&</sup>lt;sup>1</sup>This work also focussed on Verilog as the RTL description language. The other commonly used alternative is VHDL [Ash96]. Conceptually, the only requirements for a VHDL front-end to the methodology is synthesizability of the design.

between structural Verilog and MPP is a straightforward syntactic rewrite. The subset and style of Verilog that is accepted by the translator is similar to the subset that would synthesize well using Synopsys tools. Transparent latches, as well as edge-triggered flops, are recognized. However, there are a few semantic issues that require some care to ensure correct translation of the control logic.

#### 3.3.1 Semantic Issues

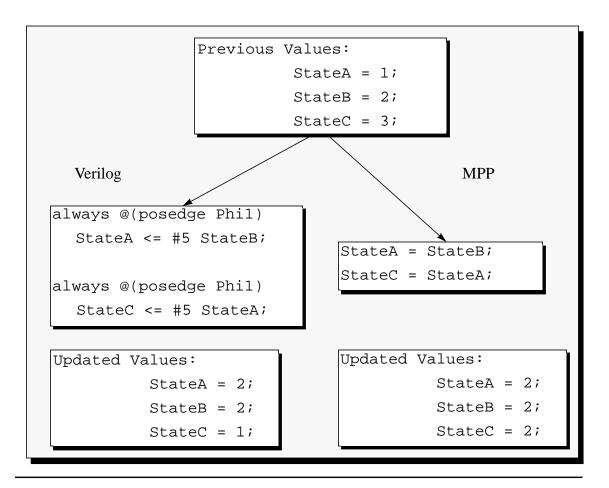

The most important semantic issue is to ensure that the event-based concurrency model of Verilog is preserved when going to MPP, which has a cycle-based concurrency model. In Verilog, when a variable changes value, an event is posted to the simulator. If any other variables are *sensitized* to, or dependent on, that value, they will be updated and further events posted. In this way, textual ordering of assignments is made irrelevant to the concurrency model. Where this matters is assignment to a state variable. In Verilog, assignment to a reg data type is potentially capable of holding state. If coded correctly (without a race condition), state assignments should also be made so that they are independent of textual order<sup>2</sup>. However, in MPP, assignments are evaluated once, in their textual order, every cycle. This may lead to problems if a state-variable is directly used as an input to another state-variable assignment, as shown in Figure 5.

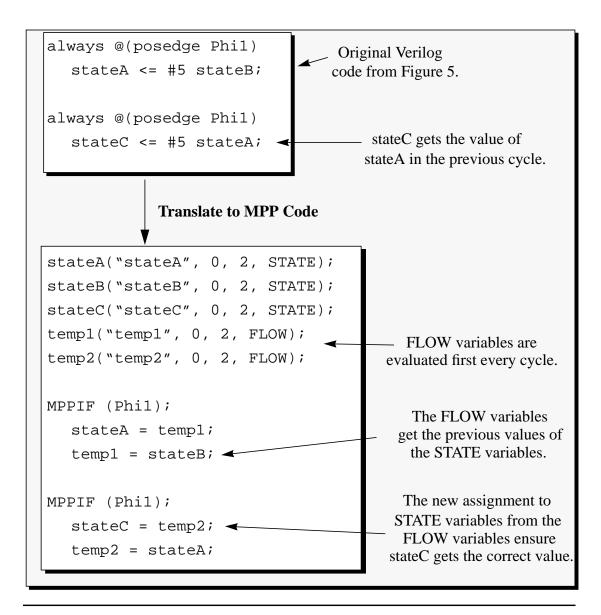

The intended behavior of the Verilog is for simultaneous assignments to *StateA* and *StateC*. A straightforward translation to MPP would result in the wrong concurrency model. However, MPP does give the correct concurrency model for non-state variables, that is, assignments to *wires* are independent of textual ordering, and wire assignments are always evaluated before *any* state assignments are done. This provides the fix for the above problem. If the translator ensures that a *wire* appears between every state-assignment, we get the desired behavior where every state assignment occurs simultaneously using the previous values for other state-variables. Hence, if the translator ever finds a state variable read directly by another state variable in the Verilog, it inserts a wire assignment in between, as shown in Figure 6. Since MPP evaluates its wire variables (called FLOW) prior to its state variables, this results in all state assignments using the previous values of state variables that appear in the right-hand-side. Although this example is specific to MPP as an FSM enumeration tool, the underlying problem is preservation of an

<sup>&</sup>lt;sup>2</sup>If not, different simulator implementations may result in different results. For transparent latches, this is done by sensitizing the assignment to all variables that it depends on. For edge-triggered flops, this is done by using a non-blocking delayed assign.

Figure 5. Problematic MPP State Assignment

event-based concurrency model when translating to some other concurrency model. This issue will arise in some form with most FSM enumeration tools.

The translator must also be able to infer all state assignments in Verilog because MPP requires that state variables are explicitly defined. There are several ways in which a variable can be made to hold state. As part of the coding style adopted, all state elements were required to be either:

- transparent latches encoded with a fully-sensitized always block, or

- edge-triggered flops encoded with a non-blocking, delayed assignment.

The general semantic issue is identification of state. This is also the primary reason the translator is restricted to a synthesizable subset of Verilog. With this restriction, all state, explicit or implied, can be inferred from the structural equivalent of the description.

Figure 6. Breaking up state-to-state assignments in MPP

However, an unsynthesizable description may contain implicit state encoded as delays, that is, state is created by placing long delays between assignment statements to the same variable. Such a coding style is described as *behavioral* and can not, in general, be synthesized automatically. For exactly the same reasons, the RTL translator cannot generally infer state in such a description, hence behavioral descriptions cannot be used as input to the methodology.

```

always @(Phil or condition or input)

if (Phil & condition)

latch = input;

always @(Phil)

if (condition)

latch <= #5 input;

```

Figure 7. Code examples of transparent latch (a) and edge-triggered flop (b).

### 3.3.2 Identifying Control-Logic

A harder task for the translator is determining which parts of the RTL description are required for the control logic FSM modeling. We assume that the RTL we get from the designers already has a coarse level of partitioning between control logic and datapath, which has been done for synthesis. However, even within the control sections, not all the logic present is required to create the FSM model. For example, there may be some logic that takes an output from an FSM and modifies it to control a datapath element. This additional information might not be wanted in the FSM description, which focuses on the logic that determines possible next state values.

To capture only the logic that directly determines the next state function, a *transitive* fan-in algorithm is used. For this, the designer is asked to point out some of the important state variables in the RTL by annotating the Verilog with comment-embedded directives. The annotation is done once for a design and as long as changes to the design are not too drastic, it remains constant for a particular FSM model. An example of the non-intrusive annotation is shown in Figure 8. In general, only the state variables of the major FSM need to be annotated. These are usually assigned values in switch statements in code destined for synthesis.

The transitive fan-in algorithm is given in Figure 9. It maintains a stack of variables that are found to be *required* by the FSM logic. Initially, only variables that are named in the annotations are placed in the *required* stack. It also maintains a *provided* set, which

```

// v2m:state stateVar_x

always @(posedge Phil) begin

switch (presState_v) begin

case 'IDLE:

if (CacheMiss_v)

stateVar_x = 'MISS_START;

else

stateVar_x = 'IDLE;

```

Figure 8. State Annotation Example

holds the variables that have already been included in the translated logic. As each variable is popped from the *required* stack and placed in the *provided* set, the algorithm scans the RTL searching for other variables that help determine its next value. Each of these is compared to the set of variables already found and placed in the *provided* set. Any variable not already in the *provided* set is added to the *required* stack. This continues until the stack is empty. All logic that sets the value of a variable in the *required* set is translated. The net effect of the transitive fan-in algorithm is that all logic that determines the next-state value of the annotated variables is translated, up to the module boundary. The algorithm stops at the module boundary because this acts as a natural *abstraction* interface. Abstraction is discussed in the next section.

If multiple modules are translated together, some cross-module checking of dependences is performed. In particular, if one module requires a signal as an input and it is generated by another module, a dependence is created. The logic in the other module for that signal is labeled *required* even if it was not otherwise needed. In this way, only signals that represent inputs from the datapath or external environment are left to be driven by the environment.

## 3.3.3 Abstracting the Design

The inputs to the FSM model specified by the transitive fan-in algorithm and not generated by logic within some other module must be driven by the non-deterministic (ND) environment. The ND environment provides an abstract model of the datapath and external signals that is more general than the real hardware. In other words, it generates more

```

/* Transitive Fan-In Algorithm */

initialize REQUIRED queue to NULL;

initialize PROVIDED set to NULL;

do {

current var = POP top of REQUIRED queue;

/* If we popped a var, mark it as provided. */

if (current_var != NULL) {

Add current_var to PROVIDED set;

}

for (each RTL statement) {

switch (statement type) {

case ANNOTATION: push variable onto REQUIRED queue;

/* User specified state variable */

case CONTINUOUS_ASSIGNMENT:

case PROCEDURAL_ASSIGNMENT: {