Computer Systems Laboratory

Department of Electrical Engineering Stanford University, CA 94305

Efficient Multiprocessor Communications: Networks, Algorithms, Simulation, and Implementation

Yen-Wen Lu

July 1996

Technical Report No. CSL-TR-96-699 (Technical Report No. STAR-1DEH694-1996-1)

# Efficient Multiprocessor Communications: Networks, Algorithms, Simulation, and Implementation

By Yen-Wen Lu July 1996

Technical Report No. CSL-TR-96-699 (Technical Report No. STAR-1DEH694-1996-1)

> Department of Electrical Engineering Stanford University, CA 94305

© Copyright by Yen-Wen Lu 1996 All Rights Reserved This report constitutes a Ph.D. dissertation submitted to Stanford University.

# Abstract

As technology and processing power continue to improve, inter-processor communication becomes a performance bottleneck in a multiprocessor network. In this dissertation, an enhanced 2-D torus with segmented reconfigurable bus (SRB) to overcome the delay due to long distance communications was proposed and analyzed. A procedure of selecting an optimal segment length and segment alignment based on minimizing the lifetime of a packet and reducing the interaction between segments was developed to design a SRB network. Simulation shows that a torus with SRB is more than twice as efficient as a traditional torus.

Efficient use of channel bandwidth is an important issue in improving network performance. The communication links between two adjacent nodes can be organized as a pair of opposite uni-directional channels, or combined into a single bi-directional channel. A modified channel arbitration scheme with hidden delay, called "token-exchange," was designed for the bi-directional channel configuration. In spite of the overhead of channel arbitration, simulation shows that bi-directional channels have significantly better latency-throughput performance and can sustain higher data bandwidth relative to uni-directional channels of the same channel width. For example, under 2% hot-spot traffic, bi-directional channels can support 80% more bandwidth without saturation compared with uni-directional channels.

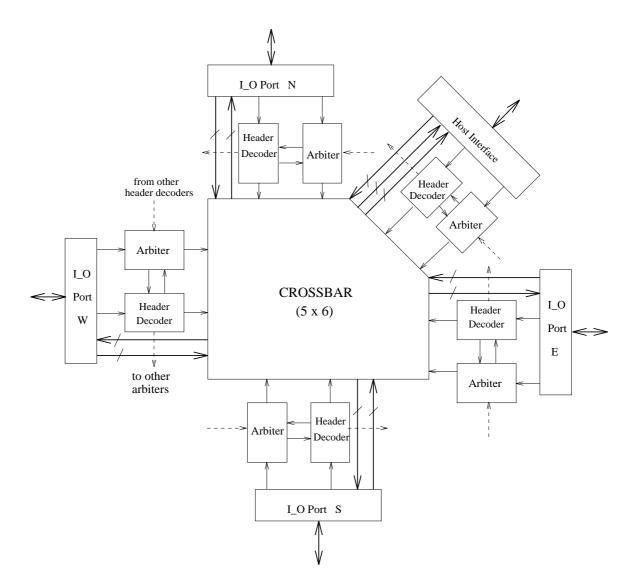

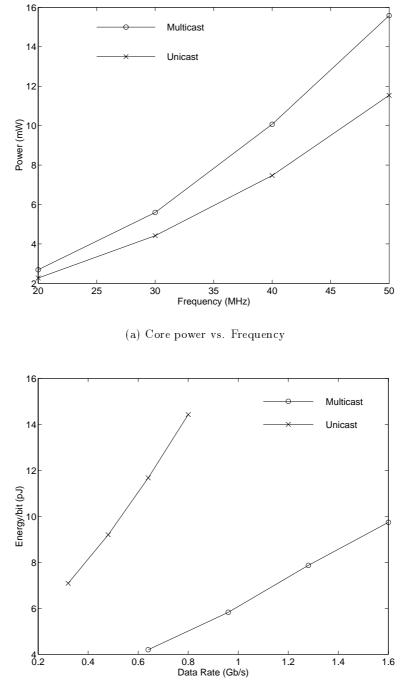

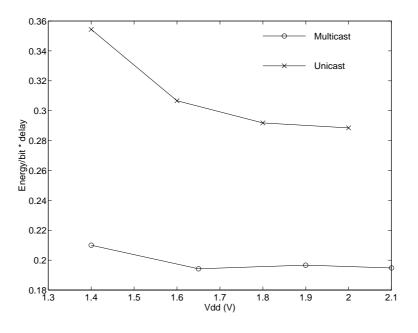

An efficient, low power, wormhole data router chip for 2-D mesh and torus networks with bi-directional channels and token-exchange arbitration was designed and implemented. The token-exchange delay is fully hidden and no latency penalty occurs when there is no traffic contention; the token-exchange delay is also negligible when the contention is high. Distributed decoders and arbiters are provided for each of four IO ports, and a fully-connected  $5 \times 6$  crossbar switch increases parallelism of data routing. The router also provides special hardware such as flexible header decoding and switching to support path-based multicasting. From measured results, multicasting with two destinations used only 1/3 of the energy required for unicasting. The wormhole router was fabricated using MOSIS/HP 0.6 $\mu$ m technology. It delivers 1.6Gb/s (50MHz) @ Vdd=2.1V, consuming an average power of 15mW.

# Acknowledgments

I would like to thank my parents, to whom this dissertation is dedicated, for their unconditional support throughout my education. Without their encouragement, it would not be possible for me to achieve my goals.

I would like to express my deepest gratitude to my advisors, Professor Allen Peterson and Professor Len Tyler. Professor Peterson had given me a tremendous amount of support and guidance during my first three years at Stanford. Professor Tyler has been very patient with me for preparing my oral defense and this dissertation. I especially thank him for the time and effort he put into helping me clarify and correct many important points in this dissertation. I would like to thank Professor Michael Godfrey for letting us use his laboratory to do the chip testing and for helping us resolve all the related problems. I would also like to thank Professor Teresa Meng, Professor John Gill, and Professor Fabian Pease for serving in my reading and oral committees.

I have been fortunate to work with my colleagues in the Space, Telecommunications, and Radioscience Laboratory, and the Ultra Low Power group. Jim Burr has helped me a great deal in the direction of my research and projects. Gerard Yeh, my partner of the STARP project, is always eager to help me solve problems, and it is a pleasant experience to work with him. I would like to thank Bevan Baas for many discussions of all different topics. I would also like to thank the visiting scholars, Masataka Matsui and Kallol Bagchi, for broadening my background and knowledge.

Last but not least, I would like to thank my wife, Woan-Yu, for her loving support and understanding. She has accompanied me for countless hours to finish my projects over the last few years.

My research was supported by Intel, NASA, Toshiba, and the department of Electrical Engineering, Stanford University. They are all gratefully acknowledged.

# Contents

| A        | bstra          | $\mathbf{ct}$                                    | iv |

|----------|----------------|--------------------------------------------------|----|

| A        | cknov          | wledgments                                       | v  |

| 1        | Intr           | oduction                                         | 1  |

|          | 1.1            | Multiprocessor Speedup                           | 2  |

|          |                | 1.1.1 Speedup with a fixed load                  | 2  |

|          |                | 1.1.2 Speedup with fixed execution time          | 3  |

|          | 1.2            | Multiprocessor Networks                          | 5  |

|          | 1.3            | Multiprocessor Communications                    | 5  |

|          | 1.4            | An Overview of the Research                      | 7  |

| <b>2</b> | $\mathbf{Net}$ | work Interconnection                             | 9  |

|          | 2.1            | Properties of Network Topology                   | 9  |

|          | 2.2            | Network Examples                                 | 11 |

|          | 2.3            | Network Category                                 | 15 |

| 3        | Rou            | nting Flow Control                               | 19 |

|          | 3.1            | Desired Routing Properties                       | 19 |

|          | 3.2            | Routing Flow Control Schemes                     | 21 |

|          | 3.3            | Virtual Channel                                  | 24 |

|          |                | 3.3.1 Virtual Channel Configuration              | 25 |

|          |                | 3.3.2 Dynamically Allocated Multi-Queue          | 26 |

|          | 3.4            | Uni-directional versus Bi-directional Channel    | 27 |

|          |                | 3.4.1 Token Exchange for Bi-directional Channels | 27 |

| 4 | Wo             | ormhole Routing Algorithms                           | 31 |

|---|----------------|------------------------------------------------------|----|

|   | 4.1            | Deterministic Routing                                | 33 |

|   | 4.2            | Fully Adaptive Routing                               | 35 |

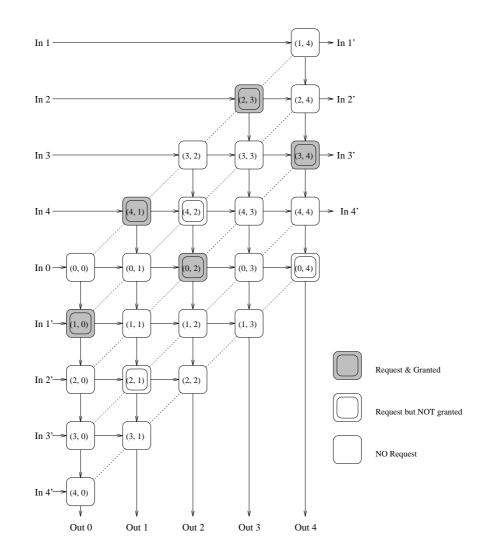

|   |                | 4.2.1 Virtual Network Algorithm                      | 37 |

|   |                | 4.2.2 Dimension Reversal Algorithm                   | 41 |

|   |                | 4.2.3 Star-Channel Algorithm                         | 43 |

|   |                | 4.2.4 Extended Channel Dependency                    | 44 |

|   | 4.3            | Partially Adaptive Routing                           | 48 |

|   |                | 4.3.1 Planar Algorithm                               | 48 |

|   |                | 4.3.2 The Turn Model                                 | 49 |

|   | 4.4            | Randomized Routing                                   | 51 |

|   | 4.5            | Multicast Routing                                    | 54 |

|   |                | 4.5.1 Unicast-based Multicasting                     | 55 |

|   |                | 4.5.2 Tree-Based Multicasting                        | 55 |

|   |                | 4.5.3 Path-Based Multicasting                        | 58 |

| 5 | Wo             | ormhole Routing Simulation                           | 61 |

|   | 5.1            | Simulation Models                                    | 61 |

|   |                | 5.1.1 Network Model                                  | 61 |

|   |                | 5.1.2 Node Model                                     | 62 |

|   |                | 5.1.3 Link Model                                     | 66 |

|   |                | 5.1.4 Traffic Model                                  | 67 |

|   | 5.2            | Simulation Flow                                      | 67 |

|   | 5.3            | Performance Measurement                              | 68 |

|   | 5.4            | Simulation Results                                   | 69 |

| 6 | $\mathbf{Seg}$ | gmented Reconfigurable Bus                           | 87 |

|   | 6.1            | SRB Architecture Overview                            | 88 |

|   | 6.2            | Routing Algorithms for Different Torus Architectures | 89 |

|   |                | 6.2.1 Torus with Links Only                          | 89 |

|   |                | 6.2.2 Torus with Global Buses                        | 89 |

|   |                | 6.2.3 Torus with Reconfigurable Buses                | 92 |

|   |                | 6.2.4 Torus with Segmented Reconfigurable Buses      | 93 |

|   | 6.3            | Interconnection Delay                                | 94 |

|   |     | 6.3.1  | Link model                     | 95 |

|---|-----|--------|--------------------------------|----|

|   |     | 6.3.2  | Long wire model                | 96 |

|   |     | 6.3.3  | Bus model                      | 96 |

|   |     | 6.3.4  | Transmission gate model        | 97 |

|   |     | 6.3.5  | Repeater model                 | 98 |

|   |     | 6.3.6  | Delay Comparison               | 99 |

|   | 6.4 | SRB Si | imulation and Comparison       | 01 |

|   |     | 6.4.1  | Simulation Results             | 05 |

|   |     | 6.4.2  | Discussion                     | 06 |

|   | 6.5 | SRB O  | ptimization                    | 08 |

|   |     | 6.5.1  | Optimal Segment Length         | 08 |

|   |     | 6.5.2  | Optimal Segment Alignment      | 10 |

|   | 6.6 | Summa  | ary                            | 15 |

| _ |     |        |                                |    |

| 7 |     |        | 5                              | 19 |

|   | 7.1 |        |                                | 19 |

|   |     |        |                                | 19 |

|   |     |        |                                | 20 |

|   | 7.2 |        | 0                              | 22 |

|   | 7.3 |        |                                | 22 |

|   |     |        |                                | 23 |

|   |     |        |                                | 24 |

|   |     |        |                                | 25 |

|   | 7.4 |        |                                | 26 |

|   |     | 7.4.1  |                                | 26 |

|   |     | 7.4.2  |                                | 28 |

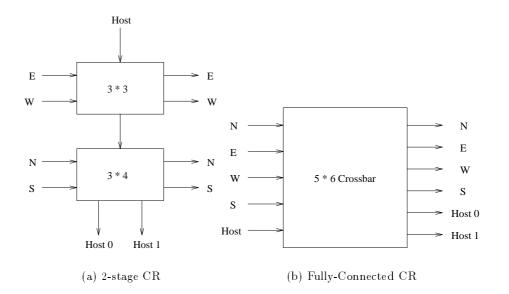

|   |     | 7.4.3  | Crossbar Switch Architecture 1 | 32 |

|   | 7.5 | Router | Timing 1                       | 34 |

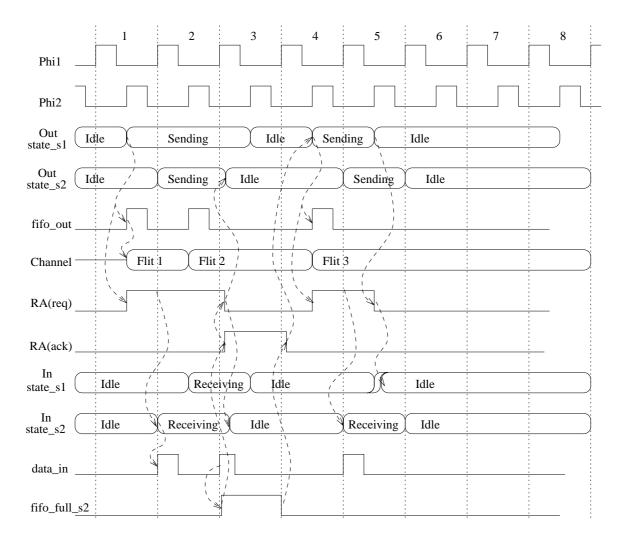

|   |     | 7.5.1  | I/O Timing 1                   | 34 |

|   |     | 7.5.2  | Router Core Timing 1           | 38 |

|   | 7.6 | Router | Instruction Sets               | 42 |

|   |     | 7.6.1  | Status Instructions            | 43 |

|   |     | 7.6.2  | Packet Instructions            | 44 |

| R | efere | nces   |                                      | 164 |

|---|-------|--------|--------------------------------------|-----|

|   | 8.2   | Sugge  | stions for Future Work               | 162 |

|   | 8.1   |        | ibutions                             |     |

| 8 | Cor   |        | ions and Suggestions for Future Work | 161 |

|   | 7.9   | Summ   | ary                                  | 190 |

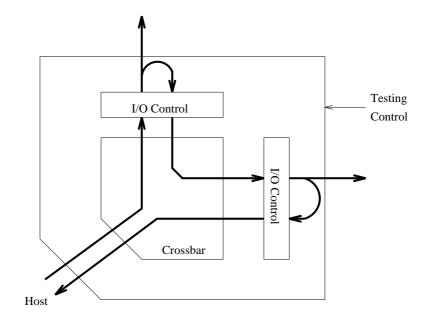

|   | 7.0   |        | Testing Results                      |     |

|   |       |        | -                                    |     |

|   |       | 7.8.2  | Tester Setup                         |     |

|   |       | 7.8.1  |                                      |     |

|   | 7.8   | Testin | g Issues                             | 153 |

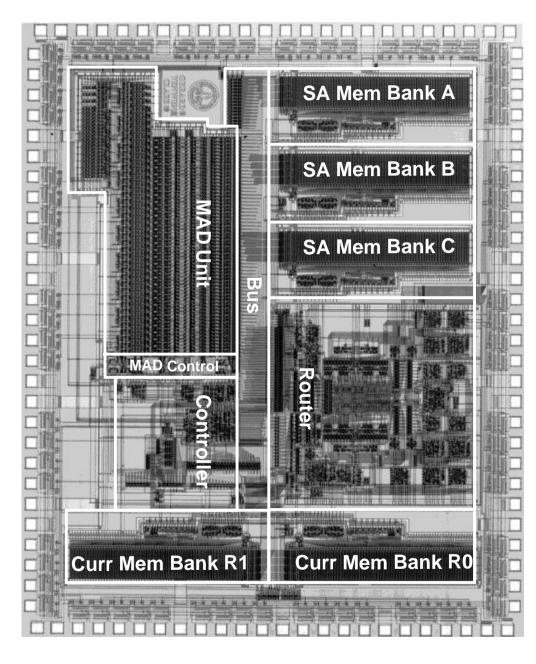

|   |       | 7.7.3  | Chip Fabrication                     | 153 |

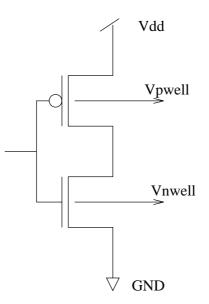

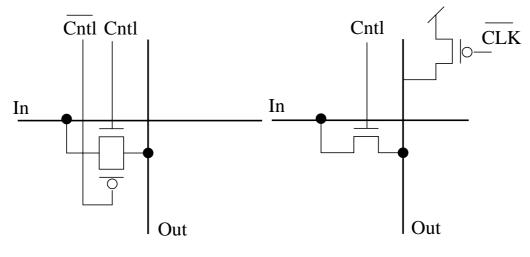

|   |       | 7.7.2  | Circuit Issues                       | 149 |

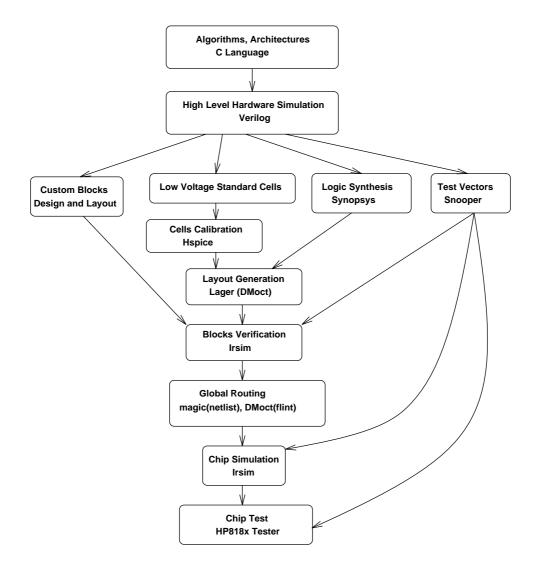

|   |       | 7.7.1  | Design Methodology                   | 147 |

|   | 7.7   | Chip I | Implementation                       | 147 |

|   |       | 7.6.3  | Instruction Examples                 | 145 |

# List of Tables

| 2.1 | Summary of network properties                                                         |

|-----|---------------------------------------------------------------------------------------|

| 2.2 | Topologies of existing parallel systems                                               |

| 5.1 | Virtual channel buffer allocation for different routing algorithms in a 2-D torus. 71 |

| 6.1 | Comparison of different torus architectures                                           |

| 6.2 | Alignment metric $\eta$ , $\alpha = .5$ , $\beta = 2$ , $N = 60$ , segment length=15  |

| 6.3 | Average latency (completion steps), $N = 60$ , segment length=15, buffer size=10.117  |

| 6.4 | Optimal segment alignment for different segment length                                |

| 7.1 | Topologies of existing parallel systems                                               |

| 7.2 | Some previous wormhole router designs                                                 |

| 7.3 | Comparison of 2-stage CR and fully-connected CR 133                                   |

| 7.4 | Summary of status instructions modes 144                                              |

| 7.5 | Estimated power and area allocation of the router in STARP 159                        |

| 7.6 | STARP wormhole router summary                                                         |

# List of Figures

| 1.1 | Amdahl's Law. Speedup with a fixed load                                                   | 3  |

|-----|-------------------------------------------------------------------------------------------|----|

| 1.2 | Gustafson's Law. Speedup with fixed time                                                  | 4  |

| 1.3 | Multiprocessor networks                                                                   | 5  |

| 1.4 | Total execution time is composed of computation time and communication time               | 6  |

| 1.5 | An example of traffic contention.                                                         | 7  |

| 2.1 | Linear Array and Ring                                                                     | 11 |

| 2.2 | Tree Networks                                                                             | 12 |

| 2.3 | Hypercube and CCC                                                                         | 13 |

| 2.4 | 2-D Mesh and Torus                                                                        | 14 |

| 2.5 | Bus Networks                                                                              | 15 |

| 2.6 | Some multi-stage networks examples                                                        | 16 |

| 2.7 | Crossbar Network                                                                          | 16 |

| 3.1 | An example of deadlock                                                                    | 20 |

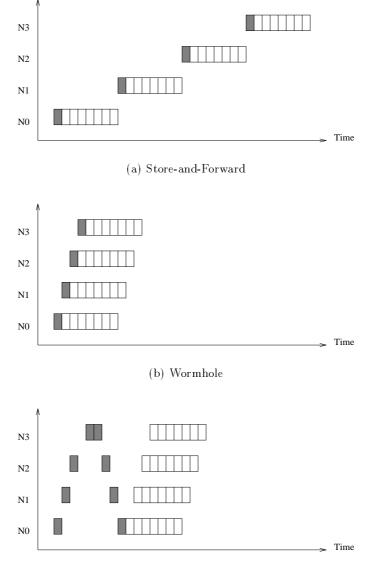

| 3.2 | Latency comparison of different flow control schemes $\ldots \ldots \ldots \ldots \ldots$ | 23 |

| 3.3 | FIFO queue configurations.                                                                | 25 |

| 3.4 | Channel configuration                                                                     | 28 |

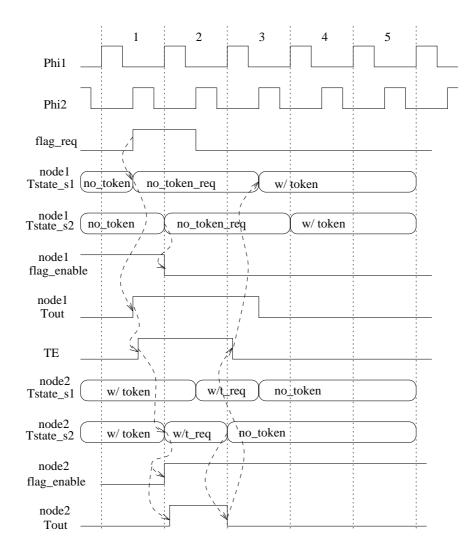

| 3.5 | Token exchange state diagram                                                              | 29 |

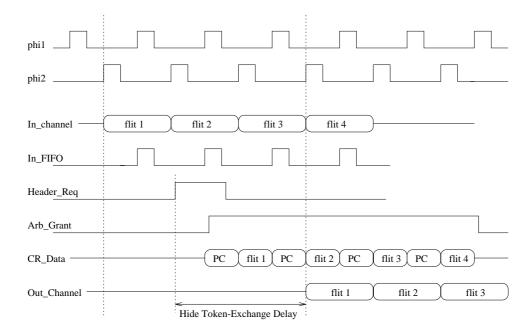

| 3.6 | Token exchange timing diagram                                                             | 29 |

| 4.1 | Channel $c_i$ has a source node $s_i$ and destination node $d_i$                          | 31 |

| 4.2 | Relation between network graph $G$ and channel dependency $D.\ldots\ldots\ldots$          | 33 |

| 4.3 | Deadlock avoidance by adding virtual channels                                             | 34 |

| 4.4 | Examples of dimension-order routing in a 2-D torus                                        | 36 |

| 4.5 | Two virtual networks in a 2-D torus                                                       | 38 |

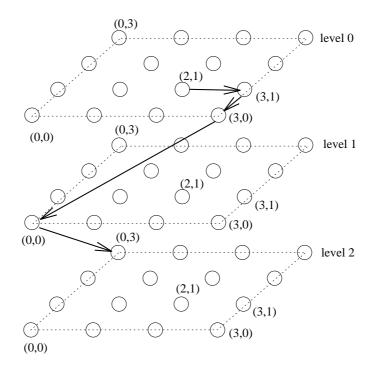

| 4.6  | Expanding a virtual network to three logical levels in a 2-D torus                           | 38 |

|------|----------------------------------------------------------------------------------------------|----|

| 4.7  | Examples of Virtual Network routing on the negative network in a 2-D torus.                  | 40 |

| 4.8  | A packets is routed from $(2,1)$ to $(0,3)$ on the negative virtual network in a             |    |

|      | 2-D torus                                                                                    | 41 |

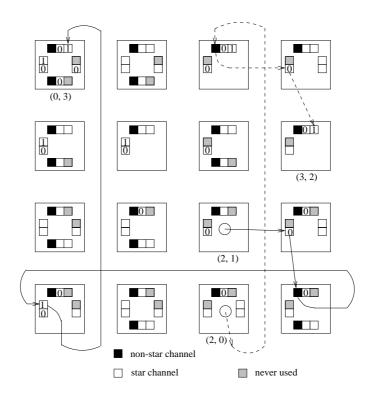

| 4.9  | Examples of Star-Channel routing in a 2-D torus                                              | 45 |

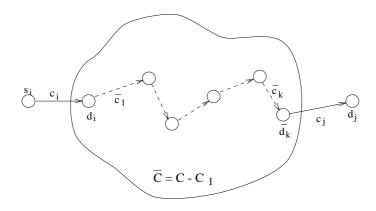

| 4.10 | Indirect channel dependency from $c_i$ to $c_j$                                              | 47 |

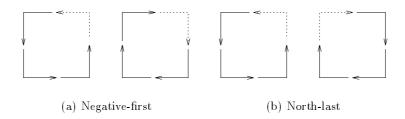

| 4.11 | Two different possible ways to break cyclic dependency in a 2-D mesh                         | 50 |

| 4.12 | Examples of paths for the <i>negative-first</i> algorithm of the Turn model in a 2-D         |    |

|      | $\mathrm{mesh}$                                                                              | 50 |

| 4.13 | Derouting in a 2-D array when a packet is blocked. $\ldots$ $\ldots$ $\ldots$ $\ldots$       | 52 |

| 4.14 | Latency penalty due to derouting in a 16 $	imes$ 16 2-D torus $\ldots$                       | 55 |

| 4.15 | Examples of different multicasting schemes                                                   | 56 |

| 4.16 | Deadlock configuration in tree-based multicasting                                            | 58 |

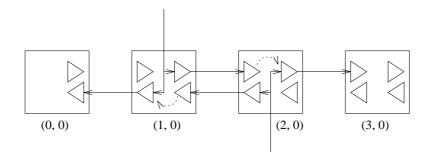

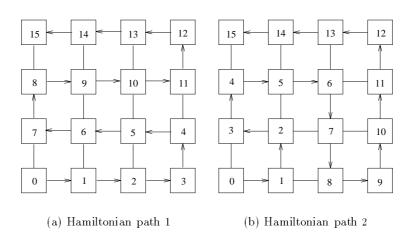

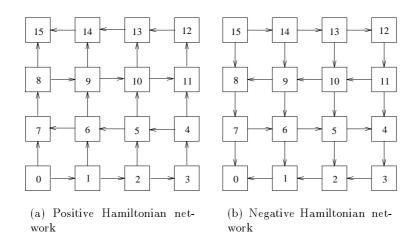

| 4.17 | Two different mapping to construct Hamiltonian paths in a 2-D mesh $\ldots$ .                | 59 |

| 4.18 | Partition of a 2-D mesh based on the Hamiltonian path                                        | 60 |

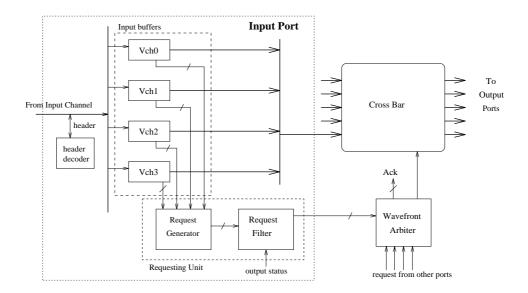

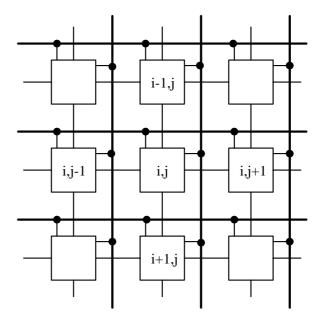

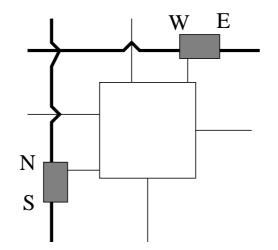

| 5.1  | Internal router node architecture model                                                      | 63 |

| 5.2  | Wavefront arbitration.                                                                       | 65 |

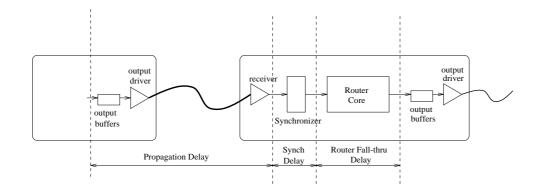

| 5.3  | Link model                                                                                   | 66 |

| 5.4  | Simulation Flow                                                                              | 69 |

| 5.5  | Delay components in the simulation model                                                     | 70 |

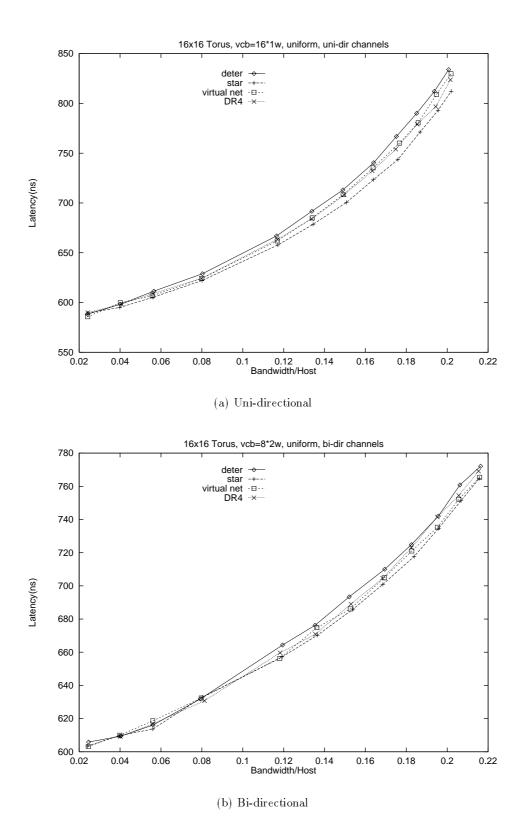

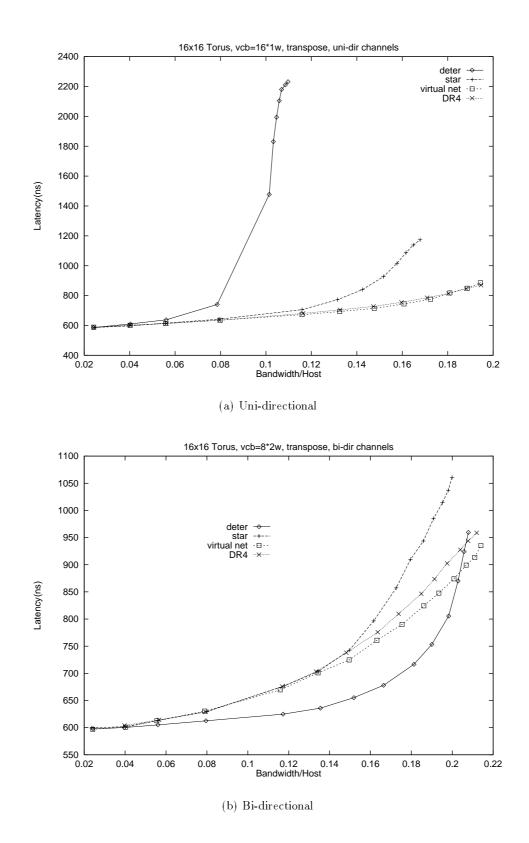

| 5.6  | Latency versus throughput for different routing algorithms under uniform ran-                |    |

|      | dom traffic                                                                                  | 76 |

| 5.7  | Latency versus throughput for different routing algorithms under transpose                   |    |

|      | traffic                                                                                      | 77 |

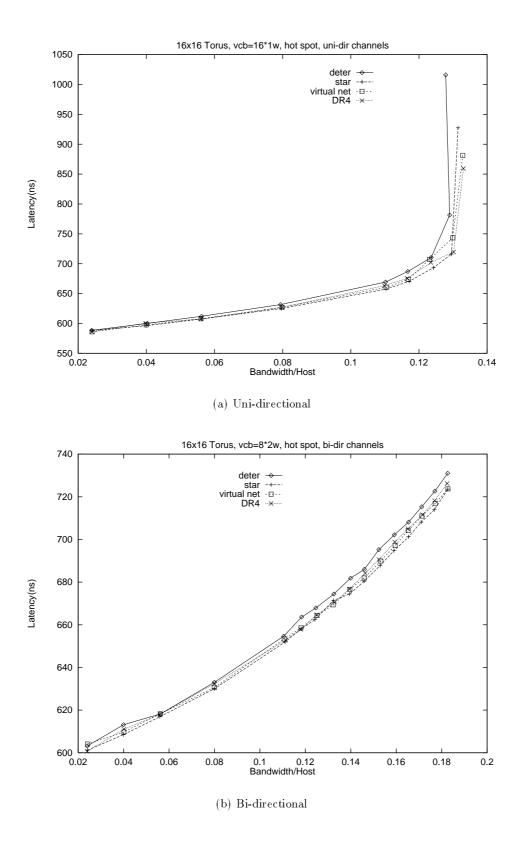

| 5.8  | $Latency\ versus\ throughput\ for\ different\ routing\ algorithms\ under\ Hot-spot\ traffic$ | 78 |

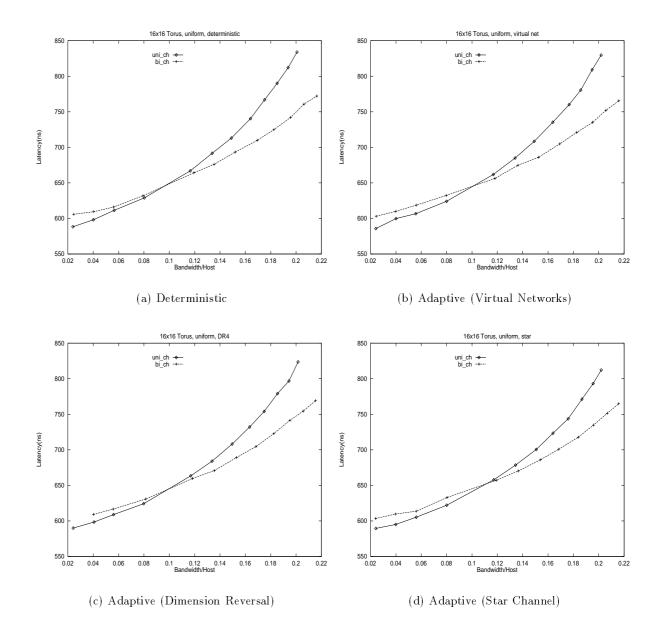

| 5.9  | Latency versus throughput for different routing algorithms under uniform ran-                |    |

|      | dom traffic. Comparison of uni- and bi-directional channels                                  | 79 |

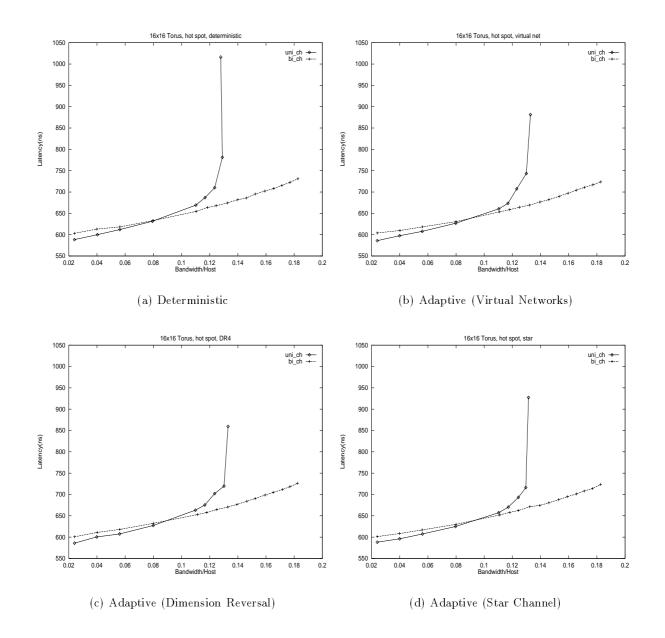

| 5.10 | Latency versus throughput for different routing algorithms under Hot-spot                    |    |

|      | traffic. Comparison of uni- and bi-directional channels                                      | 80 |

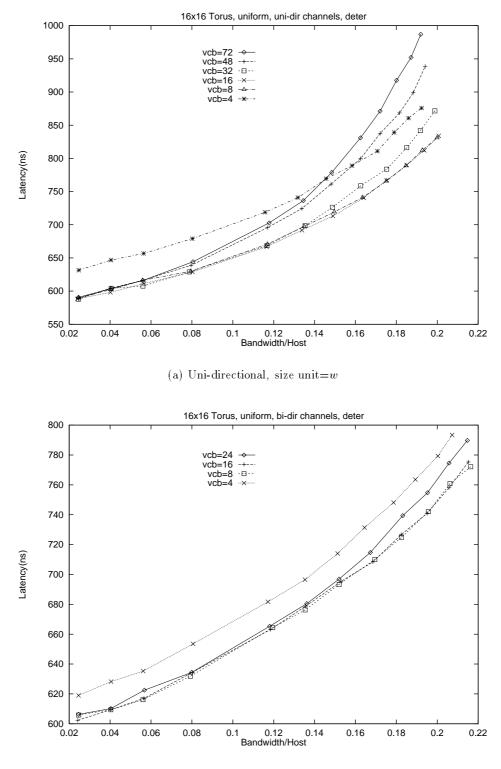

| 5.11 | Latency versus throughput for different virtual channel buffer sizes. Determ-                |    |

|      | inistic routing under uniform random traffic                                                 | 81 |

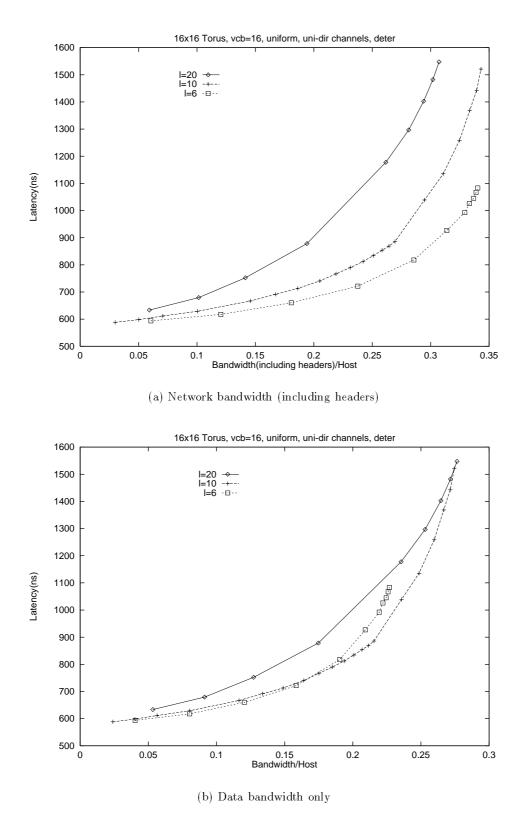

| 5.12 | Latency for different packet length. Uni-directional channels. Deterministic routing under uniform random traffic    | 82  |

|------|----------------------------------------------------------------------------------------------------------------------|-----|

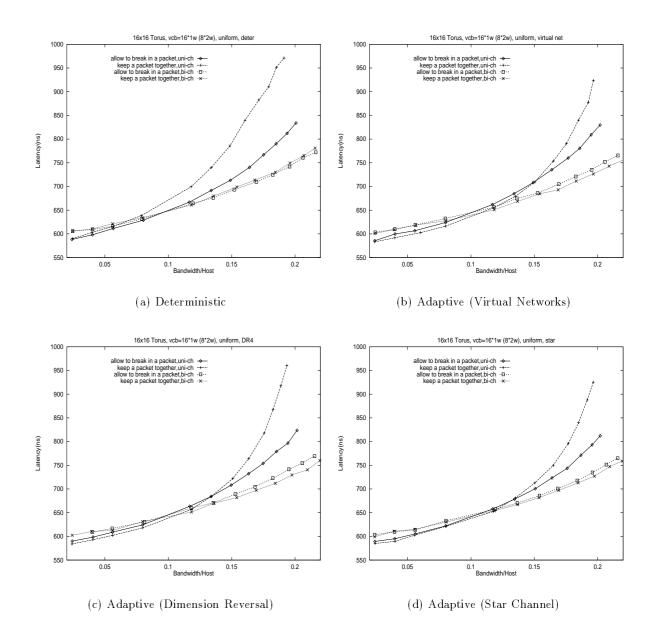

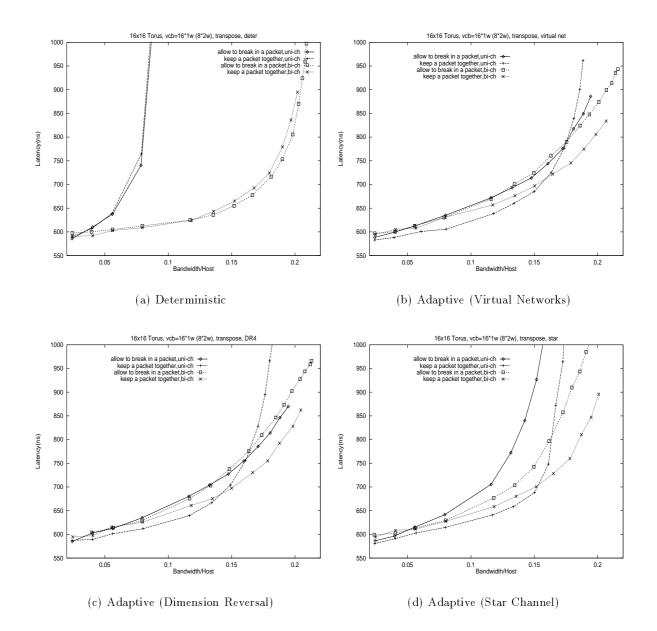

| 5.13 | Latency versus throughput for different routing algorithms under uniform ran-<br>dom traffic.                        | 83  |

| 5.14 | Latency versus throughput for different routing algorithms under transpose traffic.                                  | 84  |

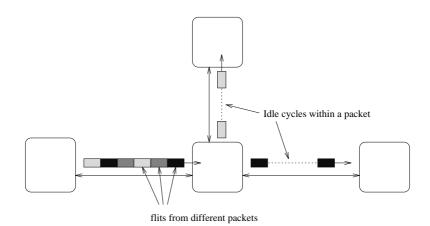

| 5.15 | Interleaving flits from different packets will insert idle cycles in the packets when they continue to the next node | 85  |

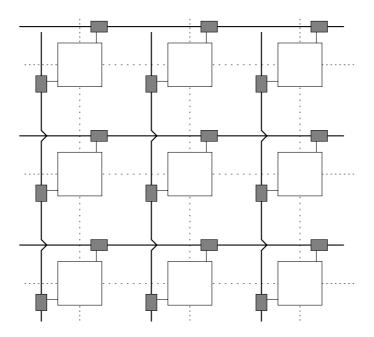

| 6.1  | Torus structure with links and reconfigurable buses                                                                  | 88  |

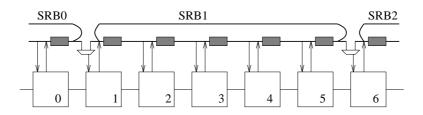

| 6.2  | Adjacent segments share a common end points                                                                          | 89  |

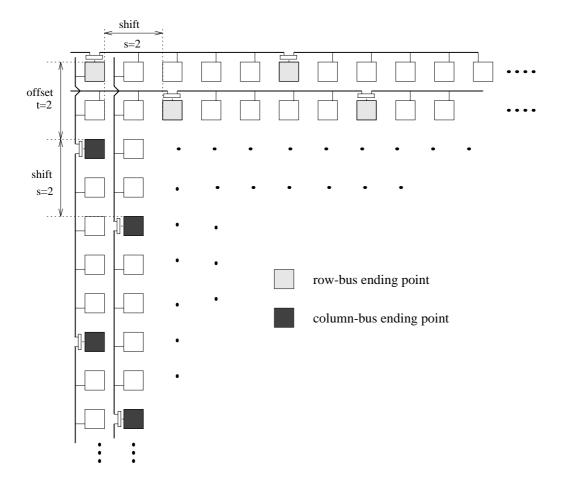

| 6.3  | Torus with segmented reconfigurable bus, segment length= $5$ , shift= $2$ , offset= $2$ .                            | 90  |

| 6.4  | Torus with global bus                                                                                                | 91  |

| 6.5  | A node of the torus with reconfigurable bus                                                                          | 93  |

| 6.6  | Wrap-around connections in a torus with SRB $\ldots$                                                                 | 94  |

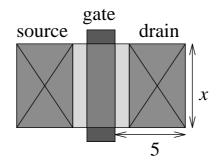

| 6.7  | Transistor layout model                                                                                              | 95  |

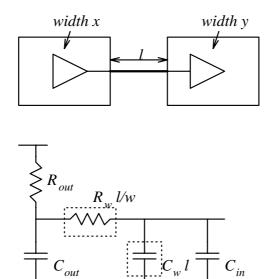

| 6.8  | Link model, where the wire is modeled by distributed $RC$                                                            | 96  |

| 6.9  | Bus model, where the parameters are the same as link model $\ldots$                                                  | 97  |

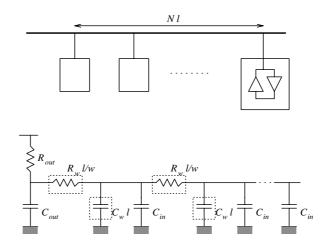

| 6.10 | (a) Transmission gate model, (b) Transmission gate interconnection, (c) Trans-                                       |     |

|      | mission gate interconnection model                                                                                   | 98  |

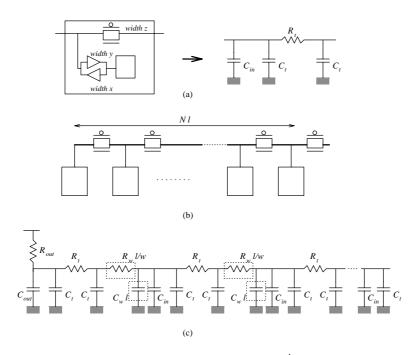

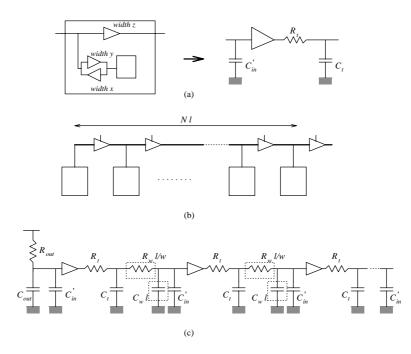

| 6.11 | (a) repeater model, (b) repeater interconnection, (c) repeater interconnection                                       |     |

|      | model                                                                                                                | 99  |

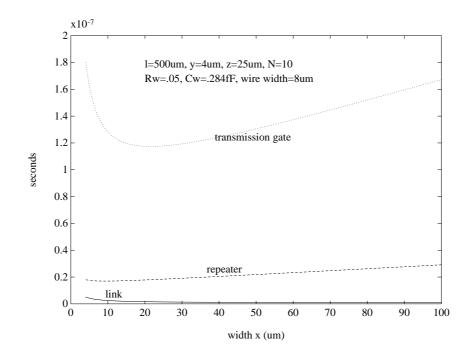

| 6.12 | Delay versus transistor width $x$ for a fixed width $z$                                                              | 101 |

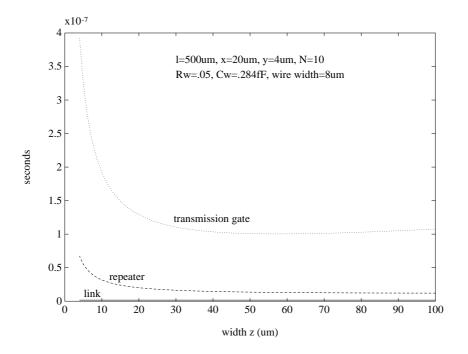

| 6.13 | Delay versus transistor width $z$ for a fixed width $x$                                                              | 102 |

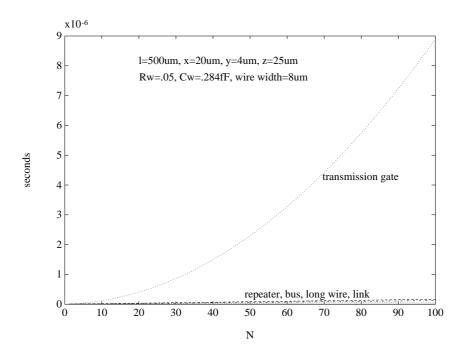

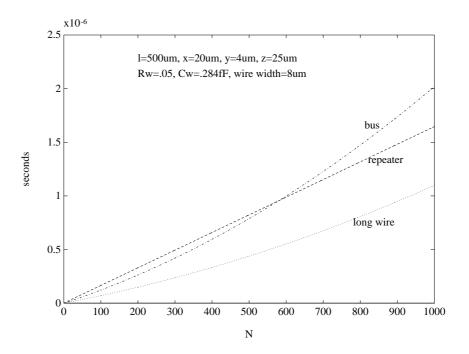

| 6.14 | Delay versus $N$                                                                                                     | 102 |

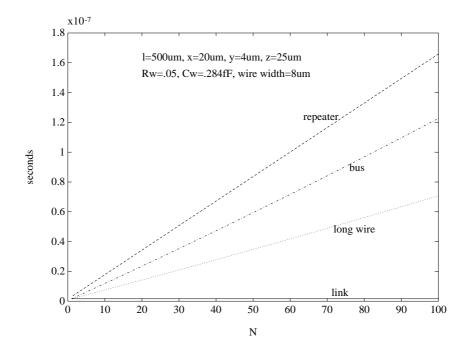

| 6.15 | Delay versus $N$ , excluding transmission gate $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                    | 103 |

| 6.16 | Delay versus large $N$                                                                                               | 103 |

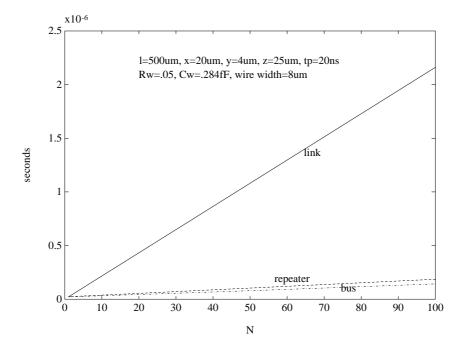

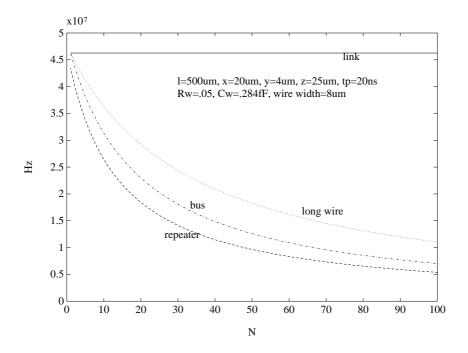

| 6.17 | Latency versus $N$                                                                                                   | 104 |

| 6.18 | Throughput versus $N$                                                                                                | 104 |

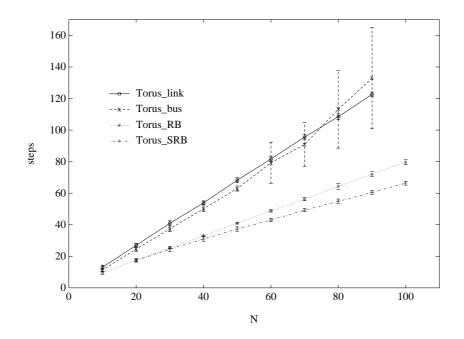

| 6.19 | Average steps versus $N$                                                                                             | 106 |

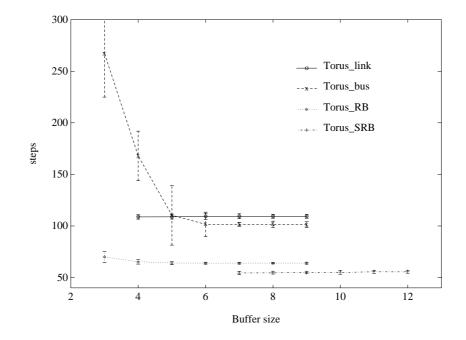

| 6.20 | Average steps versus buffer size, $N = 80$ , segment length=10 for Torus_SRB                                         | 107 |

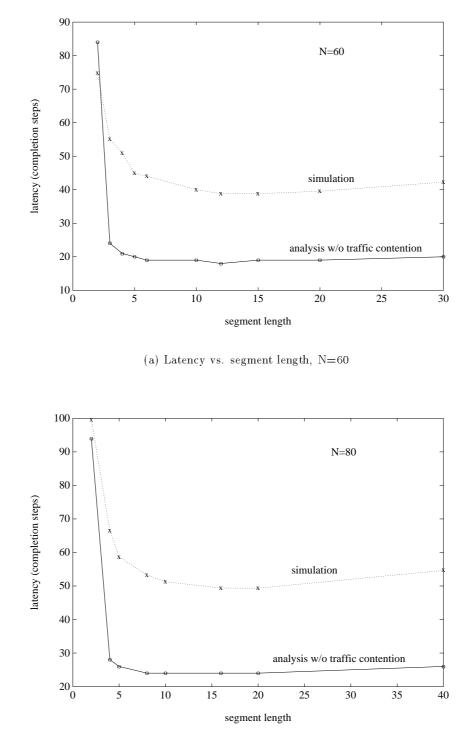

| 6.21 | Analysis and simulation of segment length                                                                            | 111 |

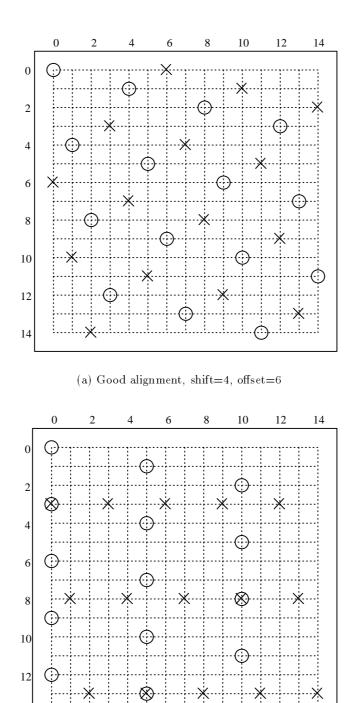

| 6.22 | Examples of segment alignment, $L = 15$ , (a) shift=4, offset=6, (b) shift=5,                                                                              |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | offset=3                                                                                                                                                   | 16 |

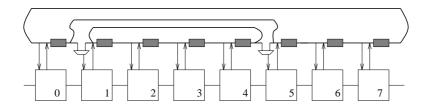

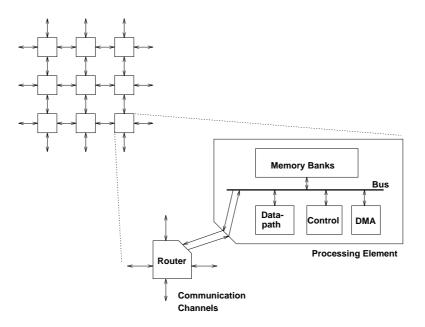

| 7.1  | Network architecture of STARP                                                                                                                              | 22 |

| 7.2  | Channel format                                                                                                                                             | 23 |

| 7.3  | Packet format                                                                                                                                              | 24 |

| 7.4  | Flit format                                                                                                                                                | 25 |

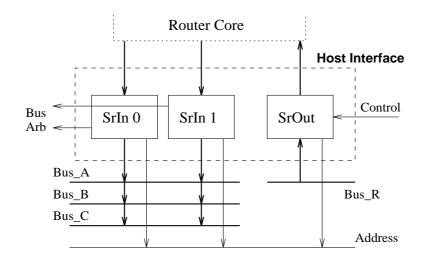

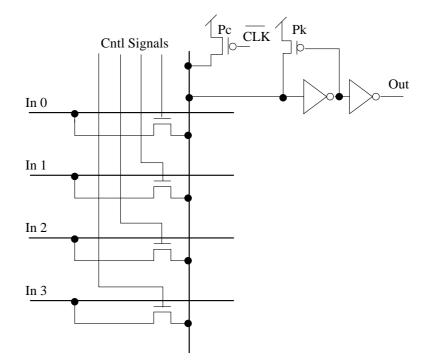

| 7.5  | Global router architecture                                                                                                                                 | 27 |

| 7.6  | Host interface architecture                                                                                                                                | 28 |

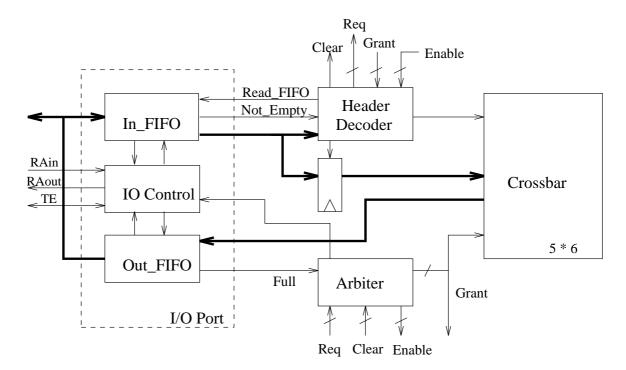

| 7.7  | Router port architecture, only one port is shown                                                                                                           | 29 |

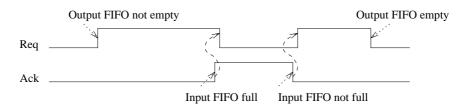

| 7.8  | Channel hand-shaking in the packet level                                                                                                                   | 30 |

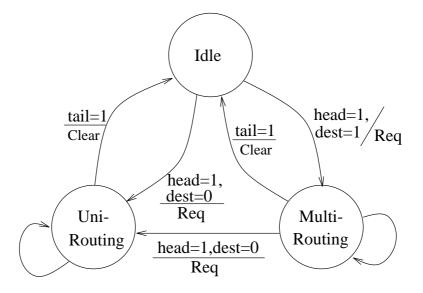

| 7.9  | State diagram of the header decoder                                                                                                                        | 31 |

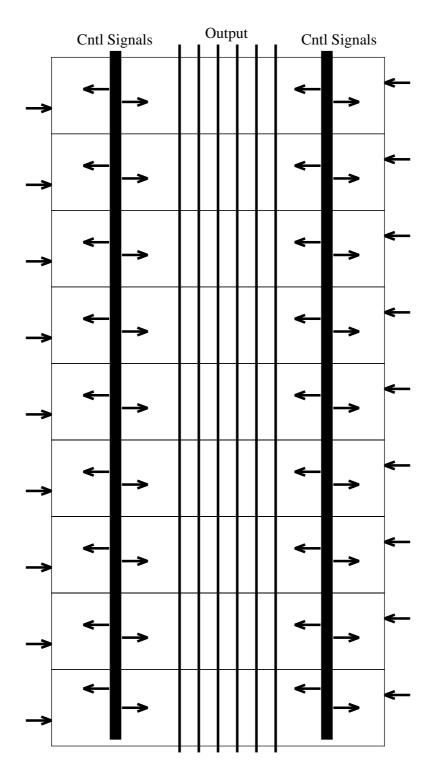

| 7.10 | Two different crossbar architectures                                                                                                                       | 33 |

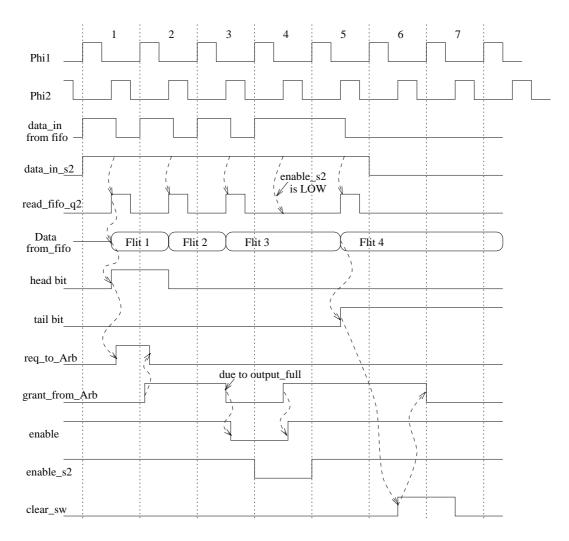

| 7.11 | I/O control and channel timing diagram 13                                                                                                                  | 35 |

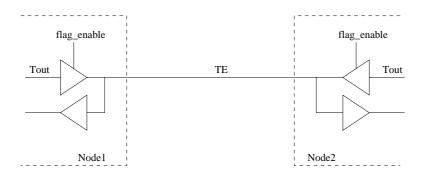

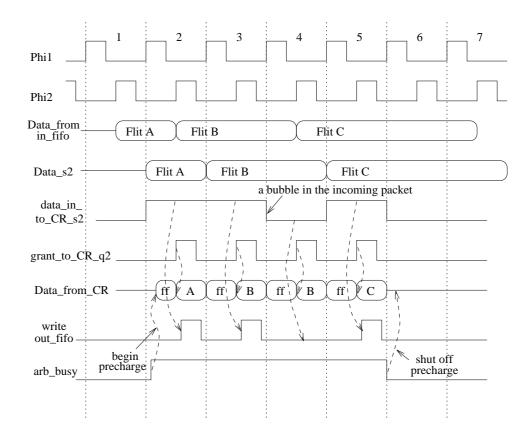

| 7.12 | Token-exchange interface circuit diagram                                                                                                                   | 36 |

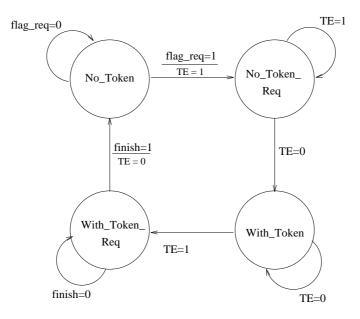

| 7.13 | Token-exchange state diagram                                                                                                                               | 36 |

| 7.14 | Token-exchange timing diagram                                                                                                                              | 37 |

| 7.15 | Header decoder timing diagram                                                                                                                              | 39 |

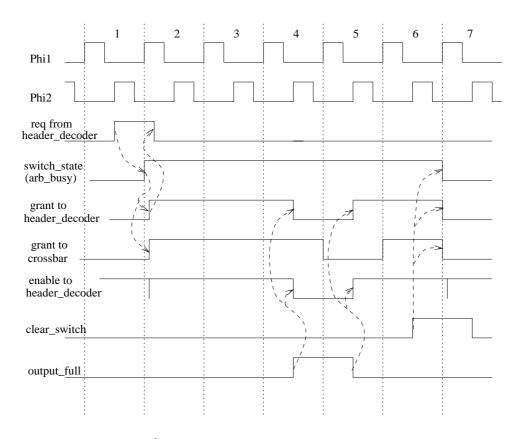

| 7.16 | Arbiter timing diagram                                                                                                                                     | 40 |

| 7.17 | Crossbar timing diagram                                                                                                                                    | 41 |

| 7.18 | Router core timing diagram 14                                                                                                                              | 42 |

| 7.19 | Design methodology and flow of STARP 14                                                                                                                    | 48 |

| 7.20 | CMOS inverter model                                                                                                                                        | 49 |

| 7.21 | Crossbar switch circuits                                                                                                                                   | 50 |

| 7.22 | Dynamic crossbar switch with a PMOS keeper at the output to prevent leakage1                                                                               | 51 |

| 7.23 | Crossbar switch floor plan                                                                                                                                 | 52 |

| 7.24 | STARP chip micrograph                                                                                                                                      | 54 |

| 7.25 | Loop-back mode test                                                                                                                                        | 55 |

| 7.26 | Chip measurement results 18                                                                                                                                | 57 |

| 7.27 | Core energy×delay vs. Vdd $\ldots \ldots $ | 58 |

| 7.28 | Performance improvement vs. well bias                                                                                                                      | 58 |

# Chapter 1

# Introduction

The demand for more powerful computation is increasing rapidly in many different fields. For example, high-definition television (HDTV) with  $2K \times 1K$  pixels per frame and a frame rate of 60 frames per second will require at least 100 GOPS ( $1 \times 10^{11}$  operations/sec) for video compression. With higher quality and larger image size, the computation requirement falls easily in the Tera OPS ( $1 \times 10^{12}$  operations/sec) range. Facing this exploding demand, we will ask where the computation power comes from.

Different advanced techniques and computing models have been proposed and implemented to improve computational capability (Hennessy and Patterson, 1996). These computing models have different approaches and efficiency, but they all achieve their goals by increasing the concurrency of the system to some degree.

#### Pipelining

A serial computation can be divided into a number of steps, called stages. Each stage works at full speed on a particular part of computation. The output of one stage is the input of the next stage. With proper balance of the delay of each stage, data are fed continuously into the pipelined stages and all stages can operate concurrently with different sets of input to maximize the computation throughput.

#### Superscalar

When a pipeline reaches its maximum capacity, more functional units must be added in parallel to increase performance. Machines that can issue multiple independent instructions per cycle are superscalar machines. Different instructions can use different functional blocks and execute in separate pipelines concurrently if there is no hardware conflict. Therefore, a superscalar machine increases the parallelism in a processor to achieve more computation in a shorter time.

#### Massively Parallel Processing (MPP)

After we consume the computation power of a single processor, the next step is to combine more processors to solve problems together. Massively parallel processing represents the ultimate approach to achieving the limits of computation.

Parallel processing provides significant computational advantages for many scientific, signal processing, and image processing applications. However, it took more than 20 years for parallel computers to move from laboratory to marketplace. Even with today's most advanced technology, many challenges remain. Computation is not the only concern, however, as other issues are becoming bottlenecks. For example, as a parallel system grows, interprocessor communication may eventually dominate overall system performance. Having noticed the increasing importance of inter-processor communication, realizing its potential to limit the improvement of a parallel system, we take the question of optimal multiprocessor communication as the central problem of this dissertation.

## 1.1 Multiprocessor Speedup

When we have a multiprocessor system, a natural question to ask is how much performance gain we can get from the system. Speedup performance models were defined to answer this question quantitatively.

#### 1.1.1 Speedup with a fixed load

The most common speedup model is that of the "fixed-load", which has a fixed problem size and workload. As the number of processors increases, the fixed load is distributed to all the processors in the system. Let T(1) be the time required to finish the problem in one processor, and T(n) be the time for n processors. Then the speedup factor for the fixed load is defined as

$$S_n = \frac{T(1)}{T(n)} \tag{1.1}$$

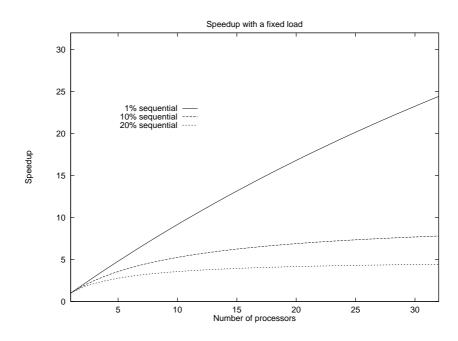

Figure 1.1: Amdahl's Law. Speedup with a fixed load

Amdahl's law is used to find the speedup factor for a fixed load. Usually the total workload W is assumed to consist of two parts:  $W_s$  is the sequential portion of the program which cannot be parallelized, and  $W_p$  is the portion which can be parallelized and evenly distributed in all available processors. The speedup factor  $S_n$  can be written as

$$S_{n} = \frac{W}{W_{s} + W_{p}/n} = \frac{W_{s} + W_{p}}{W_{s} + W_{p}/n}$$

(1.2)

When  $n \to \infty$ ,  $S_n \to W/W_s$ . So the speedup is bounded by  $W/W_s$  and cannot go further even we have more processors. Fig. 1.1 shows the speedup versus the number of processors for a fixed load. When we have 10% of a program which cannot be parallelized, the speedup curve is very flat after we have more than about 20 processors. So the sequential part becomes the performance bottleneck.

#### 1.1.2 Speedup with fixed execution time

The problem with Amdahl's law is that the workload cannot scale with the number of processors to fully utilize the available computing power, and we get a very low speedup factor. Gustafason (1988) proposed a fixed-time speedup model to scale the problem size.

Assuming the total work  $W(1) = W_s + W_p$  for one processor can be done in time T, for n

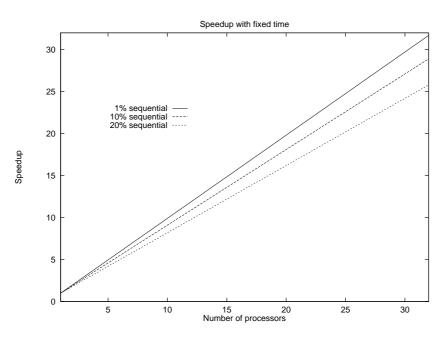

Figure 1.2: Gustafson's Law. Speedup with fixed time

processors, we can finish the total workload  $W(n) = W_s + nW_p$  in the same amount of time. Therefore, the speedup  $S_n$  can be defined as

$$S_n = \frac{W(n)}{W(1)}$$

$$= \frac{W_s + nW_p}{W_s + W_p}$$

(1.3)

Fig. 1.2 shows the speedup for the fixed-time model. With fixed-time characteristics, a very good speedup factor is achieved even when the sequential portion is as high as 20%. Because we have scaled the problem size, we can utilize more computing power by keeping all processors busy.

Gustafson's law gives us insight to design our own parallel machine for image/video processing (Chapter 7). When we have a fixed image size, the benefit of increasing the network size to solve the problem is small when we have a "sufficient" network size.<sup>1</sup> But if we are dealing with a larger image size, we should scale our network size to match the workload, and thereby maintain a very high speedup factor.

$<sup>^1</sup>$  "Sufficient" means that the time a processor spends in the parallel portion is about the same as the time in the sequential part.

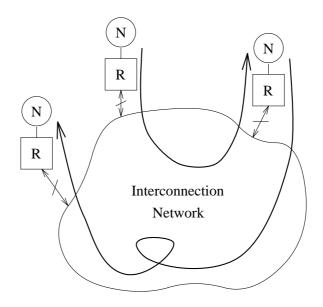

Figure 1.3: Multiprocessor networks. Communication occurs between nodes (processors and/or memory). N is the node and R is the data router.

### 1.2 Multiprocessor Networks

A multiprocessor network is used to connect all processing elements, memory modules, and periphery devices, and to make them work together. Fig. 1.3 illustrates a general multiprocessor network. The interconnection network is the backbone of a parallel system. All nodes collaborate with each other through the interconnection network. Chapter 2 will give an overview of interconnection networks and different network examples.

### **1.3** Multiprocessor Communications

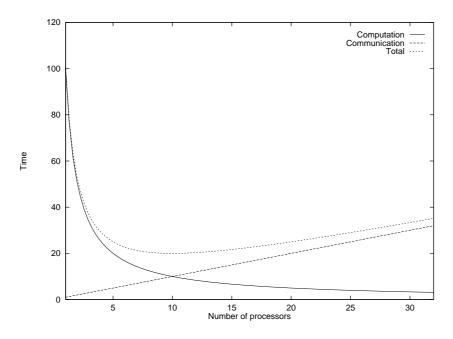

Fig. 1.4 shows the total execution time of a parallel machine in terms of its two components: computation and communication. We assume that the computation can be parallelized completely, and that the computation time is inversely proportional to the number of processors. Communication time, however, is linear with the number of processors. As the number of processors increases, the computation time decreases dramatically. However, the communication time increases steadily and becomes dominant finally. Therefore, the communication overhead plays an important role in the overall system performance.

In fact, when traffic contention in a network occurs, the communication time will increase more than linearly with the number of processors. Fig. 1.5 illustrates a simple example of

Figure 1.4: Total execution time is composed of computation time and communication time

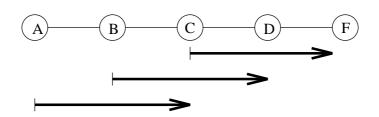

traffic contention. Assume nodes A, B, C have data sent to nodes C, D, E, respectively. The channel setup time is t for each hop and data transmission will occupy the channel for nt where n is the packet length. The intermediate nodes can begin to forward the data to the next nodes immediately after they receive the data.<sup>2</sup> Without any traffic contention, the data routing can be finished at time nt (assume  $n \gg 1$  to ignore the channel setup time). But data moving from node A to C and data moving from B to D will compete for the link BC. Similar contention occurs on link CD. So if nodes A, B, C start to send their data at the same time, the data routing cannot be completed until time  $\sim 3nt$ . However, if we can delay node B to send its data till time  $\sim nt$ , then there is no contention between path A  $\rightarrow$  C and C  $\rightarrow$  E, and the data routing will be finished at time  $\sim 2nt$ . This simple example shows how the routing latency can be varied due to different degrees of traffic contention.

$<sup>^2\</sup>mathrm{We}$  assume the wormhole routing flow control. The detail of flow control schemes will be given in Chapter 3.

Figure 1.5: An example of traffic contention. Node A to node C, B to D, and C to E. There is traffic contention on link BC and CD.

### 1.4 An Overview of the Research

In the rest of this dissertation, we will discuss in detail the inter-processor communication issues in parallel systems for which the design goals for an efficient inter-processor communication architecture are high data throughput, low routing latency, low communication energy, and low implementation cost. Chapter 2 gives an overview of network properties and examples of different network topologies. Chapter 3 introduces flow control schemes, virtual channels, and channel configurations. Chapter 4 describes wormhole routing algorithms including deterministic, fully adaptive, partially adaptive, and multicasting algorithms. Simulation results of different routing algorithms and channel configurations are given in Chapter 5. An enhanced mesh or torus architecture with segmented reconfigurable bus (SRB) is introduced in Chapter 6, where also gives an optimization procedure for a torus with SRB. Chapter 7 describes the detail design and implementation of a VLSI wormhole data router for a 2-D mesh or torus. It implements bi-directional channels, dimension-order data routing, and hardware supported path-based multicasting. A completed chip implementation delivers 1.6Gb/s (50MHz) @ Vdd=2.1V and consumes an average power of 15mW. Finally, Chapter 8 summarizes the contributions of this dissertation and suggests some future work in this field.

CHAPTER 1. INTRODUCTION

## Chapter 2

# **Network Interconnection**

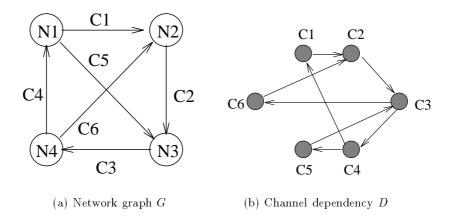

A multiprocessor network comprises nodes and communication channels, and can be represented by a uni-directional graph G = (N, C), with vertices  $N = \{n_1, n_2, \ldots, n_m\}$  corresponding to the nodes and edges  $C = \{c_1, c_2, \ldots, c_n\}$  corresponding to the communication links between nodes. An efficient network for multiprocessors should be able to utilize the hardware resources effectively. Network performance usually is measured by latency and throughput: latency is the time required for a message to be delivered from source to destination; throughput is the data rate which is maintained in the network. Both latency and throughput are strongly dependent on the network topology and the routing algorithm employed. In this chapter, we will describe some properties of a network and introduce different network topologies.

### 2.1 Properties of Network Topology

There are several network properties that are directly related to network performance and complexity (Hwang, 1993). We will describe these network properties in this section and compare these properties for different networks in the next section.

#### **Network Diameter**

The network diameter is the maximum shortest path between any two nodes in the network. The diameter is the indication of the worst case latency when the traffic load is low. A designer should keep the network diameter small to reduce latency.

### **Bisection Width**

The network bisection width is the minimum number of channels required to be removed to cut the network into two equal-sized parts. Therefore, the bisection width is related to the maximum communication bandwidth supported between two separated parts in the network.

#### Number of Links

The total number of links is related to the maximum total bandwidth provided in a network. In an ideal case, all the links can be used for transmitting data at the same time; this would achieve the peak throughput of the network. So the number of links is an indication of degree of concurrency of communications. The number of links also affects the cost of the network interconnection.

#### Node Degree

The node degree is the number of IO ports associated with each node in the network. When we design a scalable network, we would like to have the node degree independent of the network size to reduce the cost. Limited wire density and pin count in the current VLSI packaging technology restrict the node degree in feasible networks.

#### Symmetry

A network is symmetric if it is isomorphic to itself with any node used as the origin. Thus, in a symmetric network, the network is the same seen from any node. For uniform traffic, a symmetric network has the same traffic loading in all channels, and "hot-spot" effects, which may occur in an asymmetric network, are reduced.

#### **Network Mapping**

No matter what form of network we design, we need to map the network onto a twoor three-dimensional space for implementation. This network mapping directly affects the physical channel width and wire length. Thus propagation delay, clock speed, and transmission power all depend on the network mapping.

#### **Data Routing**

Data routing is the basic function performed by a network. Different network topologies have different characteristics as described above, as well as different node addressing,

#### 2.2. NETWORK EXAMPLES

(a) Linear Array

(b) Ring

Figure 2.1: Linear Array and Ring

communication paths, and channel dependency. Therefore, different data routing algorithms are needed to match the different topologies.

#### Scalability

Ideally, the network performance should be scaled linearly with an increasing number of processors employed. For example, the network bisection width should be scaled with the network size to support sufficient communication bandwidth for the increased traffic. For a scalable network, the node degree should be constant, the network mapping should be compact, and the data routing should be identical for different size of networks.

### 2.2 Network Examples

In this section, we will give a brief description of some popular networks and compare their characteristics as defined in the previous section.

#### Linear Array and Ring

Fig. 2.1 shows the topology of a linear array and ring. Linear arrays and rings are very simple and low-cost, but long diameter and low bisection width causes the latency to increase exponentially as the number of nodes increases, due to traffic contention.

#### Tree

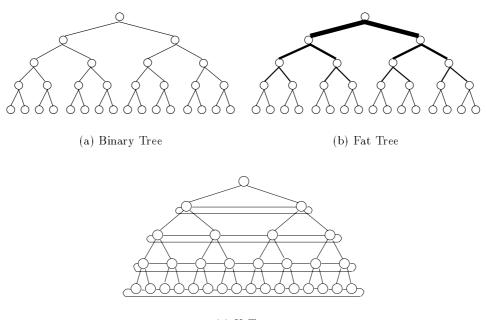

A binary tree is shown in Fig. 2.2(a). A tree is made up a root, intermediate nodes, and leaves. Long relative distances between leaves on different branches and low bisection width are the main drawbacks of a tree network. Fat trees (Fig. 2.2(b)) have been proposed to increase the bandwidth as we ascend from leaves to the root and then reduce traffic contention near the root. Another variation of the tree structure is the

(c) X-Tree

Figure 2.2: Tree Networks

"X-tree" (Fig. 2.2(c)). In an X-tree network, all the nodes at the same level are also connected in a ring to reduce the communication across levels and the bottleneck near the tree root. The tree structures are not only limited to binary connections. The structures can be extended to multiway trees.

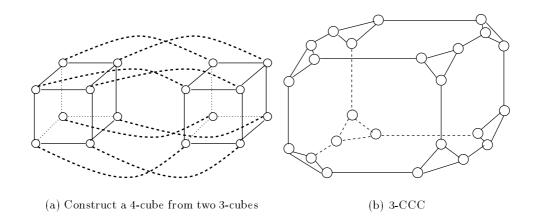

#### Hypercube and Cube-Connected Cycle (CCC)

In general, a hypercube is an *n*-cube with  $N = 2^n$  nodes. There are *n* dimensions with two nodes per dimension. An order *n* hypercube can be constructed from two order n - 1 hypercubes, but the node degree increases from n - 1 to *n* (Fig. 2.3(a)). That the node degree depends on the network size makes hypercubes unscalable. A cube-connected cycle (CCC) is a variation of hypercubes. An *n*-dimensional CCC is a *n*-cube in which each vertex is replaced by a cycle of *n* nodes. Therefore, an *n*-CCC has  $N = n2^n$  nodes, and a longer network diameter, but a constant node degree of 3. Fig. 2.3(b) shows a 3-cube topology.

Figure 2.3: Hypercube and CCC

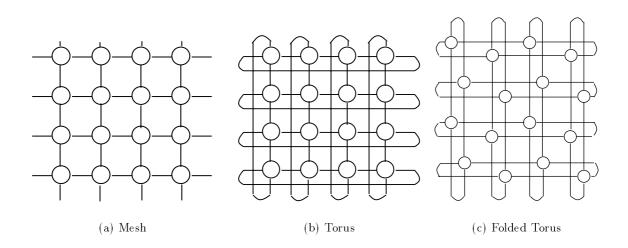

#### 2-D Mesh and Torus

Fig. 2.4 shows the topology of a 2-D mesh and torus. A torus is basically a mesh with wrap-around connections in each row and column to reduce the network diameter. A folded torus, shown in Fig. 2.4(c), can be laidout easily without the long wrap-around connections which increase the propagation delay. 2-D meshes and tori are becoming popular due to their simplicity, regularity, scalability, and feasibility.

#### k-ary n-cube

This is a very general network topology with n dimensions and k nodes per dimension. Linear arrays, rings, hypercubes, meshes, and tori all belong to this family. Several researchers have produced results in favor of low-dimensional networks. Under the assumption of constant wire bisection width, Dally (1990b) has shown that two-dimensional k-ary n-cube networks can offer the minimum latency with a linear wire delay model. Agarwal (1991) also showed that three or four-dimensional networks perform best under some other constraints, e.g., fixed node size, considerable switching delay, and so on. Several new generation multiprocessors have chosen the k-ary n-cubes family as their interconnection.

Figure 2.4: 2-D Mesh and Torus

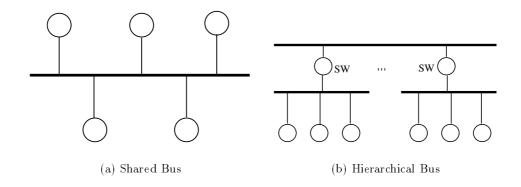

#### Shared Bus

A shared bus is a very simple way to connect several hosts together (Fig. 2.5(a)). A bus is usually heavily loaded, has long propagation delay, and consumes more energy than other types of interconnections. Bus arbitration needs to be considered because only one node at a time can use the bus. The bus bandwidth is shared among multiple nodes and the traffic contention may become serious when the number of nodes increases. A hierarchical bus structure has been proposed to increase utilization and bandwidth, and to reduce contention (Fig. 2.5(b))(Mahnud, 1994).

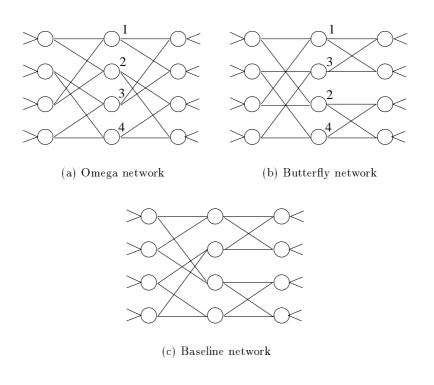

#### Multi-stage Network

A multi-stage interconnect network (MIN) consists of more than one stage of switch elements which can be set up dynamically according to traffic requests. Processing nodes (or memory) are located at the ends of the MIN, and traffic is routed from one end to the other. Different switch "fabrics" and interstage connections have been proposed (Tobagi, 1990; Fen, 1981). Some examples are the *Omega* (or *Shuffle-Exchange*), *Butterfly*, and *Baseline* networks, etc., pictured in Fig. 2.6. We should note that some multi-stage networks are actually equivalent, for instance, Fig. 2.6 (a) is equivalent to (b) with some nodes in the middle stage re-ordered. All the paths in a MIN have the

Figure 2.5: Bus Networks

same latency, so the designer cannot take advantage of data locality in most applications.

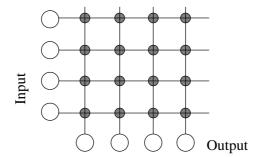

#### Crossbar

A crossbar switch is an interconnection in which each input is connected to each output through a path that contains a single switching node (Fig. 2.7). It offers the least traffic contention, but has the highest complexity. The cost is proportional to  $N^2$  where N is the network size. Because of the high cost, the crossbar network is not very scalable in a large system.

Table 2.1 provides a summary of network characteristics, showing the relation between key physical properties and network size for different network topologies. Table 2.2 surveys the topologies used in some parallel systems. Most of the recent multiprocessor systems have chosen the low dimensional k-ary n-cube as the network interconnection because of its scalability for high bandwidth, regularity for easier data routing, and simplicity for efficient implementation.

## 2.3 Network Category

Networks also can be categorized based on interconnection status or node functionality. A network interconnection can be either *static* or *dynamic*. Static networks such as meshes and k-ary *n*-cubes have all their connections fixed without changing during execution. On the

Figure 2.6: Some multi-stage networks examples

Figure 2.7: Crossbar Network

| Network      | size          | diameter                           | bisection  | number       | node   | symmetry |

|--------------|---------------|------------------------------------|------------|--------------|--------|----------|

|              |               |                                    | width      | of links     | degree |          |

| Linear Array | N             | N - 1                              | 1          | N-1          | 2      | No       |

| Ring         | N             | $\lfloor N/2 \rfloor$              | 1          | N            | 2      | Yes      |

| Binary Tree  | $N = 2^n - 1$ | 2(n-1)                             | 1          | N-1          | 3      | No       |

| Hypercube    | $N = 2^n$     | n                                  | $2^{n-1}$  | nN/2         | n      | Yes      |

| CCC          | $N = n2^n$    | $2n - 1 + \lfloor n/2 \rfloor$     | $2^{n-1}$  | 3N/2         | 3      | Yes      |

| 2-D Mesh     | $N = k^2$     | 2(k-1)                             | k          | 2(N-k)       | 4      | No       |

| 2-D Torus    | $N = k^2$     | $2\lfloor k/2 \rfloor$             | 2k         | 2N           | 4      | Yes      |

| k-ary n-cube | $N = k^n$     | $n \left\lfloor k/2 \right\rfloor$ | $2k^{n-1}$ | nN           | 2n     | Yes      |

| Shared Bus   | N             | 1                                  | 1          | 1            | 1      | Yes      |

| Omega        | N             | $\lg N + 1$                        | N/2        | $N(\lg N+1)$ | 4      | No       |

| Crossbar     | N             | 2                                  | N          | N            | 2      | Yes      |

Table 2.1: Summary of network properties

other hand, dynamic networks may change their channel configuration during the running time depending on data routing requirement, for example, multi-stage networks.

A network configuration also can be either *direct* or *indirect*. In a direct network, all the nodes are the processing units as well as switching elements, *i.e.*, the communication channels connect processors directly. Unlike direct networks, indirect networks have some intermediate nodes used for switching only. In this case, messages between processing nodes are routed through the paths set up by switching nodes. A dynamic network is usually an indirect network; for example, a multi-stage network often has its processors or memory at both ends of the network, and has the intermediate stages as switches. A dynamic network also can be a direct network; for example, a reconfigurable mesh may change its connections to the neighbors even though all the nodes are the processing units. Similarly, a static network can be either a direct or indirect network; for instance, a tree network is a direct network if all the nodes are processors, but is an indirect network if only the leaves of the tree are processors.

| Machine             | Year | Topology                | Remarks                                                                                                                                                                               |

|---------------------|------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMU/C.mmp           | 1972 | Crossbar                | 16 processors $\times$ 16 memory                                                                                                                                                      |

| Caltech/Cosmic Cube | 1983 | Hypercube               | 64 nodes connected in a binary 6-cube                                                                                                                                                 |

| Intel/iPSC          | 1985 | Hypercube               | 7 I/O ports form a 7-dim hypercube                                                                                                                                                    |

| IBM/RP3             | 1985 | Omega                   | 512 processors. The interconnect consists of<br>2 networks. A network with 128 ports (4 levels<br>of $4 \times 4$ ). A combining network with 64 ports<br>(6 levels of $2 \times 2$ ) |

| TMC/CM-2            | 1987 | Hypercube               | CM-2 is made of 8 subcubes. Each subcube<br>contains 16 matrix boards. A matrix board<br>has 512 processors                                                                           |

| Cray/Y-MP           | 1988 | Multi-stage<br>Crossbar | 8 processors and 256 memory modules<br>connected by $4 \times 4$ and $8 \times 8$ switches and<br>$1 \times 8$ demux                                                                  |

| BBN/Butterfly       | 1989 | Butterfly               | A 3-stage $512 \times 512$ butterfly network<br>constructed by $8 \times 8$ switches for a<br>512 processors system                                                                   |

| TMC/CM-5            | 1991 | Fat tree                | 32 to 1024 processors (max. 16384 proc)<br>bisection width of 1024 nodes is 5GB/s                                                                                                     |

| KSR-1               | 1991 | Fat tree                | 2 levels of ALLCACHE Engine hierarchy.<br>The ALLCACHE Engine is the fat tree<br>topology. Eng:0 has bandwidth 1GB/s,<br>Eng:1 has 1, 2, or 4GB/s                                     |

| Intel/Paragon       | 1991 | 2-D Mesh                | Link bandwidth: 175MB/s full duplex<br>max bisection width: 5.6GB/s                                                                                                                   |

| Stanford/DASH       | 1992 | 2-D Mesh                | 16 clusters $(4 \times 4 \text{ mesh})$<br>Each cluster has 4 PEs<br>May extend to 512 clusters                                                                                       |

| MIT/J-Machine       | 1992 | 3-D Mesh                | 1024-node $(8 \times 8 \times 16)$<br>max limit: 65536 nodes $(32 \times 32 \times 64)$                                                                                               |

| Caltech/Mosaic C    | 1992 | 2-D Mesh                | 64 Mosaic chips are packaged in an $8 \times 8$<br>array on the circuit board. These boards<br>can construct arbitrarily large 2-D arrays                                             |

| Cray/T3D            | 1993 | 3-D Torus               | 2048 processors with peak 300 Gflops                                                                                                                                                  |

Table 2.2: Topologies of existing parallel systems

# Chapter 3

# **Routing Flow Control**

Data routing is one of the most important factors in a high performance multiprocessor network. In many situations, communication between processors has become the performance bottleneck. For example, in a shared memory system, processors may wait for the memory responses which need to travel across the network. Therefore, an efficient routing flow scheme and routing algorithm are crucial to achieving good overall system performance.

## **3.1** Desired Routing Properties

There are three basic types of data routing faults in any kind of network: *deadlock*, *livelock*, and *starvation*. In a network system, all messages compete with each other for limited resources. Unless the routing conflicts are resolved satisfactorily, one of these faults will occur. A desirable routing flow control will be deadlock-free, livelock-free, and starvation-free.

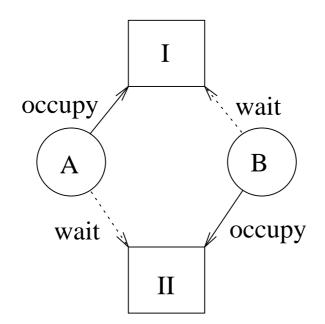

#### Deadlock

There are four necessary conditions for deadlock to occur: *mutual exclusion, no preemption, hold and wait,* and *circular wait* (Silberschatz *et al.*, 1991). For example, resource I is occupied by process A, and process A is requesting use of resource II which is occupied by process B. If process B is requesting resource I, and if a resource cannot be released by a process until the new request has been granted, then there is a circular request dependency between process A and B, and deadlock will arise (Fig. 3.1). In

Figure 3.1: An example of deadlock: A is waiting for B to release resource II, and B is waiting for A to release resource I.

data routing, the resources may be buffers (in a store-and-forward network) or channels (in a wormhole network) depending on the routing flow control scheme (Section 3.2). When the circular waiting condition occurs, no message can move forward, and deadlock results. Avoiding deadlock is critical to solution of the data routing problem. We will discuss deadlock avoidance methods in chapter 4.

#### Livelock

"Livelock" occurs when a packet circulates in a network forever and never arrives at its destination. In the livelock situation, data packets which are circulating in the network consume channel bandwidth and increase traffic contention. If all packets take only the shortest paths to their destinations, *i.e.*, every hop decreases the distance to the destination, then livelock cannot occur because all packets take finite steps to reach the destinations. Livelock can occur in non-minimal routing algorithms where packets detour away from their destinations when they encounter traffic contention.

#### Starvation

A packet may wait for a resource indefinitely when it is competing with other packets. Starvation is caused by an unbalanced arbitration of resources. For example, a low priority packet might not gain access to a channel which is always requested by other higher priority packets. One solution to the problem of starvation is *aging*. In order to prevent unlimited waiting, aging increases the priority of packets which have waited in the network for a certain time. Aging also increases the overhead of data routing in the form of the extra hardware required to calculate the age of a packet, and the additional data field required to store the age, etc.

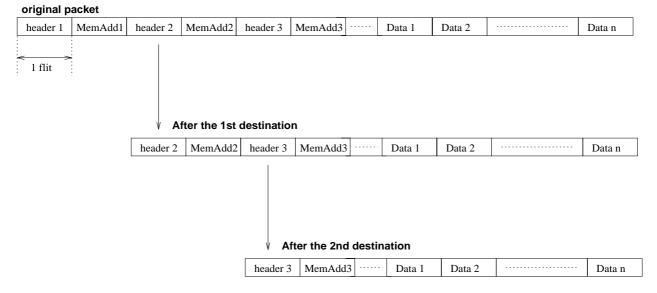

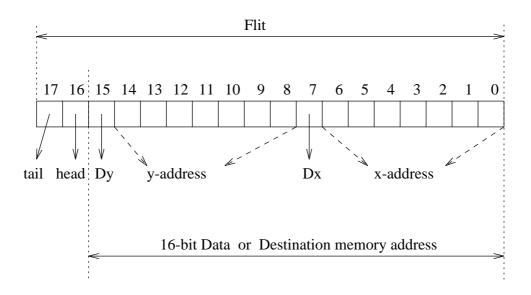

### 3.2 Routing Flow Control Schemes

Flow control is the scheme for allocating communication channels and buffers, and determining the steps to advance messages (Dally, 1990a). In a message-passing network, a message is divided into several *packets* for transmission in the network. Each packet contains its own header on routing information, and can be routed independently. A packet is divided further into several flow control digits or *flits*. A flit is the basic unit for transmission. Only the header flit contains the routing information. The rest of flits follow the header and cannot be routed independently.

Several routing control schemes have been proposed and implemented in parallel machines. In this section, we will describe and compare these different schemes.

#### Store-and-Forward Routing

Early multiprocessors used store-and-forward as the routing flow control. A packet was treated as an indivisible entity in a store-and-forward network. When a packet reached an intermediate node, the entire packet was buffered in the node. Then the packet was forwarded to the next node on the path to the destination only when the next node had sufficient buffers to hold the packet and the channel was free.

#### Wormhole Routing

In a wormhole network, only the header flit carries the route information. As the header advances along the path, all the remaining flits follow in pipeline fashion. The intermediate nodes can begin to forward the message as soon as the header has been decoded and the next node on the route has been selected. If the header is blocked, the trailing flits remain distributed in the intermediate nodes along the path.

#### Virtual Cut-Through Routing

Virtual cut-through routing is similar to wormhole routing in that the flits are pipelined in the network (Kermani and Kleinrock, 1979). But when the header is blocked in this instance, all the flits of the stalled packet are collected by the intermediate node where the blocking occurs.

#### **Pipelined Circuit Switching Routing**

Pipelined circuit switching (PCS) (Gaughan and Yalamanchili, 1995) is a variation of wormhole routing. In PCS, data flits do not immediately follow the header into the network. The header travels alone to find the path to its destination. When the header finally reaches the destination, an acknowledge flit returns to the source. Then data flits are then pipelined along the established path in the network.

The first difference among these routing flow control schemes is their latency (Ni and McKinley, 1993). Let  $L_p$  be the packet length,  $L_f$  be the flit length, B be the channel bandwidth, and D be the distance between the source and destination.

The latency for a *store-and-forward* network is

$$T_{SAF} = \frac{L_p}{B} \times (D+1) \tag{3.1}$$

The latency for a *wormhole* network is

$$T_{WH} = \frac{L_p}{B} + \frac{L_f}{B} \times D \tag{3.2}$$

The latency for a *pipelined circuit switching* network is

$$T_{PCS} = \frac{L_p - L_f}{B} + 3 \times \frac{L_f}{B} \times D \tag{3.3}$$

Fig. 3.2 provides a comparison of the latency for the different routing flow schemes.  $L_p$  is usually larger than  $L_f$ , therefore the latency of *store-and-forward* is larger than the latency of *wormhole* family. When  $L_p \gg L_f$ , the latency of wormhole routing becomes less sensitive to the distance D.

Secondly, the buffer requirement is different for these three schemes. *Store-and-forward* and *virtual cut-through routing* require buffering of the entire packet, so they need storage memory for at least an entire packet inside each node. In contrast, *wormhole* and *pipelined circuit switching routing* allow a packet to be distributed in the intermediate nodes when

(c) Pipelined Circuit Switching

Figure 3.2: Latency comparison of different flow control schemes

there is traffic contention, thus they require less buffering in each node since only part of a packet must be stored.

Thirdly, different routing flow control schemes have different deadlock avoidance characteristics. In store-and-forward and virtual cut-through routing, the critical resource is packet buffers, while in *wormhole* routing, the critical resource is communication channels. To avoid deadlock a designer must eliminate circular dependency among resources which are requested by packets. For example, in store-and-forward and virtual cut-through routing networks, messages can be forwarded from one buffer to the next according to a loop-free directed buffer graph which accommodates all the possible message routes (Merlin and Schweitzer, 1980). The buffers can be organized so that they are in an ascending order. When a packet resides in a given buffer, it can be stored only in a restricted set of buffers in the next node of the path such that no circular dependency in the directed buffer graph may occur. In wormhole networks, on the other hand, *channel dependency* is used for resource allocation. To prevent deadlock it is necessary to restrict the routing relation to make the channel dependency acyclic. Virtual channels have been proposed as one method to eliminate cyclic channel dependency (Dally, 1992). In PCS networks, some routing constraints imposed by wormhole routing are relaxed because only headers are traversing in the network during the setup phase of a packet route, and deadlock can be avoided as long as the header has acyclic dependency (Gaughan and Yalamanchili, 1995). The penalty is that PCS networks have longer latency than wormhole networks.

Wormhole routing flow control has been adopted by most of the new generation multiprocessors, for instance, the Intel Paragon, Stanford DASH, and so on. Therefore, we concentrate on wormhole routing in the remainder of discussion.

## 3.3 Virtual Channel

Virtual channels have been incorporated in multiprocessor networks as a means of preventing deadlock and also of improving performance. Several virtual channels share a physical channel. This is accomplished by time multiplexing the virtual channels on the same physical link.

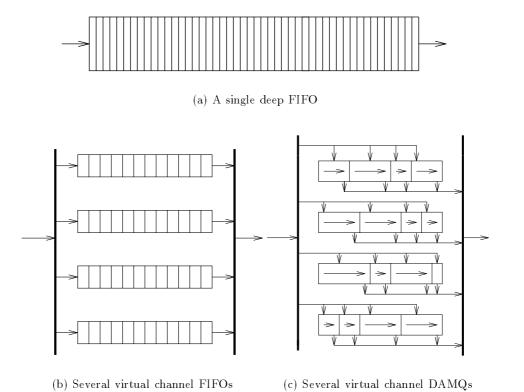

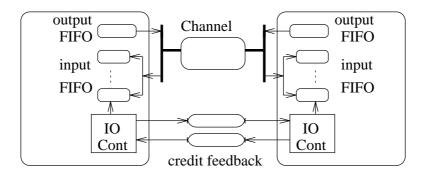

Figure 3.3: FIFO queue configurations. See Sec. 3.3.1 and 3.3.2 for discussion.

#### 3.3.1 Virtual Channel Configuration

A virtual channel is implemented by use of a buffer which can store one or more flits. Instead of having a deep FIFO structure, we may organize the buffers into several independent lanes, *i.e.*, virtual channels (Fig. 3.3). The buffer in each virtual channel can be allocated independently of other virtual channels for different packets, but the virtual channels which are associated with the same physical channel will compete with each other for the channel bandwidth.

When one virtual channel is blocked due to traffic contention, other virtual channels need not be idle since they can still make use of the physical channel. Therefore, virtual channels improve the network throughput substantially for heavily loaded traffic. Adding virtual channels and restricting the routing relation among some virtual channels can eliminate circular channel dependency to avoid deadlock (Chapter 4). Many wormhole routing algorithms are based on virtual channels for this reason. Chapter 4 describes channel dependency and some particular routing algorithms in detail.

#### 3.3.2 Dynamically Allocated Multi-Queue

Organizing buffers such that there are several parallel lanes, *i.e.*, virtual channels, increases the efficiency of physical channels. However, if the buffers within a virtual channel are arranged as a FIFO, then it is still possible that packets in the virtual channel can be blocked unnecessarily. For example, if the packet at the head of FIFO is blocked because it requests a busy output port, then all the packets behind it will be blocked even though they are destined for output ports that are idle.

A dynamically allocated multi-queue (DAMQ) arrangement has been proposed to reduce the effect of "blocked-by-head" (Tamir and Frazier, 1992) (Fig. 3.3 (c)). Packets in a DAMQ buffer destined for different output ports can be accessed separately, and the free space reassigned dynamically to any packet. Multiple queues of packets are maintained in linked lists. Each output direction has its own linked list associated with an input virtual channel. There is another linked list to keep track of free space available. When a packet arrives at the input port, a free space is removed from the free list and linked to the tail of the list corresponding to the output port to which the packet will be routed. When the packet leaves the input buffer, this space will be returned to the free linked list. All the heads of the linked lists for different output directions in an input virtual channel can issue their requests to the router. So there may be more than one request from an input virtual channel configured as a DAMQ while there is at most one request if configured as a conventional FIFO. All the requests are arbitrated so that only one request can be granted per input and output port.

Use of a DAMQ can increase the router throughput and utilization because one of the requests from an input port must be granted if there is no output conflict with other requests from other input ports. However, we have to decide to which output port the packet will be routed when the header arrives at the input port in order to make a proper linked list. Consequently, a routing decision has to be made very quickly upon the arrival of a new packet. Moreover, after a linked list associated with an output direction is established, it is not easy to change the desired output direction of the packet. Thus, it is difficult to implement a DAMQ with adaptive routing (Section 4.2) where the routing direction may be changed due to local traffic contention.

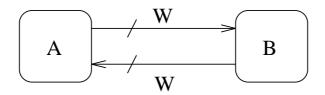

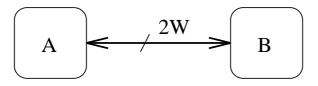

The links between two adjacent nodes can be organized either as a pair of opposite unidirectional channels, one for transmitting and the other for receiving (Reese et al., 1994), or combined into a single bi-directional channel (Fig 3.4). The choice of different link configurations affects the efficiency of channel utilization. If the total link width is a constant 2W, then a single bi-directional channel can have full channel width 2W, but each uni-directional channel can only have half of the channel width. When two uni-directional channels are not fully utilized, one may be busy while the other is idle, and up to one half of the channel bandwidth is wasted. However, bi-directional channels may have longer propagation delay due to increased capacitance loading on the channel. Also, a special arbitration is necessary for bi-directional channels to prevent conflict and deadlock, and this arbitration introduces some additional overhead. Doubling the bandwidth available for data transmission halves the packet length in terms of flits because each flit size is doubled, and the same amount of information can be encoded into one half the number of flits. Buffer storage is halved also in terms of the number of flits if the total storage space is constant. Therefore if a packet is blocked in the network, it will be distributed over the same number of nodes regardless of which scheme we use.

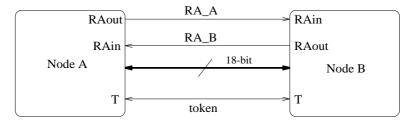

#### 3.4.1 Token Exchange for Bi-directional Channels

A token exchange mechanism is used for single bi-directional channels to prevent conflict caused by two neighboring nodes attempting to use the channel at the same time. A token is associated with each physical channel. Only the node with the token uses the channel to transmit data. A node without the token listens to the channel as a receiver. When a receiving node has data to transmit, it sends a request to the adjacent node which currently "owns" the token. The current "owner" can grant the request by sending an acknowledgment back to the requesting node, and the roles of these two nodes exchange (Dally and Song, 1987).

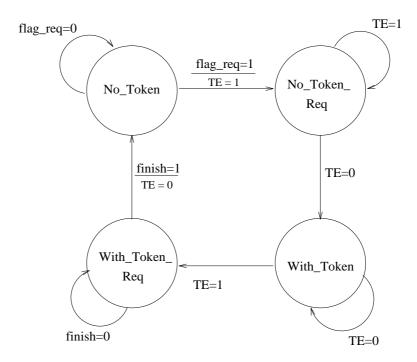

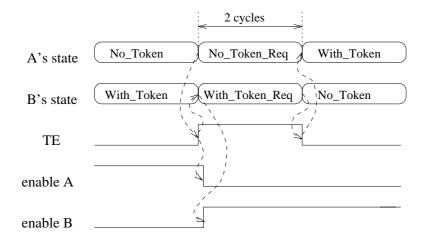

The state diagram of the token exchange is shown in Fig. 3.5. Two neighboring nodes, A and B, start at state *No\_token* and *With\_token*, respectively. The signal *TE* is low initially. Node A, which does not have the token, can send a request by making TE=1, and enter state *No\_token\_req*. Node B, which is in state *With\_token*, goes to state *With\_token\_req* after *TE* goes high. Node B will wait in state *With\_token\_req* until the *finish* signal goes high, which means it can give up the token now. Then node B will lower *TE* and enters state *No\_token*.

(a) Two uni-directional channels

(b) Single bi-directional channel

Figure 3.4: Channel configuration

Node A, which now is waiting in state *No\_token\_req*, senses the signal *TE* becoming low, and knows that the token has been granted. It enters state *With\_token* and begins to transmit data. Fig. 3.6 shows the timing diagram of the token-exchange handshaking between node A and B where *enableA* and *enableB* designate which node is driving the signal *TE*.

One of two conditions must hold if a node is to give up its token (finish=1): 1) it was idle in the previous cycle, or 2) the previous flit it sent is a tail of a packet.

#### **Theorem 1** The token-exchange channel arbitration is conflict-free and deadlock-free.

**Proof:** First, we will prove the property of "conservation of token," *i.e.*, there is one and only one token associated with a channel. From the definition of token states, only the node in the state named with *With\_token* or *With\_token\_req* has the channel token. The token exchange takes place when *TE* goes from high to low (Fig. 3.6). This event is triggered by the state transition from *With\_token\_req* to *No\_token* in node B, and will cause the state transition from *No\_token\_req* to *With\_token* in node A. This sequence of transitions transfers the token from A to B without any overlap and completes in finite time (less than one clock cycle). Therefore, conservation of token holds.

Figure 3.5: Token exchange state diagram

Figure 3.6: Token exchange timing diagram

The state transition from *With\_token\_req* to *No\_token* is caused by *finish=1*. The conditions for setting *finish* guarantee that *finish* will equal one in finite time because the packet length is finite. So this state transition will complete in finite time and the token exchange can also complete in finite time.

Based on the above two properties: conservation of token and finite-time token exchange, we can conclude that it is conflict-free and deadlock-free.  $\Box$

In the ideal case of no traffic contention the time for token exchange need not increase the latency. In practice, network routers are pipelined; for example, in a four-stage pipeline the elements might be an input buffer, header decoder, crossbar switch, and output control. Use of the output channel and the token-exchange are in the last stage of pipeline. The need to request the channel token is always known before the last stage, for example, in the header decoder stage. So the request for the token can be made in advance, for example, in the crossbar switch stage. Without traffic contention, the token transfer "just in time" for the next cycle, *i.e.*, the output control stage, and hide the token-exchange latency.

The other issue related to the bi-directional channel is that when we have the full bandwidth of the channel, the width of each flit is doubled compared with the uni-directional case, which means the crossbar switch inside the node must double too. But the total area and capacitance loading of a multiline switch are proportional to the square of the width of a flit, and the penalty for increasing the size of the switch is high. We can approach the problem of switching in another way. In our experience, the critical path inside a node is the header decoding. Although the crossbar usually is heavily loaded, it has very shallow logic depth, and is much faster than the path in the header decoding, especially for adaptive routing. Therefore we may keep the size of the crossbar unchanged but double the clock in the crossbar to match the bandwidth of the external channels.

We will show in simulation that in spite of the increased overhead of token exchange, the single bi-directional channel has better overall channel utilization, and thus better latency-throughput performance (see Chapter 5).

## Chapter 4

# Wormhole Routing Algorithms

In this chapter, we give the theoretical background and definitions required to understand wormhole data routing. We develop the routing algorithms in the following sections.

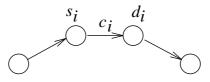

A routing algorithm determines where to send a packet according to its source, destination, and possibly local traffic conditions. An interconnection network, as defined in Chapter 2, is a uni-directed graph G = (N, C), with vertices  $N = \{n_1, n_2, \ldots, n_m\}$  corresponding to the nodes and edges  $C = \{c_1, c_2, \ldots, c_n\}$  corresponding to the communication channels between nodes. For a channel  $c_i$ , the nodes  $s_i$  and  $d_i$  are the source and destination of  $c_i$ , such that source $(c_i)=s_i$  and dest $(c_i)=d_i$ , respectively (Fig. 4.1). We use the following definitions (Definition 1 to 4) from Duato (1993):

#### **Definition 1** Routing Function R

A routing function  $R: N \times N \to P(C)$ , where P(C) is the set of communication channels C, provides a set of alternative output channels to send a packet from the current node  $n_c$  to the destination  $n_d$ , i.e.,  $R(n_c, n_d) = \{c_{c_1}, c_{c_2}, \ldots, c_{c_p}\}$ , where  $source(c_{c_i}) = n_c$ .

A routing function defines all the permissible movements which avoid deadlock and guarantee delivery according to the current position and destination. For an adaptive routing, we

**Figure 4.1:** Channel  $c_i$  has a source node  $s_i$  and destination node  $d_i$

may have more than one possible output channel supplied by the routing function if  $n_c \neq n_d$ . On the other hand, for a deterministic routing, there is only one possible output channel given any pair  $(n_c, n_d)$  if  $n_c \neq n_d$ .

#### **Definition 2** Local traffic F

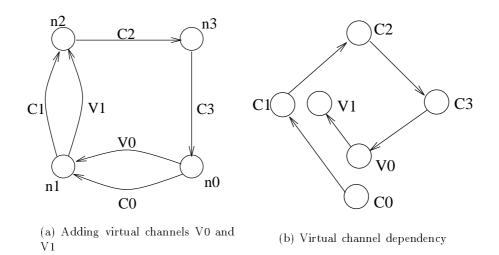

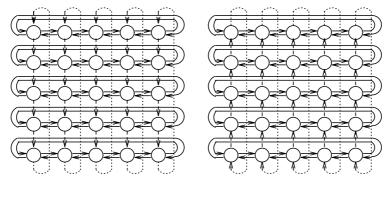

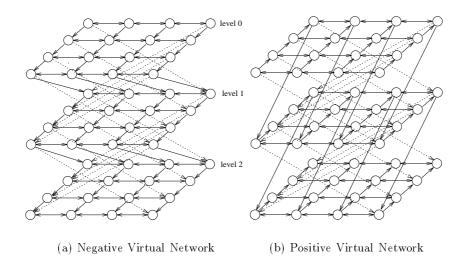

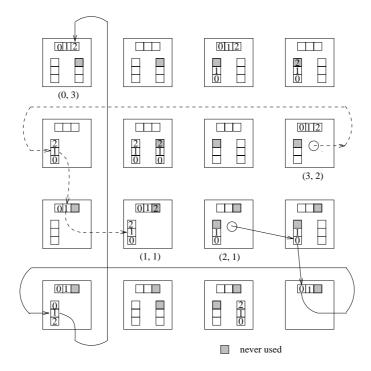

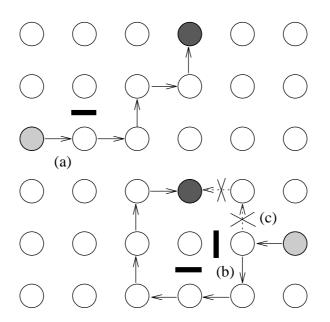

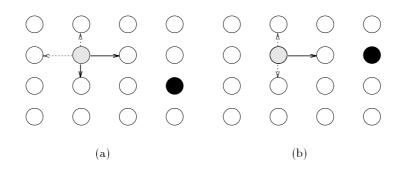

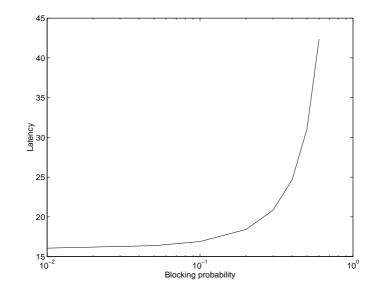

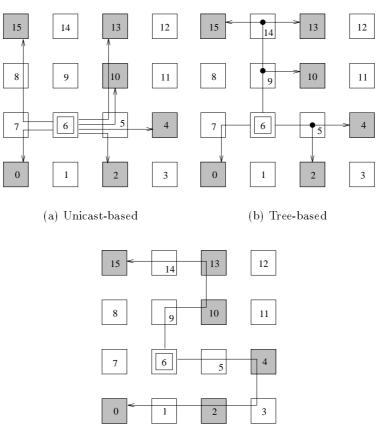

Local traffic F specifies the traffic conditions of the output channels in a node.