## COMPUTER ASSISTED ANALYSIS OF MULTIPROCESSOR MEMORY SYSTEMS

#### SeunqJoon Park

Technical Report: CSL-TR-96-696 June 1996

Computer Systems Laboratory

Departments of Electrical Engineering and Computer Science

Stanford University

Stanford, CA 94305-4055

e-mail: pubs@shasta.stanford.edu

#### Abstract

Parallel architecture becomes more and more attractive as the demand for performance increases. One of the most important classes of parallel machines is that of shared memory architectures, which are perceived as easier to program than other parallel architectures. In a shared memory multiprocessor architecture, a memory model describes the behavior of the memory system as observed at the user-level. A cache coherence protocol aims to conform to a memory model by maintaining consistency among the multiple copies of cached data and the data in main memory. Memory models and cache coherence protocols can be quite complex and subtle, creating a real possibility of misunderstandings and actual design errors. In this thesis, we will present solutions to the problems of specifying memory models and verifying the correctness of cache coherence protocols.

Weaker memory models for multiprocessor systems allow higher-performance implementation techniques for memory systems. However, weak memory models are also very subtle. Hence, it is vital to specify memory models precisely and to verify that the programs running under a memory model satisfy desired properties. Our approach to these problems is to write an executable specification of the memory model

using a high-level description language for concurrent systems. This executable description provides a precise specification of the machine architecture for implementors and programmers. Moreover, the availability of automatic verification tools allows users to experiment with the effects of the memory model on small assembly-language routines. Running the verifier can be very effective at clarifying the subtle details of the models and synchronization routines.

Cache coherence protocols, like other protocols for distributed systems, simulate atomic transactions in environments where atomic implementations are impossible. Based on this observation, we propose a verification method which compares a state graph of the implementation with a specification which is also a state graph representing the desired abstract behavior. The comparison is done through an aggregation function, which maps the sequence of implementation steps for each transaction to the corresponding transaction step in the specification. An aggregation function supplied by the user is formally proved in full detail to have certain properties using a computer-assisted theorem prover.

The aggregation approach is applied to verification of the cache coherence protocol in the FLASH multiprocessor system. The protocol, consisting of more than a hundred implementation steps, is proved to conform to a reduced description with six kinds of atomic transactions. From the reduced behavior, it is very easy to prove crucial properties of the protocol, including data consistency of cached copies at the user level. The aggregation method is also used to prove that the reduced protocol satisfies a desired memory consistency model.

#### Key Words and Phrease:

Multiprocessors, Memory models, Cache coherence protocols, Specification, Verification.

© Copyright 1996 Seungjoon Park

## Acknowledgments

This work would not have been possible without the help of many people. First among these is my research advisor Professor David Dill. It has been a pleasure and privilege to learn from him how to conduct research and present it. I started to study multiprocessor memory systems at his suggestion. Throughout my years at Stanford, he has always been a constant source of technical feedback and encouragement. I remember working with David on writing papers at some nights, roaming in the dark Stanford Shopping Center to find food for late dinners. I also cannot forget the hearty meal at his home for Thanksgiving with chicken simulating turkey when I was the only student who could not visit home during the holidays.

I would like to thank the other members of my committee, my associate advisor Professor Giovanni De Micheli and Professor Gene Franklin, for their careful reading and helpful comments on my thesis. I am also grateful to Professor Jim Harris and Dr. John Rushby who kindly served on my orals committee.

Working with the fellows in our research group was a joy. Former students, Kenneth Yun and Alan Hu; previous and current officemates, Han Yang, Norris Ip, and Supratik Chakraborty; and other colleagues, Jeffrey Su, Robert Jones, Clark Barrett, and Ulrich Stern; I thank them for friendship and technical assistance, especially for their help on my orals. I also thank Ganesh Gopalakrishnan, a visiting Professor, for his interest and comments on my thesis.

I benefited from many discussions and suggestions from the SPARC design team. Most of the detailed definition of the SPARC memory models was done by a group consisting of Dennis Allison, David Dill, Kourosh Gharachorloo, Paul Loewenstein,

Andreas Nowatzyk, and me. Feedback from these individuals was essential in developing the executable memory model in Chapter 2.

I was fortunate to participate in the FLASH multiprocessor project. Mark Heinrich clarified many details in the FLASH protocol which is used in Chapter 4.

I owe a special acknowledgment to the researchers at SRI International: John Rushby, Natarajan Shankar, Sam Owre, Mandayam Srivas, Sree Rajan, and David Cyrluk, who made my days there enjoyable when I was working as a visiting fellow. In particular, I thank Sam Owre for answering numerous questions about their verifier.

Financial support from the following agencies is gratefully acknowledged: the Advanced Research Projects Agency (through NASA grant NAG-2-891), the National Science Foundation (grant MIP-8858807). I am also grateful for my Korean Government Scholarship for Overseas Study.

I would also like to thank Korean friends and senior students who helped me to settle down at Stanford, and professors who taught me during my undergraduate and master years at Seoul National University.

Many thanks are due to my wife Yookyung, who always makes me smile with her amiable nature, for her support while she was also busy finishing her dissertation. Finally, my eternal gratitude goes to my parents for their endless love, care, and belief in me.

> SeungJoon Park May 1996

# Contents

| Acknowledgments |                                             |                 |                                                                |     |  |

|-----------------|---------------------------------------------|-----------------|----------------------------------------------------------------|-----|--|

| 1               | Introduction                                |                 |                                                                |     |  |

|                 | 1.1                                         | Motiv           | ation                                                          | 1   |  |

|                 | 1.2                                         | Backg           | round                                                          | 3   |  |

|                 |                                             | 1.2.1           | Memory consistency models                                      | 3   |  |

|                 |                                             | 1.2.2           | Cache coherence protocols                                      | 5   |  |

|                 | 1.3 Problems and Related Work               |                 | ems and Related Work                                           | 6   |  |

|                 |                                             | 1.3.1           | Specifying and analyzing memory models                         | 6   |  |

|                 |                                             | 1.3.2           | Verifying cache coherence protocols                            | 7   |  |

|                 | 1.4 Results and Contributions of the Thesis |                 | ts and Contributions of the Thesis                             | 8   |  |

|                 |                                             | 1.4.1           | Executable description and automatic analysis of memory models | s 9 |  |

|                 |                                             | 1.4.2           | Verification method for cache coherence protocols              | 10  |  |

|                 | 1.5                                         | Overv           | riew of the Thesis                                             | 11  |  |

| 2               | Rea                                         | asoning         | g About Memory Models                                          | 13  |  |

|                 | 2.1                                         | Execu           | table Specification of Multiprocessor Memory Models            | 14  |  |

|                 |                                             | C Memory Models | 16                                                             |     |  |

|                 | 2.3                                         | Ç               |                                                                | 18  |  |

|                 |                                             | 2.3.1           | Ordering rules                                                 | 20  |  |

|                 |                                             | 2.3.2           | Value axiom                                                    | 21  |  |

|                 | 2.4                                         | Execu           | table Specification of Relaxed Memory Order                    | 22  |  |

|                 |                                             | 2.4.1           | $\mathrm{Mur} arphi$ description language and verifier system  | 22  |  |

|   |     | 2.4.2                                                      | RMO description in $Mur\varphi$                                  | 24         |  |

|---|-----|------------------------------------------------------------|------------------------------------------------------------------|------------|--|

|   | 2.5 | 2.5 Automatic Analysis and Verification                    |                                                                  |            |  |

|   |     | 2.5.1                                                      | Analyzing test programs with an automatic verifier               | 35         |  |

|   |     | 2.5.2                                                      | Verifying synchronization routines                               | 38         |  |

|   | 2.6 | Forma                                                      | al Proof of Equivalence                                          | 41         |  |

|   |     | 2.6.1                                                      | The set of legal memory orders is equivalent to the set of gen-  |            |  |

|   |     |                                                            | erated memory orders                                             | 43         |  |

|   |     | 2.6.2                                                      | The value axiom of the logical specification is correctly imple- |            |  |

|   |     |                                                            | mented in the executable description                             | 45         |  |

| 3 | Rec | luction                                                    | By Aggregating Distributed Transactions                          | <b>1</b> 9 |  |

|   | 3.1 | The B                                                      | Basic Idea                                                       | 50         |  |

|   |     | 3.1.1                                                      | Related work                                                     | 51         |  |

|   | 3.2 | The V                                                      | Verification Method                                              | 53         |  |

|   | 3.3 | 3.3 The Distributed List Protocol                          |                                                                  |            |  |

|   |     | 3.3.1                                                      | The transactions of the protocol                                 | 57         |  |

|   |     | 3.3.2                                                      | The aggregation function                                         | 61         |  |

|   |     | 3.3.3                                                      | Extracting specification                                         | 62         |  |

|   |     | 3.3.4                                                      | The invariant                                                    | 63         |  |

|   | 3.4 | 3.4 Majority Consensus Algorithm for Distributed Databases |                                                                  |            |  |

|   |     | 3.4.1                                                      | The algorithm                                                    | 64         |  |

|   |     | 3.4.2                                                      | Finding an aggregation function                                  | 68         |  |

|   |     | 3.4.3                                                      | Assignments of specification steps                               | 68         |  |

|   |     | 3.4.4                                                      | Proof                                                            | 69         |  |

|   | 3.5 | Summ                                                       | nary                                                             | 69         |  |

| 4 | Rea | soning                                                     | g About Cache Coherence Protocols                                | 7 1        |  |

|   | 4.1 | Verific                                                    | cation of Cache Coherence Protocols                              | 72         |  |

|   | 4.2 | FLAS                                                       | H Cache Coherence Protocol                                       | 73         |  |

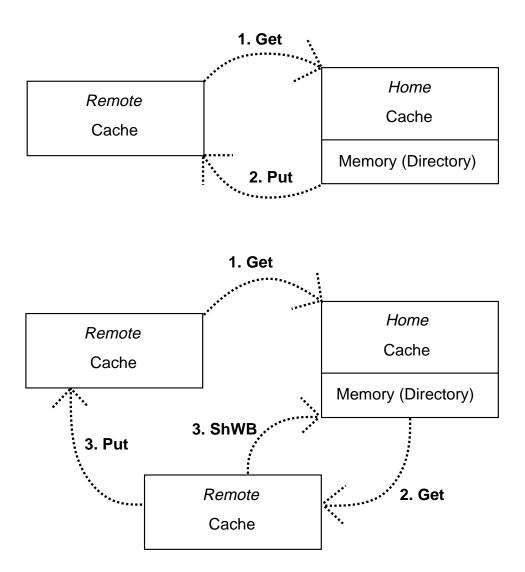

|   |     | 4.2.1                                                      | Informal description of the protocol                             | 73         |  |

|   |     | 4.2.2                                                      | Detailed description of the protocol                             | 76         |  |

|   | 4.3 | Verific                                                    | cation Using A Finite State Method                               | 78         |  |

|    |                                                     | 4.3.1                    | Data structure and global state                | 78  |  |

|----|-----------------------------------------------------|--------------------------|------------------------------------------------|-----|--|

|    |                                                     | 4.3.2                    | Transition relations in rulesets               | 78  |  |

|    |                                                     | 4.3.3                    | Specification of the protocol                  | 81  |  |

|    |                                                     | 4.3.4                    | State explosion problem                        | 82  |  |

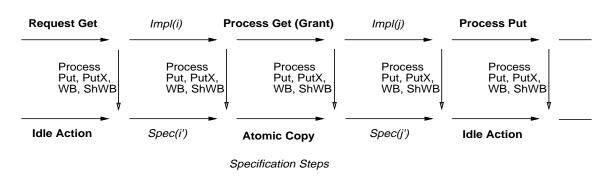

|    | 4.4                                                 | Verific                  | cation By Aggregating Distributed Transactions | 83  |  |

|    |                                                     | 4.4.1                    | Extracting reduced model of the protocol       | 84  |  |

|    |                                                     | 4.4.2                    | Commit steps                                   | 85  |  |

|    |                                                     | 4.4.3                    | Aggregation function                           | 86  |  |

|    |                                                     | 4.4.4                    | Specification steps                            | 87  |  |

|    |                                                     | 4.4.5                    | Invariant                                      | 89  |  |

|    |                                                     | 4.4.6                    | Tricks for using a theorem prover              | 91  |  |

|    | 4.5 Delayed Mode Conforms to Sequential Consistency |                          | ed Mode Conforms to Sequential Consistency     | 91  |  |

|    | 4.6                                                 | Executable Memory Models |                                                |     |  |

|    | 4.7                                                 | Detail                   | led description of FLASH protocol (EAGER mode) | 95  |  |

| 5  | Con                                                 | clusio                   | n                                              | 99  |  |

|    | 5.1                                                 | Summ                     | nary                                           | 99  |  |

|    |                                                     | 5.1.1                    | Executable memory models                       | 99  |  |

|    |                                                     | 5.1.2                    | Verification of cache coherence protocols      | 100 |  |

|    | 5.2                                                 | Future                   | e Research                                     | 101 |  |

| Bi | ibliog                                              | raphy                    | <del>.</del>                                   | 102 |  |

## Chapter 1

## Introduction

#### 1.1 Motivation

Parallel architectures are becoming more and more attractive as the demand for higher performance increases. Many multiprocessors are currently being designed to meet this demand. The scale of parallelism is increasing rapidly, and the use of parallelism is widening as technological improvements reduce costs [57, 29].

For highly parallel architectures to achieve widespread use, they must run a variety of applications efficiently without imposing excessive programming difficulty. From this view, one of the most important classes of parallel architectures is *shared memory architectures*. Shared memory (also called shared address-space) architectures are very attractive for application programmers, because they are perceived as easier to program than other parallel architectures, at least for some applications. In fact, the majority of parallel machines that are sold today are based on shared memory.

Complex systems, particularly those involving parallelism, are difficult to design. One of the major problems is how to avoid design errors resulting from unexpected interactions among system components. Validating the correctness of a design before implementation is essential because it is difficult and expensive to correct errors after a machine is built and the hardware is committed [61, 8, 68, 28].

It is widely believed by designers that system design problems are outstripping current design debugging techniques. Random testing and trace-driven simulations are not sufficient for validation because coverage declines as design complexity increases, so bugs remain undetected by simulations. Moreover, it is not unusual to find bugs even in algorithms and protocols that have been proved correct by hand, because of errors in the proofs.

The general objective of this research is to develop improved methods for debugging and assuring the correctness of high-level multiprocessor designs. We have focussed on large-scale shared-memory multiprocessors as the domain, because there is currently a great deal of interest in designing them [39, 3, 52, 65, 32]. To expedite the validation process and to reveal possible mistakes in human reasoning, computer assistance is necessary.

In a shared memory multiprocessor architecture, a memory model describes the behavior of the memory system observed at the user level. A memory model specifies the semantics of memory operations when multiple processors load and store shared memory locations. The model also provides a programmer-level view of memory transactions ordering. Given a multiprocessor program, a memory model provides sufficient information to determine the set of possible results of the program.

Unfortunately, defining and reasoning about memory models can be very difficult. In this dissertation, we describe methods for defining executable specifications of memory models in a description language that is suitable for verification. The automatic verifier can be used to enumerate all the outcomes of an example program, or to check the correctness of simple synchronization routines.

Most shared memory multiprocessors implement caches which keep multiple copies of data for a given memory location, to provide an illusion of a single shared memory while providing rapid access to data from multiple processors. The use of caches exploits the temporal and spatial locality of memory accesses by the multiprocessors, improving the performance of the memory system. However, dealing with multiple copies of a datum raises a consistency problem: a cached copy of a memory location may not be consistent with other cached copies of the same memory location.

In such implementations, a *cache coherence protocol* aims to maintain consistency among the multiple copies of cached data and the data in main memory. A cache coherence protocol is a lower-level abstraction of a memory system which should

1.2. Background 3

conform to the memory model which is a higher-level abstraction of the memory system.

We also present methods for formally verifying cache coherence protocols. One of the methods is to use a finite-state verifier. A more general (but more difficult) approach is to use a general-purpose computer-assisted theorem-prover. We present a new way to use theorem-proving to verify cache coherence protocols, which is based on aggregating implementation steps into high-level transactions.

## 1.2 Background

This thesis aims to propose better approaches to reasoning about memory models and cache coherence protocols for shared memory architectures, which are two different levels of abstraction of multiprocessor memory systems. This section introduces background for the research.

#### 1.2.1 Memory consistency models

In a shared memory multiprocessor architecture, a memory model is a user-level description of the *behavior* of the memory system. A memory model specifies the semantics of memory operations when multiple processors load and store shared memory locations. In other words, the memory model should be a precise specification of how memory behaves with respect to read and write operations from multiple processors.

Several memory models for shared memory multiprocessor architectures have been proposed. An early model, sequential consistency [42], simply requires that multiprocessors simulate atomic reads and writes to a common global memory observing the sequential order defined in a program. This model is relatively easy to understand but has strong constraints which hinder high performance implementations.

Unfortunately, sequential consistency constrains the range of behaviors of the memory system to such a degree that it cannot be implemented efficiently in hardware. Consequently, many less constraining memory models have been proposed, which make fewer guarantees about behavior (we call these weaker memory models).

This allows more concurrency in memory system and processor implementations, resulting in improved performance. During the past decade, a lot of effort has been made to design weaker memory models, such as processor consistency [27], weak consistency [20], total store ordering, partial store ordering [35], release consistency [25], and relaxed memory order [66].

A memory model provides sufficient information to determine the results of a program running under the memory system. In other words, given a program, we should be able to know what results are possible and what are impossible from the specified memory model without worrying about its detailed implementation.

To illustrate why it is important to understand memory models, let us consider an example. The following parallel program demonstrates how memory models affect program behavior.

| Processor $P_0$    | Processor $P_1$    |  |  |

|--------------------|--------------------|--|--|

| store $\#1 \to A$  | store $\#1 \to B$  |  |  |

| load $B \to \%r_0$ | load $A \to \%r_1$ |  |  |

Processor  $P_0$  stores constant value 1 to memory address A, then it loads memory address B to its register  $\%r_0$ . Processor  $P_1$  does similar instructions. We assume all the registers and memory locations initially contain zero values.

Suppose the program is running on multiprocessors with a memory system which implements the sequential consistency memory model. In this case, either  $\%r_0$  or  $\%r_1$  should obtain value 1 after the program is executed, because at least one of the two stores must be performed before both of the loads.

However, this result may not be guaranteed if the memory system is based on a weaker memory model which allows more freedom in executing memory instructions. One of the widely-used techniques in implementing efficient memory systems for single processor machines is to use write buffers to delay store transactions while subsequent loads are performed. This technique does not make a visible difference to the user running on a single processor machine. However, the same technique produces different program results when applied to a multiprocessor memory system. For example, suppose each processor issues the corresponding store into its own write buffer. Before any of the stores are performed by the main memory,  $P_0$  loads the

1.2. Background 5

memory location B reading the initial value 0 from the main memory, and  $P_1$  also loads the memory location A reading the initial value 0, also from the main memory. Then, the two stores are performed to the main memory. In this case, the result of the program is  $\%r_0 = \%r_1 = 0$ , which was not allowed by the sequential consistency model.

As we observed from the example, different memory models produce different program results. With simpler memory models, it is relatively easy to program and to reason about results of programs, because their strong requirements allow less diverse executions. However, the strong constraints hinder high performance implementations.

Using weaker memory models allows many efficient implementation techniques in hardware design by exploiting more parallelism. However, weaker memory models are generally very subtle, because understanding the behavior of highly concurrent systems is never easy. Thus, there is a tension between the simplicity of memory models and performance of memory systems.

#### 1.2.2 Cache coherence protocols

In order to improve performance of memory systems, most of multiprocessor architectures use distributed caches for each processor, which keep local copies of main memory. Because data can be found either in memory or in the multiple caches, coherence problems arise when more than one processor's cache holds a copy of a datum at a shared address [57]. Cache coherence is one of the key aspects that is different in the design of memory systems of multiprocessors from that of uniprocessors.

For instance, to build a memory system supporting the sequential consistency, we wish to ensure that when reading a memory location the processor always sees the latest value written to that location. This is simply achieved in uniprocessors, because normally it is only the processor that is reading and writing memory. However, it is not trivial to obtain coherent caches in multiprocessor systems.

Suppose the multiprocessors execute the following memory accesses in order.

1. Processor  $P_1$  loads a memory location A into its cache  $C_1$ .

- 2. Processor  $P_2$  loads a memory location A into its cache  $C_2$ .

- 3. Processor  $P_2$  stores the memory location A by writing a new value into  $C_2$ .

When  $P_2$  writes a new value into  $C_2$ , the cached value in  $C_1$  and the datum in main memory at location A should be invalidated or updated. Otherwise, future reads to the memory location by a third processor may load the old value in the main memory; and future loads by  $P_1$  may get the old value in  $C_1$ .

In shared memory architectures, cache coherence protocols maintain the consistency among multiple cached data and data in main memory. The protocols control a number of readable and writable copies of each memory location for multiprocessors in distributed caches. Modification of one copy of a datum may require updating other copies to maintain consistency among them.

#### 1.3 Problems and Related Work

This section presents some of the problems in analyzing multiprocessor memory systems and related work by others.

### 1.3.1 Specifying and analyzing memory models

Weaker memory models for multiprocessors allow higher-performance implementation techniques for memory systems. However, their behavior may be sometimes counter-intuitive. Therefore, it is vital to specify a memory model precisely.

The precise details of the memory model are crucial to several parties. Obviously, programmers must be aware of the model to write correct and efficient shared memory programs; for example, the model affects the correctness of synchronization routines. Multiprocessor designers should understand the model because the design of the cache coherence scheme must respect the model. Also, processor designers must ensure that processor optimization techniques such as out-of-order issue of memory instructions and register renaming do not violate the model model. Compiler writers may also have to consider the memory model in some optimizations.

Memory model descriptions in English can be ambiguous. Unfortunately, precisely defining the semantics of a memory model often leads to complex specifications that are difficult to understand for typical users such as programmers and hardware builders of computer systems.

Many formal specifications of memory models are written in mathematics. Collier [13] specifies memory models using partial orders and infers the behavior of programs from a set of ordering relations. Gharachorloo [24] and Sindhu and Frailong [62] have used methods similar to Collier's. Another way to specify memory models is using automata. Gibbons et al. [26] use I/O automata, and Hojati et al. [33] use L-automata to specify and reason about memory models.

However, such specifications require that the users infer the behavior of programs from a set of ordering constraints or by reasoning about automata. For those not familiar with such formal notation, it is hard to reason about programs running on multiprocessors by manual computation—and almost impossible for large programs even for experts.

#### 1.3.2 Verifying cache coherence protocols

Cache coherence protocols can be quite complex and subtle, creating a real possibility of design errors, especially for those used in large-scale multiprocessor systems. Formal verification is desirable because the bugs can be quite subtle and hard to capture by simulation. Several coherence protocols have been proposed but few are formally verified [4, 67, 9, 47].

One of the effective ways to validate protocols is using finite-state methods (model checking). Finite-state methods enumerate the states of the reachable state graph of the system, searching for states that violate a specified property (e.g.  $Mur\varphi$  [15], SMV [21], SPIN [34], COSPAN [38]).

These methods suffer from the state explosion problem: the number of states for nontrivial numbers of processors and cache lines is very large. For example, the  $Mur\varphi$  verifier can barely handle a relatively simple protocol with 3 processors and 2 memory lines using 100 megabytes of memory in the process.

Another problem with the model checkers is that it is very difficult to specify

correctness conditions of the protocol using notations such as  $Mur\varphi$  or temporal logic. The specification is the corresponding memory model of the protocol so it is required to encode a full memory model in temporal logic.

Symbolic state models proposed by Pong and Dubois [60, 59] reduce the state explosion problem by using symbolic states which abstract away from the exact number of configurations of replicated identical components by recording only whether there are zero, one, or more than zero replicated components. However, there still remains a specification problem of the protocol as in model checking: It is not easy to find a set of properties in their notation, which completely describes the correct behavior of the protocols. Moreover, their method requires the user to write an abstract description of the protocol to be verified, which raises another verification problem that the abstract description and the actual protocol are equivalent.

Another approach to formal verification is computer-assisted theorem-proving. Theorem-provers make available the full power of formal mathematics for proof, so they can routinely deal with problems that cannot yet be solved by any finite-state methods.

However, the major problem with theorem proving is that considerable labor is required. Consequently, previous theorem proving approaches have not been able to verify a problem of the scale of a full multiprocessor cache coherence protocol. The most significant result to date is a manual proof of "lazy caching," a simple and abstract cache coherence algorithm [2, 23, 40].

Overall, the finite-state method and theorem-proving have been applied to simple and small protocol models. However, we expect that the complexity of cache protocols will continue to increase as faster and larger relaxed memory models are implemented. Then verifying cache coherence protocols becomes a serious challenge which must be met with appropriate and efficient techniques.

### 1.4 Results and Contributions of the Thesis

This thesis will present solutions to the problems of specifying and analyzing memory models, and verifying the correctness of cache coherence protocols.

# 1.4.1 Executable description and automatic analysis of memory models

We present a new approach for specifying a memory model for multiprocessors. We describe the memory model by giving a maximally general executable description [54, 18], using a high-level description language for concurrent systems called  $\text{Mur}\varphi$  [15]. Such a description provides a precise specification of the machine architecture, both for programmers and hardware implementors.

The major advantage of using  $Mur\varphi$  is that it is also an automatic verification system. There is a tool that supports exhaustive checking of all the reachable states of a description for violations of user-specified properties. Using the verifier allows users to experiment with the effects of the memory model on programs being executed in the memory system. Running the verifier can be very effective at clarifying the subtle details of the models.

The Mur $\varphi$  verifier is used for several different kinds of automatic analysis. First of all, we can formally verify the synchronization routines for a memory model which are the most frequently used and important programs of the multiprocessor memory system. Mur $\varphi$  also allows the printing of the state of a system at user-specified points while exploring the reachable states. This feature has been used to list all of the possible register values that can occur when an example program terminates. Consequently, we can obtain a complete list of possible program results for a given multiprocessor program running in a specified memory model. If we obtain an unexpected output, the verifier can also be used to generate an execution producing a trace to the specific output. This feature helps programmers to understand the memory behavior and to correct their programs.

We developed an executable memory model during the process of defining the RMO (Relaxed Memory Order) memory model of the SPARC Architecture Version 9 [66]. The RMO is a generalization of the previous SPARC Version 8 memory models, TSO (Total Store Ordering) and PSO (Partial Store Ordering) [18].

Developing an executable model of RMO in  $\text{Mur}\varphi$  greatly enhanced our understanding and confidence in the design for several reasons. First, writing a precise

description pointed out ambiguities and inconsistencies, even without executing the description. Second, we were able to analyze the possible outcomes of illustrative examples and synchronization programs rapidly and automatically, when there was a question about the implications of a change in detail of the specification. Third, we could verify the examples in the SPARC Architecture Manual Version 9, which increased our confidence that there were no errors in the code examples associated with the memory models [54]. Overall, our approach has been extensively used in the design procedure, and it was very helpful for the SPARC-V9 design team.

The executable description should be a maximally general implementation of the axiomatic specification so that it can be used as an *equivalent specification*. We have done a high-level formal proof of the equivalence that the executable specification generates all the possible behavior that is allowed by the axiomatic specification, and that executions generated by the executable description are allowed by the axiomatic specification.

#### 1.4.2 Verification method for cache coherence protocols

We present a new approach for using a computer-assisted theorem-prover to verify the correctness of protocols and distributed algorithms. The method aims to overcome the finiteness constraint of model checking and to exploit advantages of theorem-proving in verifying cache coherence protocols.

The method compares a state graph of the implementation with a specification which is also a state graph representing the desired abstract behavior. The steps in the specification correspond to atomic transactions, which are not atomic in the implementation.

The method relies on an aggregation function, which is a kind of an abstraction function that aggregates the steps of each transaction in the implementation into a single atomic transaction in the specification [55]. We present an easy and systematic way to find such an aggregation function. The method substantially reduces the amount of labor required, hence significantly extends capability of computer-assisted theorem-proving for cache coherence protocols.

Owing to the generality obtained by the use of logic as a formalism, we have been

able to validate protocols with an arbitrary number of processors. Our method has successfully verified the safety properties of the FLASH cache coherence protocol [39, 30]. For several years, we believed that proving the correctness of protocols of the complexity of the FLASH cache coherence protocol was well beyond the capability of a general-purpose theorem prover. The aggregation method has broken through this barrier.

The method also solves the specification problem. The aggregation renders a reduced model of the implementation, which can serve as a specification, if none exist.

The proposed verification procedure is not only for cache coherence protocols but also has been applied to other protocols, which are simple but non-trivial: majority consensus algorithm for multiple copy databases [64, 37], and a distributed list protocol [17].

### 1.5 Overview of the Thesis

Chapter 2 presents techniques for writing executable memory models in a high-level description language for concurrent systems. The techniques are applied to the Relaxed Memory Order of SPARC Version 9 Architecture as well as the earlier, simpler models TSO and PSO. This chapter also demonstrates several ways to use an automatic verification tool for analyzing the memory model: verification of synchronization routines, generation of complete lists of possible program results, and generation of an execution trace for a specific program result.

Chapter 3 explains the aggregation method for verification of cache coherence protocols and similar distributed algorithms using a computer-assisted theorem prover. The method is illustrated on the examples, a distributed list protocol and a majority consensus algorithm for multiple copy databases.

Chapter 4 presents verification of the FLASH cache coherence protocol. The protocol is briefly described, and a finite-state method is used to verify some properties of the protocol. Next, the aggregation method presented in Chapter 3 is applied to verify the protocol with arbitrary numbers of processors.

Finally, Chapter 5 summarizes the thesis and discusses possibilities for future research.

# Chapter 2

# Reasoning About Memory Models

In this chapter, the Mur $\varphi$  description language and verification system for finite-state concurrent systems is applied to the problem of specifying a family of multiprocessor memory models in the SPARC Architecture Manual Version 9. This chapter describes the memory models and their encoding in the Mur $\varphi$  description language, and presents several techniques using its automatic verifier for analysis of programs running under the specified memory models.

The description language allows for a straightforward executable description of the memory model which can be used as a specification for programmers and machine architects. The automatic verifier can be used to generate all possible outcomes of small assembly-language multiprocessor programs in a specified memory model, which is very helpful for understanding the subtleties of the model. The verifier can also check the correctness of assembly language programs including synchronization routines.

Section 2.1 discusses general problems of specifying abstract memory models for multiprocessors. Section 2.2 explains the intuition behind memory models of SPARC-V9 architecture. Section 2.3 presents the logical specification of Relaxed Memory Order of SPARC-V9. Section 2.4 demonstrates how to write an executable specification using the description language. Section 2.5 presents techniques to verify synchronization routines and to analyze finite state programs using the automatic verifier. We

also present some interesting findings from the verification and the analysis. Section 2.6 contains a formal proof that the executable specification is equivalent to the logical specification.

## 2.1 Executable Specification of Multiprocessor Memory Models

In a shared memory multiprocessor architecture, a memory model specifies the semantics of memory operations when multiple processors load and store shared memory locations. The precise details of this model are crucial to several parties: programmers, multiprocessor system designers, processor designers, compilers, and hardware implementors.

Several memory models for shared memory multiprocessor architecture have been proposed. Weaker memory models are attractive because they allow better more concurrency in memory system and processor implementations, resulting in improved performance. However, weaker memory models are generally very subtle. Even sequential consistency can be counter-intuitive at times. Hence, it is vital to specify a memory model precisely.

Our approach to these problems is to describe the memory model by giving a  $maximally\ general$  executable description [54], using a high-level description language for concurrent systems called Mur $\varphi$  [15]. Such a description provides a precise specification of the machine architecture, both for implementors and programmers. The major advantage of using Mur $\varphi$  is that it is also an automatic formal verification system. There is a tool that supports exhaustive checking of all the reachable states of a description for violations of user-specified properties. Mur $\varphi$  also allows the printing of the state of a system at user-specified points while exploring the reachable states; this feature can be used, for example, to list all of the possible register values that can occur when an example program terminates.

The approach here is different from that used by Collier [13], who infers the behavior of programs from a set of ordering relations, which are not necessarily easy to convert into an executable form. Gharachorloo [24] and Sindhu and Frailong [62] have used methods similar to Collier's. Our method more closely resembles that of Gibbons, et al. [26], who give I/O automata specifications of memory models. The primary differences here are the description languages, and more importantly, our emphasis on support for automatic analysis, while verification with I/O automata is generally by hand.

It is important to note that the executable description is a maximally general implementation [33] which could be regarded as a formal specification. In other words, all the execution traces generated by the executable model are legal under the logical specification and all the legal execution traces are generated by the executable model. To ascertain this, we present formal proofs, which have been confirmed by automatic theorem provers, that our executable specification in  $\text{Mur}\varphi$  is equivalent to the logical specification.

We developed an executable memory model during the process of defining the Relaxed Memory Order (RMO) model of the SPARC Architecture Manual Version 9 [66]. RMO is a generalization of the previous SPARC Version 8 memory models, TSO (Total Store Ordering) and PSO (Partial Store Ordering). Intuitively, TSO liberalizes sequential ordering by allowing the performance of stores to be delayed relative to subsequent loads; PSO additionally allows stores to be delayed relative to other stores; and RMO further allows loads to be delayed relative to subsequent loads and stores. In [18], we developed an executable model for TSO and PSO; however, the executable model of RMO is not a simple generalization of the earlier description.

Developing an executable model of the protocol in  $\operatorname{Mur}\varphi$  greatly enhanced our understanding and confidence in the design for several reasons. First, writing a precise description points out ambiguities and inconsistencies, even if the description is not executed. Second, we were able to analyze the possible outcomes of illustrative examples and synchronization programs rapidly and automatically, when there was a question about the implication of a change in detail of the specification. Third, we could verify the examples in the architecture manual, which increased our confidence that there were no errors in the code examples associated with the memory models.

## 2.2 SPARC Memory Models

This section explains the intuition behind the SPARC-V9 memory models. It is not intended to be exhaustive or to be a tutorial on the models. For more information, see the SPARC Architecture Manual Version 9 [66].

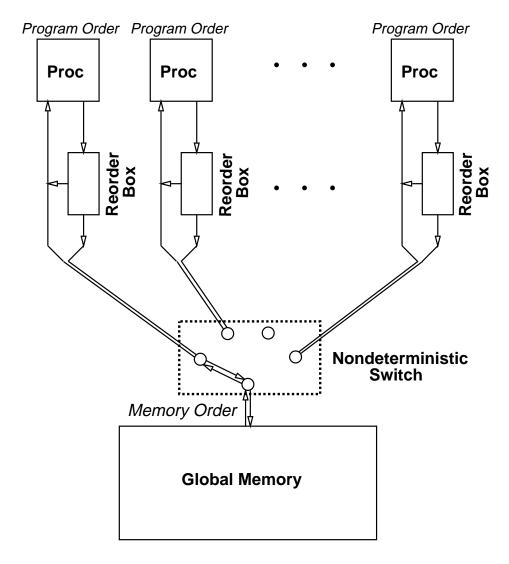

Figure 2.1 illustrates the intuition behind the memory models. Note that this is a fictitious description that bears no relation to a reasonable implementation of a memory model—it is only intended to capture a programmer-level view of the possible behaviors of memory operations. There is a set of processors,  $P_1, P_2, \ldots, P_n$ , each of which has its own cache, and an abstract reorder box. Each processor executes instructions in the natural order specified in the program, called program order. Instructions may appear to occur in some order other than program order, due to various implementation techniques, such as local caching or out-of-order instruction execution in the processor implementation. This reordering is modeled in Figure 2.1 by attaching a reorder box to each processor.

Each reorder box is also connected to a common global memory. The memory arbitrarily chooses one of the reorder boxes, chooses an instruction from the reorder box subject to ordering constraints that are specified as part of the particular memory model. It then executes actions which depend on the instruction, such as updating memory locations or processor registers. The actions for each instruction are executed atomically—other actions in the system cannot interfere with them. An instruction is said to be performed when it is executed by the memory.

It bears repeating that this is not intended to resemble any implementation of a memory system. It is merely a fiction that explains the functional behaviors of programs—without regard to performance. Indeed, the "memory" is doing almost all of the work of executing instructions, including modifying processor registers and even doing arithmetic—in early models, the memory performed much more memory-like functions, which is why we use the term. The lack of a clear separation between processor and memory models is a little awkward, but it seems that ordering constraints from the processor inherently affect the memory model, especially in liberal models such as RMO, so we have found it necessary to generalize the memory in this

Figure 2.1: An abstract memory model for multiprocessors

way.

All SPARC implementations must support the standard memory model, called  $Total\ Store\ Ordering\ (TSO)$  which is also the most restrictive model. In TSO, store operations from a processor  $P_i$  must be performed by the memory in program order. However, a load issued by  $P_i$  may return a value recently stored by  $P_i$  before the store is performed by the global memory. Hence, a processor  $P_j$  may load an old value  $after\ P_i$  has loaded a new value. This last scenario would not be allowed under sequential consistency; TSO is weaker than sequential consistency. Equivalently, any synchronization code that is guaranteed to work properly in TSO will also work properly in a sequentially consistent model, but not the reverse.

The SPARC architecture defines a weaker model called *Partial Store Ordering* (PSO). PSO is similar to TSO except that it allows stores from a processor to be performed without regard to the program order unless they are to the same address. TSO and PSO were the memory models of the SPARC Version 8 architecture.

In order to allow more latitude in multiprocessor implementations, a new model called *Relaxed Memory Order* (RMO) was defined in the SPARC Version 9 architecture. In the TSO and PSO models, a load operation must be performed before any stores that follow it in program order. However, in many cases, RMO allows a store to be performed before a load even if the load occurred first in program order.

# 2.3 Logical Specification of Relaxed Memory Order

This section is a condensed description<sup>1</sup> of the logical specification of the memory model in the SPARC Architecture Manual Version 9. The logical specification is not executable. In essence, given an instruction trace from each processor consisting of the sequence of instructions and the results of interactions with the memory system, it determines whether the instruction trace is compatible with the memory model. This

<sup>&</sup>lt;sup>1</sup>The change we made from the SPARC manual is that we do not differentiate memory transactions from instructions. We believe that such a distinction is not necessary at this level of specification.

is the style of specification used by Collier, Gharachorloo, and Sindhu and Frailong [13, 24, 62].

In the remainder of this chapter, X, Y, and Z refer to memory instructions.  $X_A^n$  denotes a memory instruction X on processor n that reads or writes memory address A. The processor index and memory address are specified only if needed. Predicates L(X) and S(X) are true if X is a load or a store instruction, respectively. L(Y) and S(Y) can be true simultaneously, when Y is an atomic load/store.

A program order is a partial order of instructions that is an interleaving of total orders, one for each processor: instructions associated with the same processor are always program-ordered, while instructions from different processors are never program-ordered. Program order represents the sequence of instructions as issued by each processor. We write  $A <_p B$  when instruction A precedes instruction B in program order.

A memory order is a total order of all the memory instructions from the processors. Each memory model defines a set of ordering rules which constrain legal memory orders. Many memory orders may be consistent with a given program order. This multiplicity of orders reflects nondeterminism in the memory model, and yields nondeterministic results when multiprocessor programs are executed. The choice of a particular global memory order determines the values returned by loads. We write  $A <_m B$  when instruction A precedes instruction B in a particular memory order; also, in this case, we say "A is performed before B."

The SPARC-V9 architecture has a special memory barrier instruction (membar). It explicitly enforces additional constraints on the memory order of certain types of memory instructions preceding and following the membar. For instance, membar {L<S} requires that all the loads preceding the membar in program order precede the stores following it. The predicate M(X,Y) holds when  $X <_p Y$  and X and Y are ordered by a membar of the corresponding type. For example, in the instruction sequence of  $L <_p S <_p \text{ membar}\{L < L, S < S\} <_p L' <_p S', M(L, L') \text{ and } M(S, S') \text{ hold.}$  Therefore,  $S <_m S' <_m L <_m L'$  is a legal memory ordering—if there are no other constraints, but  $S' <_m S <_m L <_m L'$  is not.

A program in a weak memory model can be made to behave like the same program in a stronger model by inserting membars between appropriate instructions. To simulate PSO under RMO, we may insert membar{L<L,L<S} immediately following every load, disabling the freedom of RMO to delay the execution of loads until after the following memory instructions.

#### 2.3.1 Ordering rules

There are some times when ordering constraints from a processor must necessarily constrain the memory order. For example, an instruction loading a register cannot be performed after an instruction storing the resulting register value back to memory; a store cannot be performed before a preceding branch is resolved. The SPARC-V9 memory model defines a dependence order (denoted by  $<_d$ ) which captures the data dependence and control dependence relations among instructions, as one step in the specification of the constraints on memory order. Dependence order is determined from program order as follows.

$A <_d B$ , if  $A <_p B$  and at least one of the following is true.

- (d1) A and B are control dependent and S(B)

- (d2) A writes a register read by B

- (d3) A stores a memory location loaded by B

Precise rules can be defined so that each dependence can be determined between every pair of instructions in a sequence by inspecting the sequence. Rule (d1) requires a branch instruction to a following store. Rule (d2) orders two instructions, if the preceding writes a register which is read by the following. Note that some branch instructions read a special register CCR (condition code register) to decide branching, so a test instruction that write a CCR is dependence ordered to such a branch instruction that read the CCR. Rule (d3) orders a store to a following load which reads the memory location written by the store.

Caution is required in the definition of dependence order, because it constrains memory order. If dependence order is too strict, it may unnecessarily constrain the range of legal processor implementations. There are two specification issues that should be mentioned. First, the definition (d2) does not define a dependence when two instructions write the same register, or when an instruction reads a register then another writes it, in order to allow register renaming in the processor implementation. Second, rule (d1) is defined so that there is a control dependence when an instruction affects a branch which is followed by a store, but not when the following instruction is a load. This ensures that the processor is allowed to do speculative execution of loads after a branch, before the branch has been decided. Both of these decisions affect the executable description, which must include register renaming and speculative execution of loads if it is to be maximally general.

A particular memory total order  $<_m$  is legal if  $X_A <_m Y_B$  whenever one or more of the following conditions holds.

(m1)

$$X_A <_d Y_B$$

and  $L(X_A)$

$$(m2)$$

$M(X_A, Y_B)$

(m3)

$$A = B$$

and  $X_A <_p Y_B$  and  $S(Y_B)$

Rule (m1) says that if two instructions are data dependent ( $<_d$ ) and the first is a load, then they should be performed in order ( $<_m$ ). Preceding stores may be delayed even if there is a data dependence between them and following instructions. Therefore, rule (m1) allows the implementation to use store buffers. Rule (m2) describes the ordering constraint explicitly imposed by membars. Rule (m3) requires that stores to the same address be performed in program order. The rule also orders a load and a following store to the same address, a constraint that is not captured by dependence order. This constraint is necessary to ensure that a single processor behaves as though instructions were performed in program order.

#### 2.3.2 Value axiom

While the ordering rules constrain the performance order of memory instructions, the following axiom defines the value returned by a load:

Value

$$(L_A)$$

= Value ( Maximum  $S_A$  under  $<_m$  from the set of  $\{S_A <_m L_A\} \cup \{S_A <_p L_A\}$ ).

Given a particular memory order, it implies that the value returned by a load is that of the latest store with respect to the memory order that is performed by the shared memory before the load ( $\{S_A <_m L_A\}$ ), or that precedes the load in program order ( $\{S_A <_p L_A\}$ ). Note that the store in the latter case should be the one issued by the same processor which issued the load, since  $<_p$  does not order instructions from different processors.

# 2.4 Executable Specification of Relaxed Memory Order

The executable specification is intended to be maximally general—not only should it conform to the logical specification, it should generate every possible result that is allowed under the specification. Hence, it is more difficult in some ways to write the executable specification than to describe a particular multiprocessor, because a multiprocessor does not have to take advantage of every degree of freedom allowed by the logical specification. On the other hand, the executable model does not have to represent an efficient or practical solution, so it is much easier to design in that sense.

#### 2.4.1 Mur $\varphi$ description language and verifier system

Mur $\varphi$  is a high-level description language for modeling finite-state asynchronous concurrent systems. There is an automatic verifier for Mur $\varphi$  which generates all of the reachable states of the system while checking for deadlock and other error conditions. Mur $\varphi$  can also check liveness and fairness properties (e.g. progress). The syntax of Mur $\varphi$  is derived from various standard programming languages, especially Pascal and C.

$Mur\varphi$  allows the declaration of familiar data types, including subranges of integers, arrays, records, and user-defined enumerations. Additionally, procedures, functions,

and global variables can be declared. The operational part of the language is based on iterated guarded commands—which was inspired by Misra and Chandy's Unity language [10]. A state of the described concurrent system is an assignment to each global variable with a value in the range of the declared type. A  $\text{Mur}\varphi$  program consists of a collection of rules. Each rule has a condition, which is Boolean expression referring to the global variables, and an action, which is a statement that modifies the values of the variables, yielding a new state.

Execution of a  $\operatorname{Mur}\varphi$  program begins with one of a set of initial states specified by the user. Then the following loop is executed forever: some rule whose condition is satisfied by the current state is chosen and its action evaluated, yielding a new current state. If there are no rules whose conditions are true, the execution halts. Although the action may be a compound statement consisting of a sequence of smaller statements, conditionals, and loops, it is executed atomically—no other rule can be executed before the action completes.

When several rule conditions are true at the same time, a choice is made arbitrarily, resulting in several possible executions. The  $\text{Mur}\varphi$  verifier tries them exhaustively by depth-first or breadth-first search.

One essential construct in  $Mur\varphi$  is the *ruleset*, which is used to describe a collection of rules that vary over a parameter. A ruleset can be thought of as nondeterministically selecting a value for the parameter from a set.

Several types of errors can be detected in a  $Mur\varphi$  description. There is an error statement that can appear in an action. Invariant Boolean expressions may also be specified; if the invariant is false in any reachable state, an error is reported. The system can detect deadlock states, which are states that have no other states as successors. Finally,  $Mur\varphi$  can check many common liveness and fairness properties using a subset of linear-time temporal logic.

If a problem of any type is detected, the verifier prints out a diagnostic trace, which is a sequence of states that leads to a state exhibiting the problem. In addition to the error traces, it is possible to print out the values of specified variables using put commands. This capability is used to obtain all the possible results of test programs.

#### 2.4.2 RMO description in $Mur\varphi$

The executable specification follows the intuition of Figure 2.1. It describes reordering boxes, global memory with a nondeterministic switch, and necessary part of processors. There are shared variables for all of the state of the system, including the processor registers, the memory, and the contents of the reorder boxes. Here, we provide excerpts from the description.

#### State of the model

In the first part of Figure 2.2, constants are declared for the number of processors, size of memory, number of registers, size of reorder boxes, and so on. These constants are the only declarations needed to be changed to have a larger or smaller-sized system, since the description is scalable. For verification, these constants should be kept very small in order to bound the size of the state space that must be explored by the verifier. Constants such as A, B, r1, etc. are used to represent memory addresses and registers in the program symbolically.

Types are declared using those constants. For example, Processor is declared to be a subrange of integers, which are used as identifiers for processors. Instruction is an enumeration, which may include all kinds of instructions used in the program being modeled. IssueIndex is a pointer to an instruction in a reorder box and ReorderBoxType is a record representing a reorder box of each processor. It consists of a counter and an array of instruction records. The counter holds the number of instruction records in the reorder box. Each instruction record contains all the information of an instruction: the instruction type, memory address operand, register operand, constant operand, and so on.

Global states of the executable model are represented by a set of state variables shown in Figure 2.3. The first variable, Memory, models the global memory by an array of Value indexed by Address type. The control state in a processor is modeled using global variables: program counter PC and nPC (next PC), and condition code register CCR. The use of the program counters will be explained in the next section.

```

Const

ProcessorNum : 3;

AddressNum : 3;

RegisterNum : 3;

TempNum

: 6;

ValueNum

: 5;

MaxPC

: 10;

ReorderBoxSize : 6;

A : 1;

B : 1;

r1: 1;

-- other constants are omitted

Type

Processor : 0 .. ProcessorNum - 1 ;

Address : 0 .. AddressNum - 1 ;

TempIndex : 0 .. TempNum - 1; -- for register renaming

Value : 0 .. ValueNum - 1; -- range of data

Instruction: Enum{Iload, Istore, Ildstore, Iswap, Imov, Icmp, Itst, Imembar,

IbeY, IbeN, IbneY, IbneN }; -- other instructions are omitted

: 0 .. MaxPC ;

IssueIndex : 0 .. ReorderBoxSize - 1 ;

ReorderBoxType : Record

Count : 0 .. ReorderBoxSize; -- number of instructions in the box

: Array[IssueIndex] of

Record Instr : Instruction;

Addr : Address;

Temp : TempIndex; -- and so on

MemBit: Array [Enum{ b0, b1, b2, b3 }] of Boolean;

-- used for membar instructions

End;

End;

-- other types are omitted

```

Figure 2.2: Constant and type declarations for the executable memory model in Mur $\varphi$

```

Var

: Array [Address] of Value;

Memory

: Array [Processor] of Label;

: Array [Processor] of Label;

-- for anulled branch

nPC

: Array [Processor] of Boolean; -- condition code register

CCR

Registers : Array [Processor] of Array [Register] of TempIndex;

: Array [Processor] of Array [TempIndex] of Value;

ReorderBox: Array [Processor] of ReorderBoxType;

-- for speculation branch

: Array [Processor] of Label;

memPC

memnPC

: Array [Processor] of Label;

: Array [Processor] of Array[Register] of TempIndex;

memReg

```

Figure 2.3: State variable declarations for the executable memory model in  $Mur\varphi$

This description is based on a register renaming scheme, so registers are a perprocessor array of temporary indices, which are pointers to temporaries in a register pool, and Temps are real locations where the values for registers are kept.

The reorder boxes are represented as an array ReorderBox of ReorderBoxType indexed by Processor. A reorder box queues up every instruction from its processor in program order.

The description also implements speculation on branches. The states of PCs and registers are saved in memPC and memReg at the time of issue of a speculative branch; these are used to restore the PCs and registers in case the speculation turns out to be incorrect.

#### Procedures

There are individual processes for the processors in Figure 2.1 and for the memory. Only one process may execute at a time. The processes modeling the processors issue individual instructions by inserting them at the tail of a reorder box queue, so that instructions in a reorder box are always in program order.

For each class of instruction, there is a procedure in the Mur $\varphi$  description that issues the instruction by inserting it in the reorder box. For example, Load\_init() in Figure 2.4 inserts a load instruction with its operands after all previously-issued

```

Procedure Load_init(p:Processor; a:Address; r:Register);

Begin

PutInBox(p, Iload, a, GetTemp(p,r));

PC[p] := nPC[p]; nPC[p] := nPC[p] + 1;

End;

Procedure Store_init(p:Processor; r:Register; a:Address);

Begin

PutInBox(p, Istore, a, Registers[p][r]);

PC[p] := nPC[p]; nPC[p] := nPC[p] + 1;

End;

```

Figure 2.4: Procedure 'Load\_init' and 'Store\_init'

instructions in the reorder box. This issuing procedure also handles register renaming, so that the instructions in the reorder box refer to temporary registers, not to register names. The function GetTemp(p,r) returns a new temporary location for register r in processor p. Procedure PutInBox() puts the instruction into a reorder box by copying it at the tail of instruction queue of the reorder box. Finally, the next PC value is copied to the current PC, then incremented.

Procedures for other instructions simply copy the instruction into reorder boxes. When a store instruction is issued, the procedure Store\_init() puts its arguments into the corresponding reorder box. When a branch instruction is issued, it is performed immediately if the CCR is already set by a test. Otherwise, a nondeterministic prediction of the branch direction is made. The branch is then issued based on this prediction. There are two issuing procedures for each branch instruction: e.g., BeY\_init() and BeN\_init() for be instruction ("branch on equal").

There is also a procedure to perform each class of instruction type. These procedures are executed by the global memory, and do all of the work of the instructions. For instance, the procedure Store\_perf() in Figure 2.5 performs a store instruction by writing the contents of the register (assigned temporary) into the memory location.

Performing a load is more involved because the value axiom should be satisfied determining the value to be loaded. The procedure Load\_perf() shown in Figure 2.5 is executed when a load is performed to read the specified memory address.

```

Procedure Store_perf(p:Processor; t: TempIndex; a:Address);

Begin Memory[a] := Temps[p][t]; End;

Procedure Load_perf(p:Processor; i:IssueIndex; a:Address; t:TempIndex);

-- Read the most recent value of address A from the view of processor[p].

Temps[p][t] := Memory[a];

For j:IssueIndex Do

Alias J:ReorderBox[p].Ar[j] do

If ( j<i & J.Addr = a ) Then

-- if there is a store preceding in program order but not performed,

-- then get the value being stored.

If ( J.Instr = Istore | J.Instr = Iswap )

Then Temps[p][t] := Temps[p][J.Temp];

Elsif ( J.Instr=Ildstore ) Then Temps[p][t] := 1; End; --If

End; --If

End; --Alias

End; --For

End;

```

Figure 2.5: Procedure 'Load\_perf' and 'Store\_perf'

If the prediction on a branch turns out to be incorrect when the branch instruction is performed, the state of the registers and program counter is restored to what it was when the branch was issued, and the speculative instructions are canceled. Since the logical specification allows speculative execution and ignores anti-dependences from register usage, it is necessary to include speculative execution to ensure that the executable specification generates every legal program result.

#### **Functions**

The description attempts to provide the most direct possible translation from the ordering rules given in the logical description. We write functions for the low-level predicates that it uses. Functions Is\_load(p,i) and Is\_store(p,i) check whether the instruction at position i in the reorder box for processor p is a load or a store instruction. Similarly, Is\_branch and Is\_CCR check whether the instruction is a branch or a test that writes a CCR.

The function Membared(p,i,j) is shown in Figure 2.6. It returns a Boolean formula which is true if and only if the two memory instructions at entry i and j are ordered through a membar. Each or'ed expression checks if there is a memory barrier of the corresponding type in between the two instructions. The Alias command is used to define an abbreviation.

```

Function Membared(p:Processor; i,j:IssueIndex):Boolean;

Alias R:ReorderBox[p] do

Return

(Is_load(p,i) & Is_load(p,j) &

Exists k:IssueIndex do -- bit:b0 corresponds to the type of {L<L}

i<k & k<j & R.Ar[k].Instr = Imembar & R.Ar[k].MemBit[b0] end)

(Is_store(p,i) & Is_load(p,j) &

Exists k:IssueIndex do -- bit:b1 corresponds to the type of {S<L}

i<k & k<j & R.Ar[k].Instr = Imembar & R.Ar[k].MemBit[b1] end)

(Is_load(p,i) & Is_store(p,j) &

Exists k:IssueIndex do

-- bit:b2 corresponds to the type of {L<S}</p>

i<k & k<j & R.Ar[k].Instr = Imembar & R.Ar[k].MemBit[b2] end)

(Is_store(p,i) & Is_store(p,j) &

Exists k:IssueIndex do -- bit:b3 corresponds to the type of {S<S}

i<k & k<j & R.Ar[k].Instr = Imembar & R.Ar[k].MemBit[b3] end);

End:

End:

```

Figure 2.6: Function 'Membared'

In order to define function  $\mathtt{Depend}()$ , we first define function  $\mathtt{Direct\_Depend}()$  in Figure 2.7. This function checks whether two instructions are dependence ordered, as define in Section 2.3. At first, it ensures the instruction at i precedes the one at j in program order  $(X <_p Y)$ . The rest of the Boolean expressions correspond to the rules (d1) through (d3). The first or'ed expression translates the rule (d1). The next expression for the rule (d2) calls  $\mathtt{Reg\_Depend}()$ , which returns true if the preceding instruction is writing the same register that is read by the following instruction—strictly speaking, the same temporary location in the register renaming scheme. The dependence through the condition code register is checked separately. The last part

of the Boolean expression directly translates the rule (d3).

```

Function Direct_Depend (p:Processor; i,j:IssueIndex):Boolean;

Begin

Return ( i < j ) &</pre>

( Is_branch(p,i) & Is_store(p,j) )

| ( Reg_Depend(p,i,j) | ( Is_CCR(p,i) & Is_branch(p,j) ) )

| (Is_store(p,i) \& Is_load(p,j) \& mAddress(p,i) = mAddress(p,j) );

End;

Function Reg_Depend ( p:Processor; i,j:IssueIndex):Boolean;

-- Return true if instruction at 'i' writes a register read by the one at 'j'.

Function Depend (p:Processor; i,j:IssueIndex):Boolean;

-- Instructions at 'i' and 'j' are dependent through transitivity?

If ( i >= j ) Then Return false;

Elsif Direct_Depend(p,i,j) Then Return true;

Exists k:IssueIndex Do

(i < k) & (k < j) & Depend(p,i,k) & Depend(p,k,j)

End -- Exists

Then Return true;

Else Return false;

End: --If

End;

```

Figure 2.7: Function 'Direct\_Depend' and 'Depend'

Dependence order is the transitive closure of Direct\_Depend(). The function Depend(p,i,j) in Figure 2.7 computes this using the function Direct\_Depend() and calling itself recursively. It returns true if and only if the instructions at i and j in reorder box p are dependence ordered, by checking if there exists an instruction in-between i and j through which the dependence order is transitive.

#### Rules

There are two collections of  $Mur\varphi$  rules which implement the diagram in Figure 2.1. The first collection of rules describes the behavior of the model that *issues* instructions into reorder boxes. The other collection of rules *performs* the instruction in the reorder boxes. We will postpone the explanation of the first kind of rules to the next section. Here, we show the latter kind of  $Mur\varphi$  rules implementing the memory order.

The global memory process nondeterministically selects a processor and an instruction in the processor, which is executed if it is legal to do so. The ordering rules are enforced by the conditions of  $Mur\varphi$  rules that decide whether an instruction is legal to perform. An instruction is legal to perform if and only if the ordering rules allow the existence of a memory order in which the instruction can be the minimum under a memory order of all the instructions currently in the reorder box. Each ordering rule from the logical description is translated as directly as possible to a  $Mur\varphi$  function, which checks whether the ordering rule is satisfied.

When an instruction can legally be performed, the memory performs it. This involves doing all of the computation associated with the instruction, including ALU operations and updating registers and/or memory. Then it is removed from the reorder box.

In essence, a particular memory order is gradually constructed as the specification executes. The instructions that have been performed are memory ordered and those remaining in the reorder boxes have not yet been ordered. The constraints on nondeterministic choices involved in selecting the next instruction ensure that every legal memory order can be generated.

The rule for the memory order constraints is in Figure 2.8. This rule can also be thought of as implementing the behavior of the memory. The rule is embedded in parameterized rulesets that nondeterministically choose a reorder box and an instruction index. It performs the instruction at that reorder box index only if that instruction is allowed to appear first among all the instructions in the reorder box, according to the memory ordering rules.

The condition of the rule is a conjunction of several Boolean expressions. The first and'ed expression ensures that the chosen index i of the reorder box p is not an empty slot. The second expression requires every membar instruction to remain in the reorder box until all the previous instructions are executed and removed from the box.

```

Ruleset p:Processor Do

Ruleset i: IssueIndex Do

-- For all instructions, ReorderBox[p].Ar[i], check this.

Alias R : ReorderBox[p];

op : R.Ar[i].Instr Do

Rule "Execute one of the instructions in minimal set"

( i < R.Count ) -- instruction at i is valid one

& (op=Imembar -> i=0) -- the membar no longer needs to be here

& -- Rule (m1)

( Forall j:IssueIndex Do

j<i -> ! ( Depend(p,j,i) & Is_wr_reg(p,j) )

EndForall )

& -- Rule (m2)

( Forall j:IssueIndex Do

j<i -> ! Membared(p,j,i)

EndForall )

& -- Rule (m3)

( Is_store(p,i) -> Forall j:IssueIndex Do

! ( j<i & ( Is_store(p,j) | Is_load(p,j) )

& mAddress(p,j) = mAddress(p,i) )

EndForall )

==>

Begin

-- The chosen instruction ReorderBox[p].Ar[i] is allowed to be performed.

Switch op