## Analysis and Synthesis of Concurrent Digital Grouits Using Control-Flow Expressions

Claudionor Nunes Coel ho Jr<sup>\*</sup> Gi ovanni De Miche<sup>†</sup>

\* Departamento de Ciênci a da Computação, ICEx/UFMG, Belo Horizonte, MG, Brazil \*\* Computer Systems Laboratory, Stanford University, Stanford, CA 94305-9030

#### Abstract

We present in this paper a novel *modeling style* and *catrd sythesis* technique for systemlevel specifications that are better described as a set of concurrent descriptions, their synchronizations and constraints. The proposed synthesis procedure considers the degrees of freedomintroduced by the concurrent models and by the environment in order to satisfy the design constraints.

Synthesis is divided in two phases. In the first phase, the original specification is translated into an algebraic system, for which complex control-flow constraints and quantifiers of the design are introduced. In the second phase, we translate the algebraic formulation into a finite-state representation, and we derive an optimal control-unit implementation for each individual concurrent part. In the implementation of the controllers from the finite-state representation, we use flexible objective functions, which allows designers to better control the goals of the synthesis tool, and thus incorporate as much as possible their knowledge about the environment and the design.

## 1 Introduction

The use of synthesis tools has gained great acceptance in industry. Three of the reasons for its success are the increasing complexity of the circuits, the need for reducing time to market and the need to design circuits optimally. In order to meet the tight requirements of today's marketplace, designers have to rely on the specification at higher levels of abstraction, and in particular, rely on models that describe the specification at a level higher than logic level and register-transfer level (RTL) [28].

In these designs specified at higher levels, the system to be synthesized is usually modeled as a set of sequential components consisting of operations and their dependencies, e.g., as in the case of a dataflow. We call *process* each sequential component. Processes have been successfully synthesized at chip-level by experimental and/or commercial high-level synthesis tools. The synthesis task in these tools involved the scheduling of operations over a discrete time and the binding of these operations to components.

This paper considers systems that are better described as a set of synchronous concurrent processes and their synchronization, which we call here a *multi-process* or *systeml evel* design. Although it has been attempted to use high-level synthesis tools to synthesize multi-process descriptions, these techniques are usually not well suited for system-level designs for three reasons. First, nost high-level synthesis tools synthesize one process at a time, thus not considering some degrees of freedomin the optimization. Second, the model used for specifying and handling the interface in most high-level synthesis is very simple, and does not easily support modifications. Finally, standard cost functions used in high-level synthesis are simple, i.e., the goal of the synthesis tool is usually the minimization of area or delay. In system-level designs, we may have to quantify not only area and delay, but more complex cost measures, such as bus or microprocessor utilization.

The use of single process techniques in the synthesis of multi-process descriptions imposes severe limitations on the implementations; in some cases it even prevents valid implementations frombeing found. Multi-process descriptions require the use of more complex algorithms and techniques other than the ones used for single process synthesis. These complex techniques involve the utilization of the degrees of freedomof the other processes during the synthesis of a single process, the use of synchronization among processes to further optimize the synthesis tasks, the modification of the control-flow over time, as required by the specification, and the selection of the different goals of the synthesis tools.

Milti-process descriptions also require specifications of complex constraints. For example, when synthesizing single process models, the tool does not have to consider the synchronization among concurrent descriptions. However, when synthesizing multi-process descriptions, the interrelations among different processes must be considered. In addition, interrelations of the different parts in an interface does not need to be static. For example, a synchronous RAMhas different requirements in terms of cycles for the different modes of operation. The ability of adding complex timing constraints results in a greater flexibility with respect to a specification.

## 1.1 Research Objective

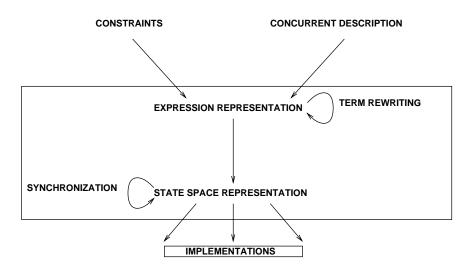

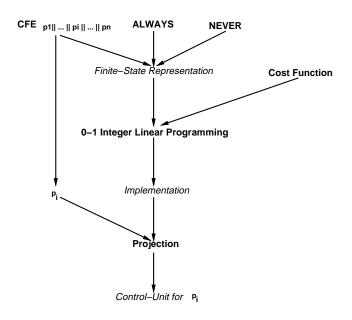

In this paper, we present a formal model to analyze control-flow intensive synchronous system level specifications (operating under a single clock), and a methodology to synthesize control-units for the concurrent parts of the design. In this methodology, the control-flow of the description is first abstracted into an algebraic system, here called *control-flow expressions*, manipulated, and then translated into its state space, where the control-unit is synthesized. Our technique also extends previous synthesis approaches because it considers processes with arbitrary control-flow. We emphasize that our systemutilizes both representations, during synthesis, i.e., an algebraic representation and a state space representation, and that these two representations are necessary for the efficient manipulation of the specification for different types of transformations. Figure 1 presents a pictorial view of our

Figure 1: Design flow for synthesizing multi-process descriptions

design flow. We assume that the design is originally specified by some hardware description language (HDL), such as VHL, Verilog HDL or HardwareC, and compiled into some control-dataflowgraph (CDFG) model. We assume that the compilation from the HDL into the CDFG model is a direct mapping, and that control-flow expressions can be obtained from the CDFG through abstraction. So in all examples in this paper, we will use the original HDL specification instead of the CDFG representation. It should be emphasized here that we focus neither on a specific CDFG model nor on an HDL language representation, but on a modeling style for concurrent synchronous systems and a synthesis technique for their control lers.

The constraints of the systemare nanually entered in the tool fromsome constraint language that includes synchronization, timing and binding constraints. For example, the specification of synchronization constraints is already present in the Esterel [2] language. The HardwareClanguage allows the specification of timing and binding constraints that are used by the synthesis tool. These constraints will guide the synthesis tool during the synthesis of the control-unit implementations.

In the next section, we present some examples of where our formulation can be used and how those problems can be solved. In the following section, we define the algebra of *control-flow expressions*, its axions, the representation of the design space, and a comparison with existing formalisms. In Section 4, we show how constraints can be represented in *control-flow expressions*, and how we restrict the solution space with respect to the constraints. In Section 5, we show how the algebra of control-flow expressions can be transformed into a finite-state representation. In Section 6, we present our synthesis method using an 0-1 integer linear programming specification with Bool ean constraints. In Section 7, we present some applications of this methodol ogy with implementation results, followed by some conclusions.

## 2 Motivation

This section presents examples of real designs that either cannot be synthesized or are synthesized sub-optimally by usual high-level synthesis tools. We show intuitively that optimal and valid implementations can be obtained only if synchronization, dynamic binding and dynamic scheduling are considered during the design space exploration. Then, in the rest of the paper, we present formal methods to obtain optimal solutions to these synthesis problems.

One of the major problems of using current high-level synthesis tools to synthesize system level designs is that the synthesis tool must consider how the environment affects the whole system. Since the specification of the environment in which the circuit is going to execute is generally a formidable task, the user must have a better control over the synthesis tool in order obtain optimal results. The user can interact with our synthesis tool by specifying complex constraints and flexible cost functions. The necessity of this interaction will become apparent in the next examples.

## 2.1 Synchronization Synthesis and Dynamic Binding

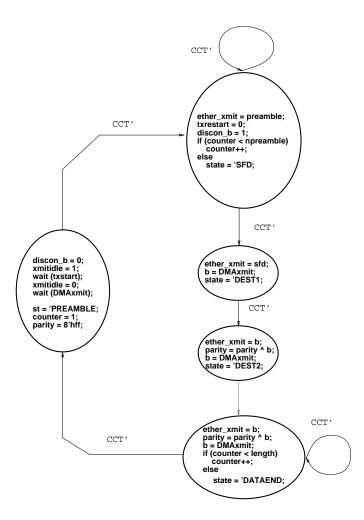

#### 2.1.1 Ethernet Co-processor

In this example, we show how we can synchronize multiple processes to share the same critical resource. This synchronization is synthesized by considering the degrees of freedom anong the different processes that share the critical resource. Dynamic binding is achieved by allowing several processes to instantiate the same resource at different times. In this example, a constraint that crosses process boundaries exists, i.e., the critical resource should not be used by more than one process at a time.

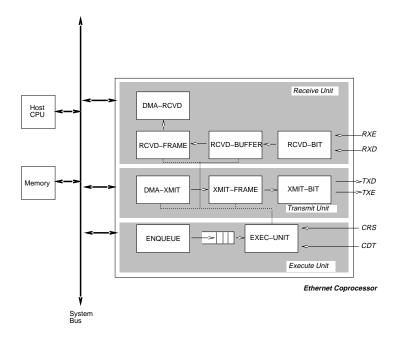

The block diagram of Figure 2 is the block diagram of an ethernet coprocessor. This coprocessor contains three units: an execution unit, a reception unit and a transmission unit. These three units are modeled by thirteen concurrent processes, with three processes accessing the bus: *DMAxmit*, *DMrcvd*, and *enqueue*. The problem we want to solve is the synthesis of the synchronization among the three processes such that any bus access for the three processes is free of conflicts. Note that the differulty in solving this problem comes from the transfers that are non-deterministic over time, i.e., *we do not know a priori when each process accesses the bus*, since this operation is control dependent. Also, the transfers of different processes are uncorrelated, i.e. knowing that one process accesses the bus at a specific time does not imply the transfers in other processes are known.

This problem has been solved for the simplified assumption that the processes are dataflows executing at the same rate [20]. Note that in the problem described here, however, we do not know when each bus access will take place, since there may be loops and conditionals in the specification that will make the bus accesses execute at different rates. Thus, the approach described in [20] cannot be used. File et al. [13] addressed the problem of rescheduling transfers inside a single loop or conditional to reduce the number of synchronizations among processes. This method is restrictive because all transfers that are optimized must be en-

Figure 2: Ethernet coprocessor

closed in the same loop or conditional, and only the synchronization due to the transfers is considered during the simplification. A synchronization is eliminated if there are two transfers that are executed sequentially or in parallel and the synchronization of the first one is correlated to the second transfer. As we are going to show later, our formalismallows processes to be specified by their control-flow with an abstraction on the dataflow parts, and thus will subsume the solutions found by both of these procedures. Also, our formalism achieves the simplification of synchronization that crosses loops and conditionals, and we do not restrict this simplification to only correlated transfers in the specification.

Let us first consider an abstraction of the original specification that captures only the bus accesses. Furthermore, in order to be able to discuss this problem throughout this paper, we will assume a set of reduced behaviors for *DMarcvd*, *DMarnit* and *enqueue* such that the resulting behavior is small enough that can be easily understood. Figure 3 presents the behaviors we assume for these descriptions in this paper, in a pseudo-Verilog code. In this figure, the constructs that do not belong to the language, such as write bus, are represented in typewriter style; reserved words of Verilog are represented in bold; and other legal syntactic constructs are represented in italics.

Note that the processes are control-dominated specifications where the flow of control is modified by some set of wait statements. In this example, also, note that the priority of *enqueue* should be the smallest one, since the execution of the bus access in this process may be delayed. On the other hand, if the bus accesses of the other processes are delayed, the controller will not be able to deliver data at the interface at the proper rate.

| <b>module</b> DMA rcvd;           | malle DMAx mit;           | <b>mdle</b> e nque ue ; |

|-----------------------------------|---------------------------|-------------------------|

| always                            | always                    | alwys                   |

| begin                             | begin                     | begin                   |

| write bus;                        | initialize variables      | wit (free bus);         |

| $data = receive(from_xmit_fram);$ | wit (transmission ready); | read bus;               |

| end                               | read bus;                 | end                     |

| entalle                           | end                       | entmile                 |

|                                   | entatle                   |                         |

Figure 3: Abstracted behaviors for DMArcvd, DMAxmit and enqueue

If we assume that every operation takes one clock cycle, an implementation for the synchronization mechanism of the bus should establish a temporal relation between *enqueue* and the two other processes *DMarnit* and *DMarcud*. This temporal relation should include any data dependent operation of the two other processes, such as the conditional *transmission ready*, and it should also consider when the other processes access the bus. Apossible solution to this problem would be:

```

mile enqueue;

always

begin

wit ( posedge clock);

while (transmission ready)

begin

wit ( posedge clock);

wit ( posedge clock);

wit ( posedge clock);

end

read bus;

end

endmile

```

In this implementation, we have to wait the first cycle because *DMarcvd* is accessing the bus in the first cycle. During the second cycle, *enqueue* will be able to access the bus only if *DMarmit* is not accessing it. In the following cycle, however, *DMarcvd* will be accessing the bus again, and *enqueue* will have to wait for another cycle. We will show later how this controller could be obtained automatically for the process *enqueue*.

#### 21.2 Protocol Conversion

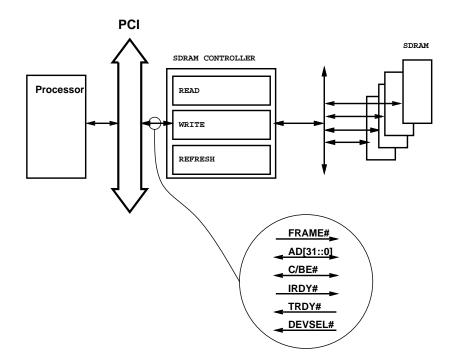

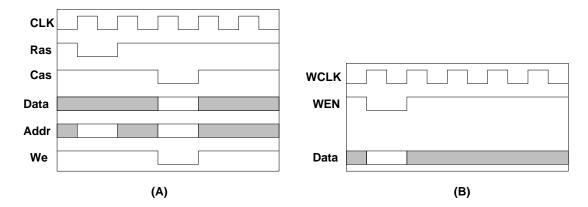

In this section, we showhow can use synchronization synthesis in order to synthesize the controller for converting the PCI bus protocol [35] into a synchronous DRAMprotocol. In particular, we will provide here the conversion between reading and writing cycles of a PCI bus into synchronous DRAMcycles. Figure 4 shows the diagramof computer using a PCI bus, and a synchronous DRAM(SDRAM memory bank. Both protocols can use single or

Figure 4: Protocol conversion for PCI bus computer

burst mode transfers, with the difference that SDRAMA burst mode are limited to at most 8 transfers on the same rowthat are one cycle apart from each other.

Informally, a PCI bus cycle begins with an address phase, followed by one or more data phases. Whit states can be inserted in the data phase by either the microprocessor or by the memory. For burst mode transactions, we assume here a linear increment of the address space.

The synchronous DRAW reading protocol begins by a rowaddress selection (RAS) phase followed by a column address selection (CAS) phase. After the CAS phase, and a fixed number of cycles, the SDRAW will produce data at a rate of one word/cycle.

During the generation of the protocol converter, a control-unit implementation is selected to combine the behaviors of both SDRAM and PCI bus protocols. Implementations satisfying these protocol conversion constraints were obtained in the system described in [4]. In our approach, we will show how such constraints can be combined with timing and resource binding constraints in order to generate optimal controllers.

## 2.2 Dynamic Scheduling

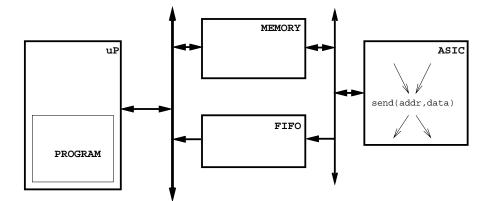

In this example, we showhow can specialize a design by incorporating dynamic scheduling constraints from an interface. Splitting the interface specification from the design specification was addressed in [31, 25, 32, 3]. One of the main advantages of abstracting interface implementation details at the higher levels of abstraction is that more degrees of freedom

Figure 5: Systemarchitecture

can be explored during synthesis.

In such techniques, the transfers among processes are abstracted in terms of communication operations (such as a *send* operation). During synthesis, the best protocol and communication mediumis selected to implement a particular transfer. The selection and synthesis of the protocol interface will impose complex scheduling constraints to the design, as we will see below.

Figure 6: Writing cycles for synchronous DRAM(A) and for synchronous FIFO (B)

Consider a system that has an ASIC and an embedded processor, such as the one given in Figure 5. Assume the ASIC communicates with the microprocessor either through a synchronous memory or through a synchronous FIFO For example, this structure has been used in hardware-software codesign [16, 17]. In this system, the transfers to the memory and to the FIFO are determined at run-time by the proper selection of the address. The interface timing is also determined at run-time, since the timing specifications for these two components are different, as given in Figure 6. In essence, a data transfer may take either one or three cycles to complete. Thus, the timing constraint specification should also reflect the mismatch between the timing of the components. The specification of interface constraints has been used in the past by Nestor [32], Ku [25] and Borriello [3]. They used min/max scheduling constraints to annotate the design specification. The use of these constraints, however, is limited to static constraints. In the example presented above, the specification of the interface requires the design to contain implementation details, which is not desirable for the reasons given previously.

Assuming that the address selection for the memory module is called s, the constraint that we need to specify is a three-cycle operation or a one-cycle operation, depending on s. Thus, the interface can no longer be specified in terms of fixed minimum/maximumdelay between operations, since the execution time of the operation is dependent on the address selection. In order to synthesize the protocol for the *send* operation given above, we must consider a dynamic schedule for this operation.

This can be achieved by using the alternative composition in the constraint specification. For example, one possible representation for this constraint could be:

> synchronize with "send" operation if (s) delay for "send" is 3 cycles dse delay for "send" is 1 cycle

W will show that using the algebra of control-flow expressions, we can represent this constraint as the following compact representation:

$$s: Ras \cdot 0 \cdot \{Cas, data\} + \overline{s}: data$$

where Rus is an abstraction to the RAS cycle of the RAM Gas is an abstraction of the CAS cycle of the RAM 0 is a one-cycle delay operation, data is an abstraction of the data transfer, and  $\overline{s}$  means that s is false.

During the synthesis procedure, the *send* operation is bound to an implementation that observes this constraint. In this case, the implementation is exactly the control that waits either one or three cycles, depending on s.

In this example, the two different communications mechanisms assume different possible behaviors for the environment. Depending on how the environment requires data, one mode should be highlighted over the other for some transfer by the proper selection of an objective function.

## 3 Control-Flow Expressions

This section presents the definition of the algebra of *control-flow expressions*, which is a formal model for representing the control-flow in systemal evel designs. As the name suggests, *control-flow expressions* are used for the analysis of the control-flow of the design, by abstracting away the dataflow details.

## 3.1 Abstraction from the Original Specification

We consider in this paper systemal evel designs that will be synthesized as synchronous circuits running under the same clock. In the synthesis of these designs, we need to represent the interactions among the concurrent parts, which can be best model ed at the control-flow level.

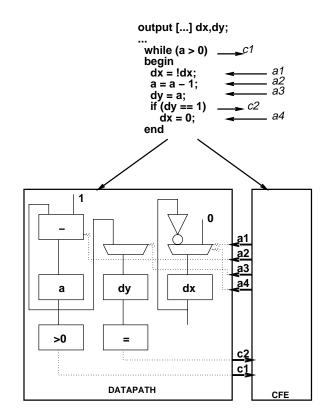

W assume in our computation model that the specification will be partitioned in terms of a control-flow and a dataflow, as described in [10, 28, 47]. In this model, variables, their operations and operands are placed in the dataflow, and the language constructs of the specification language are placed in the control-flow. In addition, we assume that any I/O operation between a process and the process external environment will be placed in the dataflow.

In this model, the control-flow and dataflow will communicate through events. The control-flow will generate output events to the dataflow that will sensitize the execution of operations in the dataflow. The dataflow will generate input events to the control-flow that will trigger the different execution paths.

Figure 7: Partitioning of specification into control-flow/dataflow

**Example 1** In Figure 7, we showhow the control - flow portion of a description can be abstracted in terms of the events it generates. The control - flow of the specification generates output events  $a_1, a_2, a_3$  and  $a_4$ . Event  $a_1$ , for example, triggers the execution of the path in the control - flow that

will complement dx. We represent the dataflow by an implementation in terms of a datapath for illustrative purposes only. In general, we do not assume any particular dataflow implementation, since control-flow will be able to encode several possible datapath implementations.

The datapath of Figure 7 generates input events and  $c_2$  that will trigger the execution of the loop and the execution of the alternative path, respectively.

The reader should note that the control-flow does not make any assumptions on the possible values of its input events over time. In this example, we assume that entering the loop (when even  $c_1$  is generated) and exiting the loop are equally probable.  $\Box$

#### 3.2 Algebra of Control-Flow Expressions

The algebra of control-flow expressions is defined by the abstraction of the specification in terms of the sensitization of paths in the dataflow, and by the compositions that are used anong these operations. As presented in the previous section, we view the communication between the dataflow and control-flow as an event generation/consumption process. More formally, we call the output events generated from the control-flow *actions* (from some alphabet  $\mathcal{A}$ ). We assume that each action will execute in one-unit of time (or cycle). If an operation executes in multiple cycles, they will be handled by a composition of single-cycle actions.

**Earple 2** W abstract the computation x = y \* z of some HDL by action a, which then substitutes all occurrences of this computation in the specification.  $\Box$

W represent the input events of a control-flow by *conditionals*, which are symbols from an alphabet C. The conditionals in a control-flow expression will enable different blocks of the specification to execute. Guards will be defined as the set of the Bool ean formulas over the set of conditionals.

**Definition 3.1** A guard is a Bool ean formula on the alphabet of conditionals. We will use  $\mathcal{G}$  to denote the set of guards over conditionals.

We assume that each guard and conditional is evaluated in zero time. At the end of this section, we compare the assumptions on the execution time of actions, conditionals and guards with the synchrony hypothesis.

**Example 3** In the specification if  $(x \ge y)$  x = y \* z, a conditional c abstracts the binary relational computation  $x \ge y$ . If at some instant of time, the *guardc* is *true*, x = y \* z is executed. If at some instant of time, the *guard* $\neg c$  is *true*, the else branch (which is null in this case) is executed.  $\Box$

As discussed in the introduction, we assume systems modeled by a set of operations, dependencies, concurrency and synchronization. We encapsulate sub-behaviors of this system in terms of processes, which are represented by control-flow expressions and correspond to an HL model. In our representation, each process has a label from some alphabet  $\mathcal{F}$  to control-flow expressions.

We define the set  $\Sigma$  as the alphabet of actions, conditionals and processes  $\Sigma = \mathcal{AUCF}$ .

The compositions that are defined in the algebra of control-flow expressions are the compositions supported by existing HDs. Vérilog HDL, for example, supports sequential composition, alternative composition, loops, forks and unconditional repetition. The same set of compositions is also supported in VHDL and HardwareC, and thus is supported by control-flow expressions. Since alternative compositions and loops in these languages are guarded, their corresponding compositions in CFEs will also be guarded.

We define the set  $\mathcal{O} = \{sequential(\cdot), alternative(+), guard(:), loop(*), infinite(\omega), parallel(||)\}$  as being the valid compositions of control-flow expressions. The formal definition of the algebra of control-flow expressions is presented below.

**Defition 3.2** Let  $(\Sigma, \mathcal{O}\delta, \epsilon)$  be the algebra of control-flow expressions where:

$\Sigma$  is an alphabet that is subdivided into the alphabet of actions, conditionals and processes;

Ois the set of composition operators that define sequential, alternative, guard, loop, infinite and parallel behavior;

$\delta$  is the identity operator for alternative composition;

$\epsilon$  is the identity operator for sequential composition.

For the sake of simplicity, we restrict the sets of behaviors definable in control-flow expressions in the following way: it should always be possible to obtain a control-flow expression without any process variables. In this sense, the set of process variables have the same cardinality as the set of control-flow expressions without process variables. In this paper, whenever we refer to a GE p, we are referring to the GFE defined by the process variable p.

W consider a special action called 0, which corresponds to a no-operation or abstraction of the computation. Action 0 executes in one unit-delay (just as any other action), but it corresponds either to an unobservable operation of a process with no side effects or to a unit-delay between two computations.

W introduced in Definition 3.2 the symbol  $\delta$  that is called here *deadlock*<sup>-1</sup>. The symbol  $\delta$  is defined as  $\delta \triangleq false : p$ , where p is any control-flow expression. The deadlock symbol is an identity for alternative composition. This means that the branch of the alternative composition represented by the deadlock is never reachable. Later we show that these branches can in fact be removed.

<sup>&</sup>lt;sup>1</sup>Deadlock was the name given to  $\delta$  in process algebras. In synthesis,  $\delta$  denotes code that is unreachable due to synchronization. Since its properties are the same as the properties for deadlock in process algebras, we used the latter name, for the sake of uniformity.

| Composi ti on | HL Representation                                                     | CF Expression            |

|---------------|-----------------------------------------------------------------------|--------------------------|

| Sequentid     | <b>begin</b> $p; q$ end                                               | p.q                      |

| Padld         | fork $p; q$ join                                                      | p   q                    |

| Alterative    | if (c)<br>p;<br>else                                                  | $c: p + \overline{c}: q$ |

|               | q;                                                                    |                          |

| Lap           | $ \begin{array}{c} \mathbf{while}\left( c \right) \\ p \end{array}; $ | $(c : p^*)$              |

|               | vait(!c)<br>p;                                                        | (c : 0). p               |

| Infinite      | al ways p;                                                            | $p^{\omega}$             |

Figure 8: Link between Verilog HDL constructs and control-flow expressions

We also introduced the symbol  $\epsilon$ , which is called here the *null computation*. The *null computation* symbol is defined as a computation that takes zero time. For example, this symbol can be used to denote an empty branch of a conditional. This symbol behaves as the identity symbol for sequential composition.

The semantics of the major control-flow constructs in HL are related to control-flow expressions in the table in the Figure 8, where p and q are processes  $(p, q \in \mathcal{F})$  and c is a conditional  $(c \in \mathcal{C})$ . In this figure, we relate GE to the control-flow structure of Vérilog HL [41]. In this paper, we assume that guards (:) have precedence over all other composition operators; loops and infinite composition  $(*, \omega)$  have precedence over the remaining compositions; sequential composition  $(\cdot)$  has precedence over alternative and parallel composition; alternative composition (+) has precedence over the parallel composition. In addition, we use parentheses to overrule this precedence and for ease of understanding. Although it is not necessary, we will at times replace parentheses by square brackets for clarity.

Informally, we define the behavior of the compositional operators of CFEs as follows: the sequential composition of two processes p and q means that q is executed only after p is executed. The parallel composition means that both p and q begins execution at the same time, and any operation following p||q will begin execution when both p and q have completed. Note that the parallel composition does not assume that p and q must terminate at the same time. The alternative composition means that a deterministic choice is first made with respect to c and  $\neg c$  to decide whether the CFE p or q is executed, respectively. The loop composition means that p is executed while the guard c is *true*. The infinite composition means that p is executed infinitely many times upon reset. Note that in our definition of the syntax of CFEs, every loop and every alternative branch is guarded by ":", which makes the different branches of alternative and loops distinct. This restricts the specification of loop bodies and alternative branches to only accept deterministic choices with respect to the guards.

W will use the following shorthand notation for control-flow expressions. The control-flow expression  $p^{n}$  will denote n instances of p composed sequentially  $(p \cdot \ldots \cdot p)$ , which

corresponds, for example, to a counting loop that repeats n times in some HL. The controlflow expression  $(x : p)^{\leq n}$  will denote a control-flow expression in which at most n-1 repetitions of p may occur. This CFE is equivalent to  $(x : p + \overline{x} : \epsilon)^{p-1}$ .

In our original specification, we assumed that every action in  $\mathcal{A}$  takes a unit-time delay in CFEs, and that every guard takes zero time delay. Then, we could possibly design a system where after choosing a particular branch of an alternative composition (e.g., after choosing c is *true* in  $c : p + \overline{c} : q$ ) and executing the first action of process p, the execution of this action would make  $\overline{c}$  true and thus also enabling the execution of q. In order to avoid this erroneous behavior, we adopt a weaker version of the synchrony hypothesis [5].

Assumption 31 Let p be a process and c be a guard that guards the execution of p (defined as c: p). Any action of p is assumed to execute after c has been evaluated to true. In order words, c: p can be viewed as  $(c: \epsilon) \cdot p$ . First, the conditional is evaluated to true, then the process p that is guarded by c is executed, and other assignments to c will possibly affect future choices only.

#### 3.3 Axions of CFEs

In this section, we present the axions for the algebra of control-flow expressions. These axions provide the theoretical background that will be used to build the finite-state machine representation for control-flow expressions in Section 5.

The algebra of control-flow expressions inherits its formalism from a subset of process algebras [1] that is suitable for describing synchronous systems, called the *algebra of regular synchronous processes*. We further extend this algebra by specifying Boolean variables as guards of processes. The following proposition holds for CFEs:

#### **Fquosition 31** (*TEs are a subset of regular synchronous process al gebras.*

In Table 1, we present the axiom of control-flow expressions that are derived from the axioms of the algebra of synchronous processes, where  $a, b \in \mathcal{M}$  <sup> $\mathcal{A}$ </sup> (the set of multisets of actions),  $p, q, r \in \mathcal{F}(\text{processes})$  and  $c_1, c_2, c_3 \in \mathcal{G}(\text{guards})$ .

The alternative composition has  $\delta$  as its identity component. It is commutative, and associates to the right or left. The sequential composition has  $\epsilon$  as its identity component. It associates to both the right and left, and it is only distributive to the left with respect to the alternative composition. This implies that  $p \cdot (c_1 : r + c_2 : s) \neq c_1 : p \cdot r + c_2 : p \cdot s$ . The intuitive meaning for  $p \cdot (c_1 : r + c_2 : s)$  being different from  $c_1 : p \cdot r + c_2 : p \cdot s$  is that we

$c_1: p + c_2: q = c_2: q + c_1: p$  $(+is \ commutative)$  $(c_1: p + c_2: q) + c_3: r = c_1: p + (c_2: q + c_3: r)$  (+ is associative)  $= c_1 : p + c_2 : q + c_3 : r$  $(c_1: p + c_2: q) \cdot r = c_1: p \cdot r + c_2: q \cdot r$  $(\cdot \text{ distributes to the left with } +)$  $(p \cdot q) \cdot r = p \cdot (q \cdot r)$  $(\cdot is associative)$  $= p \cdot q \cdot r$  $(+is \ i \ dempot \ ent)$  $c_1: p + c_1: p = c_1: p$ 1: p = p $0: p = \delta$  $c_1: p + \delta = c_1: p$ ( $\delta$  is the identity element for +)  $\delta \cdot p = \delta$ ( $\delta$  is the zero element for  $\cdot$ ) ( $\epsilon$  is the identity element for  $\cdot$ )  $p \cdot \epsilon = p$  $\epsilon \cdot p = p$  $c_1: c_2: p = (c_1 \wedge c_2): p$  $a||b = (a \cup b)$ if  $a \cup b$  synchronize  $a||b| = \delta$ if  $a \cup b$  does not synchronize a||b = b||aa||0 = a $a||\epsilon = a$  $a \cdot p || b \cdot q = (a || b) \cdot (p || q)$  $a \cdot p || b = (a || b) \cdot p$  $(c_1: p + c_2: q) ||r| = c_1: (p||r) + c_2: (q||r)$

Table 1: Axions of control-flowexpressions

abstracted away the computation of  $p, c_{-1}$  and  $c_{2}$ , and thus we cannot answer the question on whether action p affects the choice of  $c_{-1}$  or  $c_{2}$ , or if the environment needs some value from pfor making a decision on whether  $c_{-1}$  or  $c_{2}$  should be true. If we assumed this transformation were valid, we could make the decision for all branches of the specification upon start by propagating the guards towards the beginning.

On the other hand, if we assumed that  $p \cdot (c_1 : r + c_2 : s)$  were equivalent to  $p \cdot c_1 : r + p \cdot c_2 : s$ , we would be in fact assuming that systemwere non-causal (its current choices depending on the future value of conditionals) and in this case we could also have propagated all those decisions to the initial start time of the systemmodel ed by the GFE

The parallel composition assumes a synchronous execution semantics, also known as maximal parallelisms emantics. In this execution semantics, if two processes are executed in parallel, then one action of each process is executed atomically at the same time. We represent the actions that execute together by multisets of actions. For example, if multiset a defines  $\{a_1, \dots, q_n\}$ , where each  $a_i \in \mathcal{A}$  actions  $a_{-1}, \dots, a_n$  are executed at the same time.

The set consisting of multisets of actions is represented here by the symbol  $\mathcal{M}^{\mathcal{A}}$ . If two multisets  $a = \{a_{1}, \dots, q_{n}\}$  and  $b = \{b_{1}, \dots, b_{n}\}$  are composed in parallel, the resulting multiset  $\{a_{1}, \dots, q_{n}, b_{1}, \dots, b_{n}\}$  is represented by  $a \cup b$ . We sometimes abuse our notation for multisets and use  $a_{i}$  for  $\{a_{i}\}$  if it can be inferred by the context that  $a_{i}$  represents the multiset  $\{a_{i}\}$ .

In the definition of the axions of CFEs, we showed that the result of the parallel composition of two multisets a and b is dependent on some synchronization between a and b. A though a formal definition of synchronization will be presented in the next section, we will give an informal definition that will allow the reader to understand its meaning.

Processes synchronize in control-flow expressions by defining multisets of actions that always have to execute at the same time, and by defining multisets of actions that should never execute at the same time.

Loops and infinite computations can be defined by control-flow expressions with process variables. The loop composition  $(c:p)^*$  is equivalent to recursive process  $q = c: p \cdot q + \overline{c} : \epsilon$ , where p is a process variable. The infinite composition  $p^{-\omega}$  is equivalent to the recursive process  $q = p \cdot q$ . Their axions can be determined by applying those equations into axions of the original algebra.

## 3.4 Comparison of Control-Flow Expressions with Existing Formalisms

Control-flow expression is very useful as a modeling and abstraction formalism of CDFG since the translation from CDFG into CFEs is straightforward. In this section, we compare CFEs with other formalisms that were used to model the control-flow, while abstracting the dataflow information: regular expressions, path expressions, finite-state machines, Petri-nets, algebra of concurrent processes (ACP), calculus of communicating systems (CCS), timing expressions and BFSM, although this list is by no means exhaustive.

The algebra of regular expressions [19] is used represent strings accepted/emitted by a finite-state machine. This algebra is represented by (Σ, +, ·, \*), where Σ is the alphabet of characters accepted/emitted, +denotes alternative composition, · denotes sequential composition, and \*denotes zero or more repetitions of a subexpression.

Regular expressions have been used in the modeling of the control-flow of sequential programs [34, 26]. In order to specify the control-flow in terms of an input/output behavior, regular expressions must be extended to guard alternative branches and loops. Also, in the case of parallel descriptions, a parallel operator must be added. However, this parallel operator is redundant for regular expressions, since the left and right distributivity of the sequential operator with respect to the alternative operator allow concurrency to be traded by non-determinism[29]. Such expressiveness does not exist in control-flow expressions, because the sequential operator does not distribute to the right with respect to the alternative operator.

CFEs also extend regular expressions by defining infinite behaviors, which could be achieved only by extending regular expressions to  $\omega$ -regular expressions [9].

- **Pathexpressions** [8] are equivalent to regular expressions, with the addition of parallelism However, instead of a synchronous execution semantics for the parallel composition, path expressions assume an interleaved execution semantics. CFEs also extend path expressions by providing guards to alternative branches and loops, in the same way CFEs extended regular expressions.

- A fitte-state radiue [19] recognizer is a tuple (Σ, S, δ, S 0, F), where Σ is a set of inputs, S is the set of states, δ : S × Σ → S is the transition function, S is the set of initial states, and F is the set of final states. In the case of finite-state machines as computational engines, we also define an output al phabet O, and either the output transition function Δ : S -O (in the case of a More machine) or Δ: S × Σ -O (in the case of a More machine) is defined only at the transition level, in which several outputs may be generated at the same time. At this level, however, the duration for each output has already been determined, and any transformation of the specification that modifies this execution time cannot be performed.

Aspecification consisting of a set of concurrently executing finite-state machines can also be considered in this model, as in the case of reactive systemlanguages, such as StateCharts [11] and SDL [39]. In these languages, the system is modeled as a set of hierarchical concurrent finite-state machines, and the system's state is defined to be the state of the Cartesian product of all concurrently executing finite-state machines. As in the case described in the previous paragraph, at the level of finite-state machines, the execution time for the operations has already been decided, and thus any transfornation that changes the execution time of operations cannot be performed, without requiring a restructuring of the finite-state machine.

• Retri rets [36] are represented by the tuple  $(T, P, \delta, I)$ , where T is the set of transitions, P is the set of places, and  $\delta \subseteq T \rtimes P \cup P \rtimes T$  defines the transition relation (or firing) from transitions to places and vice-versa. Anarking in Petri-nets is an assignment of natural numbers (tokens) to places. I is the initial narking of the Petri-net.

Astate in a Petri-net is a marking of places. Transitions between states are achieved by having a marking that becomes another marking by firing some transition. This firing occurs when one transition of the net has all incoming places with more than one token. The transition takes one such token from each place and puts one additional token in every outgoing place. Since only one firing can occur at any time, this model can only represent interleaved concurrent systems.

One possible extension of Petri-nets is the synchronous firing semantics [43]. In this semantics, the set of firings that can occur at the same time is specified along with the Petri-net. Similarly to the concurrent finite-state machine model, any transformations

that changes the execution time of the operations, or the structure of the graph cannot be easily performed.

• **Rocess algebra** [1] and **CS** [30] correspond to a family of representations used to formally model concurrent systems. In these models, we view the system as a set of operations that are represented by *actions*, and their compositions in terms of sequential composition, non-deterministic choice, parallel composition and communication. Concurrency usually refers to interleaved concurrency, which is represented by non-deterministic choice; and synchronous concurrency is defined in terms of communication.

These representations can be considered as a superset of control-flow expressions. If we restrict the set of specifiable behaviors to regular and synchronous processes, then control-flow expressions will have the same representation capabilities of process algebras and CCS. One of the unique features of control-flow expressions that was defined previously in this paper is that we distinguish actions from conditionals. This allows the system to better capture the reactiveness nature of hardware systems, and as a result, control-flow expressions will fit better the model used for synthesis.

- Tiring expressions [46, 48] is a model for describing behaviors of sequential systems and specifying sequential constraints a sequential systemhas to satisfy [46]. In timing expressions, the sequential systemis represented by expressions that may take different values over time. When compared to control-flow expressions, we see that timing expressions will be better suited to represent the control information at lower levels of descriptions, whereas control-flow expressions will be better suited for representing the control-flow at higher-levels of descriptions. In addition, control-flow expressions can be considered as a superset of timing expressions, since CFEs can be used to represent systems containing hierarchical series-parallel specifications, whereas in timing expressions parallelismcan occur only at the highest level.

- **BFSMs** [45] are a generalization of finite-state machines with partial timing information on the relative execution time of the states. Through synthesis, a complete time (or schedule) is obtained. This model closely resembles the algebra of control-flow expressions because it was used for modeling and synthesis of control-dominated specifications. However, the lack of a synchronization formalismand the lack of a formal model for constraint specification — which is restricted to scheduling constraints prevents BFSM frombeing used in more complex problems. As opposed to CFEs, which uses both expression and finite-state machine representations for a concurrent system the translation from the specification to a finite-state machine description is performed too early with BFSM, and thus, optimizations that would be best used at the expression level — such as hierarchical abstraction and rewriting — would not be available to the synthesis process. Finally, BFSM is a model best suited for representing the control-flow of languages in which parallelismis specified at the process

level, such as VHDL. If used to represent the control-flow of languages that can specify series-parallel composition of systems, such as Verilog HDL, its representation and constraint specification becomes cumbersome.

When compared to the formalisms presented above, control-flow expressions are able to capture more succinctly the control-flow information, abstraction from the original specification, and the degrees of freedom When considering specifications in terms of CDFGs (or in terms of the corresponding HDL code) control-flow expressions fit perfectly as a modeling tool of the control behavior for synthesis of system level specifications.

## 4 Constraint Specification

In the previous section, we presented the algebra of control-flow expressions, and how to abstract the dataflow information and represent the control-flow of the design. Real designs consist of specification and design constraints. In this section, we show how to use CFEs to represent constraints, such as scheduling, binding, and synchronization.

The specification of a systemat higher levels of abstraction requires the modeling of non-determinism since at these levels, not all synthesis decisions have been made. In the algebra of control-flow expressions, we model these non-deterministic choices of the design by guarding the choices with decision variables, which quantify the design space.

Wy present in this section the incorporation of design constraints by control-flow expressions. Both the specification and the constraints will be converted to a finite-state representation in the next section, where we will be able to obtain the controllers satisfying design constraints.

## 4.1 Quantification of the Design Space

We represent here the design space and constraints by means of *decision variables*, which are used as guards of GFEs:

**Defition 4.1** A decision variable d is a variable guarding the execution of a control-flow expression whose value is determined by the synthesis procedure. Its possible values are defined as the set of Bool ean formulas over some set  $\mathcal{D}$ .

A decision variable is a Boolean variable that quantifies a constraint, i.e., whenever the decision variable is true, the constraint is satisfied. As impleimplementation that has been sought in the past is the assignment of decision variables to constant values over time [21]. Later, we showhow to obtain assignments to the decision variables that considers the "state" of the systembeing synthesized. Thus, in some cases, the set  $\mathcal{D}$  will be the set of conditionals  $\mathcal{C}$ , with the Boolean constants  $\{0, 1\}$ . When we obtain a finite-state machine satisfying the constraints in the next section, the different machines we can choose from will be uniquely determined by different assignments to the decision variables.

In the algebra of control-flowexpressions, we are going to use decision variables as guards of expressions, so we will need to extend guards to allow decision variables and conditionals to be composed together. Because decision variables will uniquely determine the satisfaction of a constraint, we only need to compose guards with conjunctions of decision variables, or their complements. This also states that any non-determinismfrom the specification will be uniquely guarded by a Bool ean guard.

**Defition 42** A guard is a conjunction of decision variables (or their complements) and a Bool ean formula over the set of conditionals.

**Earple 4** Consider the code w = y \* z; u = w + 3; Assume both the multiplication and the addition take one clock cycle, and that w = y \* z is represented by action a and u = w + 3 is represented by action b. A *anstraint* between a and b, or the quantification of all possible schedules such that b occurs after a is represented by the CFE  $a \cdot (x * 0)b$ , where  $a, b \in A$ , and  $x \in D$ . In this CFE, the possible schedules are quantified by the different assignments of the decision variable x over time.

Possi bl e assi gnments coul d be:

$$\begin{array}{c} a \cdot b \\ a \cdot 0 \cdot b \\ a \cdot 0 \cdot 0 \cdot b \\ \vdots \\ a \cdot 0 \cdot \cdots \cdot 0 \cdot b \end{array}$$

The first assignment corresponds to an assignment of x to fdseafter the execution of action a. The second assignment corresponds to an assignment of x to *true* after the execution of a, then to fdse. The other assignments have a similar correspondence.  $\Box$

## 4.2 Constraint Representation

Constraints are properties that any implementation needs to satisfy. Wy consider here a subset of constraints that can be specified as scheduling constraints, binding constraints and synchronization constraints. More complex specifications can be achieved by composing these constraints using control-flow expressions.

Timing constraints will be defined in terms of control-flow expressions. In binding constraints we will use expression rewriting, i.e., the incorporation of binding constraints as a modification of the original CFE Both timing and binding constraints will use decision variables as quantifiers of the design space. Finally, synchronization constraints will use multisets of actions that should occur at the same time and multisets of actions that should never occur at the same time.

The constraints will be defined in terms of the actions that appear in a control-flow expression, which we define below as the *support* of a GFE

**Defition 43** The support of a control-flow expression p is defined as the set of actions that are executed in p.

**Example 5** The support of a GFE  $p = (a \cdot b)$   $||(c \cdot d \cdot e)$ , written as p, is the set of actions of p. Here,  $S = \{a, b, c, d, e\}$ .  $\Box$

Each action defined in the support of a CFE will have a shadowaction, which executes every time the corresponding action executes.

**Defition 44** A shadow of an action a, written as  $\sigma$  <sub>a</sub>, is defined to be an action that does not correspond to any operation of the original specification and executes every time action a is executed.

**Example 6** In the CFE  $(a \cdot b \cdot c)$   $\omega$ ,  $\sigma_a$  is executed every time *a* is executed, ices executed every time *b* is executed, and  $\sigma$  is executed every time *c* is executed.  $\Box$

#### 421 Stedding Costraints

Scheduling constraints are constraints that specify the timing relations among computations. At though we will only define minimum and maximum timing constraints here, we can specify and handle a much richer set of constraints with control-flow expressions, including loops, alternative composition and synchronization, as opposed to the constraints that are handled in other CAD tools, such as [40, 44, 25, 3]. The specification of scheduling constraints using control-flow expressions can be also considered as an extension of path constraints defined by [40].

Let us assume p to be a CFE representing a specification of a design with support  $S_{p}$ . Suppose we want to represent initially simple minimum and maximum constraints between two actions a and b, with  $a, b \in S_{p}$ .

**Defition 45** A minimum timing constraint of n cycles between two actions a and b, whose shadow actions are  $\sigma_{a}$  and  $\sigma_{b}$ , can be represented by the  $GE(x:0) * \sigma_{a} \cdot 0^{n-1} \cdot (y:0) * \sigma_{b}$ , where x and y are decision variables.

**Defition 46** A maximum timing constraint on n cycles between two actions a and b, whose shadowactions are  $\sigma_{a}$  and  $\sigma_{b}$ , can be represented by the  $GE(x:0) = * \cdot \sigma_{a} \cdot (y:0)^{\leq n} \cdot \sigma_{b}$ , where x and y are decision variables.

Let p be a control-flow expression representing a specification and let  $m_1, \ldots, p$  be a set of CFEs representing scheduling constraints. The control-flow expression  $p||m_1||\cdots||m_n$  will denote the application of the n scheduling constraints to the specification p.

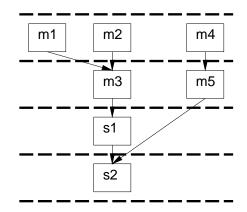

Figure 9: ODFG of a differential equation example

**Earple 7** The design in Figure 9 is the control-data flow graph of a subset of the loop of a differential equation solver [28]. Assume that the CFE for the specification is p, and that we want to specify a maximum iming constraint of 3 cycles between p and  $s_2$ , which can be represented by the CFE  $(x: 0)^* \cdot \sigma_{m_4} \cdot (y: 0)^3 \cdot \sigma_{s_2}$ , where x and y are decision variables.

The application of this constraint to the CFE p is represented by a new CFE  $p \mid (x^*: \mathfrak{G}_{p_4} \cdot (y : 0)^{<3} \cdot \sigma_{s_2}$ .  $\Box$

In the previous example, we specified conventional minimum and maximum timing constraints. As we pointed out before, CFEs can be used to specify a much broader set of scheduling constraints, and even hide interface information from the original specification, as shown in the following example.

**Earle 8** Let us examine the specification of the scheduling constraint presented in Section 2.2. In this example, the different actions that are involved in the transmission of the data are the actions "Ras", "Cas" and "data". Associated with the action "send", we have the shadowaction  $\sigma_{\text{send}}$ . The constraint that specifies that the send operation should take either three or one cycle, depending on the address selection, can be represented by the control-flow expression ( $x(z; \theta)$ ) { $\sigma_{\text{send}}, Ra$ }  $\cdot 0 \cdot \{Caz, dta\} + \overline{s_a} : \{\sigma_{\text{send}}, dta\}$ ).  $\Box$

#### 422 Brding Constraints

B nding constraints specify the possible implementations for each computation that is represented by an action. W represent binding constraints as a rewriting of the original controlflow expression.

**Defition 47** Let p be a control-flow expression with support S  $_p$ . A rewriting of p, written as  $\mathcal{R}(p)[a \leftarrow q]$ , where q is a control-flow expression, is defined as the substitution of every occurrence of  $a \in S$   $_p$  in p by q.

**Example 9** Assume we make the rewriting of a by  $(c_1 : a_0 \cdot a_1 + c_2 : a_0 \cdot a_1 \cdot a_2)$  into  $p = (a \cdot b^{\alpha}) || (c \cdot d \cdot e)$  Then:

$$\mathcal{R}(p)\left[ a \leftarrow \left( c: a_0 \cdot a_1 + c_2 : a_0 \cdot a_1 \cdot a_2 \right) \right] = \left( \left( c_1 : a_0 \cdot a_1 + c_2 : a_0 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \right) \left| \left| \left( c \cdot d \cdot e \right) \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| \left| c_1 \cdot d \cdot e \right| \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| \left| c_1 \cdot d \cdot e \right| \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| \left| c_1 \cdot d \cdot e \right| \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| \left| c_1 \cdot d \cdot e \right| \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot a_1 \cdot a_2 \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot d \cdot e \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot d \cdot e \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot d \cdot e \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot d \cdot e \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot d \cdot e \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot d \cdot e \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot d \cdot d \cdot e \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot e \right| = \left( c_1 \cdot d \cdot d \cdot e \right) \cdot b^{\alpha} \left| c_1 \cdot d \cdot d \cdot e \right| = \left( c_1$$

**Defition 48** Let p be a CFE of a specification and assume some action a can be implemented by a set of components { $C_1, C_2, \dots, C_m$ }. This binding constraint is represented by the CFE

$$\mathcal{R}p)[a \leftarrow \sum_{1 \le i \le m} x_i : C_i]$$

where  $\sum_{1 \leq i \leq m} x_i : C_i$  represents the alternative composition of the metrics  $(x \quad i : C_i)$ , and  $x_1, \dots, x_m$  are modecision variables.

In this expression rewriting, whenever  $x_i$  is *true*, component  $C_i$  implements the computation abstracted by action a. Note that since decision variables are assumed to take values from the set of Boolean formulas over  $\mathcal{P}$  and not just the values 0 or 1, we may have an implementation in which some  $x_i$  enables component  $C_i$  at some time, and at a later time  $x_j$  ( $i \neq j$ ) enables component  $C_j$ , thus implementing dynamic binding of components.

**Example 10** In this example, assume that actions  $m_i$ ,  $i = 1, \ldots, 5$  of Figure 9 can be implemented by one of three multipliers  $_1MM_2$ ,  $M_3$ . Then, for the CFE p that represents this CDFG, we define the binding for each mas:

$$\mathcal{R}(p) [m_i \leftarrow (x_{i_1}: M_1 + x_{i_2}: M_2 + x_{i_3}: M_3)]$$

where *i* ranges over 1 to 5 and  $x_1$ ,  $x_{i2}$  and  $x_{i3}$  are decision variables  $\Box$

Note that in this section we are only specifying binding constraints. When an assignment to the decision variables is obtained in such a way that different bindings are selected at different times, then we refer to this as dynamic binding.

#### 423 Syntraization Constraints

Synchronization constraints specify actions that should be executed at the same time and actions that should never be executed at the same time. The former type of synchronization corresponds to the specification data transfers, or control transfer fromone specification to another. The latter kind of synchronization allows one to specify exclusive use of a resource by some individual process.

We define below ALMAYS and NEVER sets, which are sets consisting of multisets of actions.

**Defition 49** Let ALMANS be a set consisting of multisets of actions that contains multiset X. If two actions a and b belong to the same multiset X, then a and b must always execute at the same time.

**Defition 4 10** Let NEMER be a set consisting of multisets of actions that contains multiset X. If two actions a and b belong to the same multiset X, then a and b must never execute at the same time.

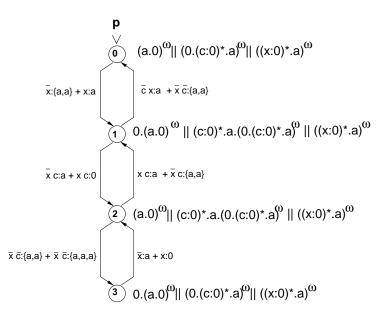

**Earple 11** Let us consider the synchronization synthesis problem presented in Section 2.1.1. In this problem, let us assume the following control-flow expressions for the processes *DMAcad*. *DM:nit* and *equee*, respectively:

$$p_{1} = [a. 0]^{\psi}$$

$$p_{2} = [0. (c : 0) a^{\psi}]$$

$$p_{3} = [(x : 0)^{*} . a^{\psi}]$$

Where a corresponds to the bus access and 0 hides the internal computation from the original specification. The conditional c hides the evaluation of *transissionady* predicate and the decision variable x quantifies the predicate *free bus* In this case, since we have the additional restriction that no two bus accesses should occur at the same time, we have  $NEVIR=\{\{a, a\}\}$ .  $\Box$

In summary, we showed how to represent scheduling, binding and synchronization constraints in this section. More complex constraint specifications can use these three types of constraints as building blocks, with the compositions of control-flow expressions as a way to combine these constraints.

## 5 Finite-State Representation

This section shows how ogenerate a finite-state representation from control-flow expressions. As we have shown in Figure 1, we use both the algebraic and the finite-state representations in our synthesis tool. The algebraic representation presented in the previous sections allowed us to manipulate and rewrite the the expressions algebraically. The finite-state representation allows us to analyze and to synthesize the control lers for the specification.

W obtain a finite-state representation from a control-flow expression by computing all the suffixes of the expression. Informally, a suffix of a control-flow expression represents the state of the systemafter an n-cycle simulation of the system. W show that this state can be represented by another CFE, and we call this simulation of the CFE to obtain its suffixes a *derivative*, because of the its resemblance to the work of Brzozowski [7] who first defined derivatives of regular expressions.

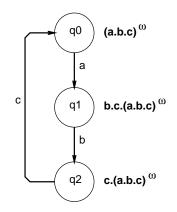

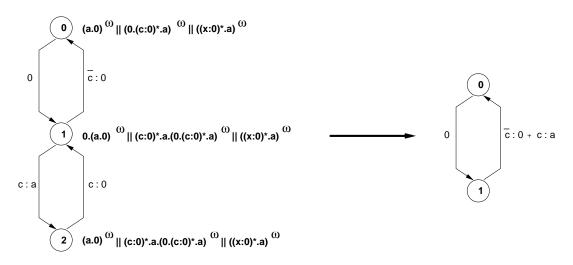

In the following example, we will present the keyideas of this section in obtaining a finitestate representation for a control-flow expression by enumerating its suffixes. The algorithm will be formalized later. **Earple 12** For the control - flow expression  $p = (a \cdot b \cdot c)^{-\omega}$ , we wish to obtain a finite-state Meal y machine. By inspecting p, and assuming that a, b and c are the outputs to the finite-state machine representing p, we know that a Meal y machine starting at some initial statemakes a transition to some state q with output a being generated. From state  $_1q$  the finite-state machine makes a transition to some state  $_2q$  with output b. Finally, a transition q curs to the original state q with output c. The Meal y machine for this control-flow expression is presented in Figure 10.

If we nowlook at the possible suffixes of p, the CFE  $b \cdot c \cdot (a \cdot b \text{ is } c)$  betained after similating  $(a \cdot b \cdot c^{\omega})$  for one cycle, and the CFE  $c \cdot (a \cdot b \cdot c^{\omega})$  sobtained after similating  $b \cdot c \cdot (a \cdot b \text{ for } c)$  one cycle. Thus, we can associate the states  $q_1$  and  $q_2$  with the suffixes  $(a \cdot b \cdot c^{\omega})$ ,  $b \cdot c \cdot (a \cdot b \cdot c)$  and  $c \cdot (a \cdot b \cdot c)$  respectively.  $\Box$

Figure 10: Mealy machine for control flowexpression  $(a \cdot b \cdot c)$

What we need to show now is how to compute the suffixes of a control-flow expression, that there is only a finite number of suffixes for a given CFE, and that there is an equivalence relation between the suffixes of a control-flow expression and the states of its corresponding Metal y automaton. This is described formally in Appendix A W suggest to the reader who is interested in the mathematical foundation of this work to go first to this appendix before proceeding to the next section.

#### 5.1 Constructing the Finite-State Representation

We present in this section a procedure to obtain the finite-state Mealy machine from a control-flow expression using derivatives. This Mealy machine is formally represented by  $M = (I, Q, Q, \delta, \lambda, q)^2$ , where I is the set of input variables of M O is the set of output symbols of M Q is the set of states,  $q_0$  is the initial state,  $\delta$  is the transition function of M i.e.,  $\delta = Q \times 2^{-I} - Q$  and  $\lambda$  is the output function of M i.e.,  $\lambda : Q \times 2^{-I} - 2^{-O}$ .

<sup>&</sup>lt;sup>2</sup>We use the Greek letter  $\delta$  to denote the transition function as used in literature. This  $\delta$  is different from the  $\delta$  introduced in Section 3.3, but the reader should be able to easily recognize when we are referring to the *deadlock* symbol and when we are referring to the *transition function* of the Mealy machine M.

This Mealy machine is related to the set of derivatives of p in the following way. The set of input variables of Mcorresponds to the set of conditional and decision variables of p. The set of outputs of Mcorresponds to the multiset of actions of p. With each irredundant suffix s of p, we associate a state  $q_s \in Q$ . In particular,  $q_0$  corresponds to the state  $q_p$ , i.e., to the GE p itself.

The transition function  $(\delta)$  and the output function  $(\lambda)$  are related to the GE p in the following way. Let s be an irredundant suffix of a control-flow expression p, for which we are building the finite-state machine representation. The triple  $(\gamma, \mu, \pi) \in \mathcal{G} \times \mathcal{M}$   $\mathcal{A} \times \mathcal{F}(defined formally in Appendix A)$ , obtained from a GE p, indicates that the actions  $\mu$  are executed when  $\gamma$  is true, followed by the execution of  $\pi$ . Assume that  $(\gamma, \mu, \pi) \in \partial s$ , where  $\partial s$  denotes the derivative of s. Thus,  $\delta(q_s, \gamma) = \pi$  and  $\lambda(q_{-s}, \gamma) = \mu$  in  $\mathcal{M}$

Figure 11: Finite-state representation for synchronization synthesis problem

**Example 13** Figure 11 shows the finite-state representation for the synchronization example whose control-flow expression was presented in Example 11  $(p \mid p \mid p)$ .  $\Box$

Note that the derivative computation does not take into account the synchronization constraints. Thus, we will need the following definitions.

**Defition 51** A transition  $\delta(q, f)$  of a finite-state Maly machine representation of the control-flow expression p is valid if

- $\forall x \in AUADS, (\lambda(q, f) \cap x \neq \emptyset) \Rightarrow (x \subset \lambda(q, f))$

- $\forall x \in NEMR, x \not\in \lambda(q, f).$

The definition above states that if at least a certain action in a transition is included in some multiset of actions of the *ADMAS* set, then all actions in this multiset should be executed in the transition. Furthermore, this transition should not include any multiset of actions of the *NEWER*set. This condition guarantees that the transition will not violate the synchronization requirements of the design.

Since some of the transitions of the Mealy machine may be invalid, we have also to check whether a state of the machine is reachable by valid transitions or not.

**Perpendicular** 51 The initial state  $q_p$  of the finite-state Maly machine representing the control-flow expression p is reachable, and so is any other state  $q \in Q$  such that there is at least one valid transition from another reachable state to q.

```

/* Breath First Search of state space represented by CFE p */

procedire Const ruct_FSM

imt: cfe, ALWAYS, NEVER

otpt: finite-state machine M

/* initialize fifo with initial cfe */

fifo.init (cfe)

while (fif o \neq \emptyset) {

/* get cfe on top of fifo */

cf e = fif o. first()

/* mark cfe as traversed and make it a state */

mark(cfe)

/* compute all cfe's one cycle apart */

derivative = \partial (cfe)

\forall (\gamma, \mu, \pi) : (\mathcal{G} \times \mathcal{M} \times \mathcal{F}) \in derivative \{

/* check if it violates ALWAYS and NEVER sets */

if (\mu \cap ALWAYS \neq \emptyset)

if (ALWAYS \not\in \mu) continue

if (\mu \cap NEVER \neq \emptyset)

if (NEVER \in \mu) cartine

/* transition is valid*/

add edge (cfe, \gamma : \mu, \pi) to finite-state machine

if unmarked (\pi)

/* if suffix isn't a state, insert it in fifo */

fif o. i ns ert (\pi)

}

}

remove unreachable states

}

```

Figure 12: Algorithm to construct finite-state representation

The algorithm of Figure 12 is used to compute the finite-state Mealy machine *M* of a specification. The algorithm works by traversing the finite-state machine in a breath-first search manner, and eliminating the invalid transitions and the unreachable states. The finite-state machine obtained contains only the reachable states and valid transitions of the system. The design space represented by the scheduling and binding constraints are embedded into the original control-flow expression of the specification.

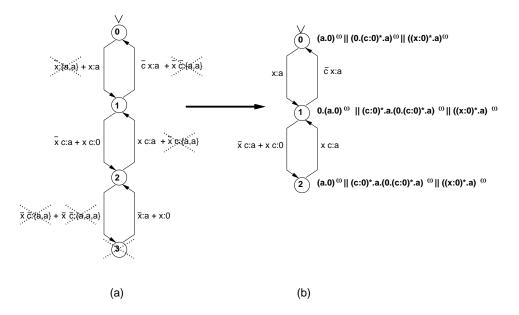

Figure 13: Finite-state representation observing synchronization constraints

**Earple 14** If we apply the  $MMR = \{a, a\}$  constraint to the finite-state representation of  $p_1 \mid p \mid p$  (shown in Example 13), we obtain the finite-state representation of Figure 13-b.

Note that state 3 becomes unreachable from the initial state, and thus can be eliminated from the final finite-state representation.  $\Box$

#### 5.2 Feasibility of Solutions

In the design process, the user may want at some point to determine if there exists an implementation for the specification in presence of a set of design constraints. The following theorems hows how one can test whether a problem is overconstrained or not.

**Technicial** Suppose p is a control-flow expression along with the synchronization constraints specified by the sets ALMANS and NEMER If the procedure Construct\_FSM(p, ALMANS, NEMER) returns an empty finite-state muchine, then the specification is overconstrained.

**Proof.** We know that at least one state should exist in the finite-state machine: the state corresponding to  $q = p | |_{h} m \cdots |_{h} m$  If this initial state does not exist in the finite-state machine, it means that it was first generated (before the **while** loop of the algorithm in Figure 12), but later removed from the finite-state machine because the state was unreachable. Since invalid transitions are eliminated when they violate synchronization constraints, q was overconstrained.

Note that the converse may not be true, however. If the overconstrained part of the specification is not large enough to make all states unreachable, then an implementation is

still obtained for the parts of the specification that satisfies the constraints.

# 6 Synthesizing Control-Units from the Finite-State Representation

Figure 14: Methodology for synthesizing control-units

We present in this section a methodology to synthesize control-units from the finite-state representation. Figure 14 gives a pictorial view of the synthesis method. From the specification represented by the set of concurrent processes  $p_1 || \cdots || p_i || \cdots || p_n$ , and the synchronization constraints expressed by the *AUMS* and *NEWR* sets, we obtained a finite-state machine representation by the algorithms hown in the previous section. From this finite-state representation, which already contains all feasible behaviors, we look for a feasible implementation that has been optimized with respect to a cost function. In particular, we obtain in this section the implementation by casting the synthesis problemas a 0-1 Integer Linear Programming instance. Note that the optimized finite-state representation model the systemas a whole. Thus, to derive the controller for each individual process  $p_i$ , we project the set of decisions made for the implementation into  $p_i$ . This methodology can be used to synthesize the controllers of concurrent systems with arbitrary control-flows, as well as systems with environment and synchronization constraints.

The major difference between our formulation and previous approaches to synthesis, such as [21, 37, 24, 14], is that we do not have the notion of a control-step as a linear order over time, because of loops, synchronization and concurrency. Whereas the control flows only in one direction in single-source single-sink dataflows, loops makes the analysis of the controlflow to depend on the different assignments to the conditionals. Concurrency implies that different instances of the same piece of computation requires different decisions. Finally synchronization implies that the different parts of the specification should not be treated separately. Thus, the complexity of the synthesis task becomes much higher.

The dependency of the flow of control on the conditionals and on the design constraints prevent us from formulating the synthesis problem in terms of control-steps. However, we can define the synthesis problem in terms of a equivalent entity: the state of a finite-state machine.

W will consider, thus, the finite-state machine  $M = (I, Q, Q, \delta, \lambda, q_{-0})$  defined in Section 5.1 that represents the control-flow expression p and the synchronization constraints. This finite-state machine was obtained by the algorithm in Figure 12. Wassume that Q contains only reachable states and  $\lambda$  contains only valid transitions.

Since we enriched the control-flow expression of the specification with decision variables in order to quantify the design space, the corresponding finite-state machine contains a representation of the design space according to the degrees of freedomintroduced. Thus, we define now what we mean by an implementation of the finite-state machine M

**Defition 6.1** Let M be the finite-state machine obtained from a control-flow expression through derivation. We call M ' an implementation of M if the following conditions hold.

- 1. The set of states of M' is a subset of the set of states of M

- 2. The initial states of M and M ' are the same.

- 3. The set of transitions of M ' is a subset of the set of transitions of M

Thus, an implementation  $M' = (I, Q, Q', \vartheta, \chi, q_0)$  will be an implementation of  $M = (I, Q, Q, \vartheta, \lambda, q)$  if  $Q \subseteq Q \vartheta' \subseteq \vartheta$  and  $\lambda' \subseteq \lambda$ . In addition to the requirements given above, we still require that M also satisfies additional constraints that will be imposed by the structure of the original specification. We will present by an example the formulation of the multi-process synthesis problemas an ILP. The complete formulation can be seen in Appendix B

In the synthesis of M' from M we have to identify which states will be included in M'and which transitions will be part of the transition function for M'. In order to determine the states of M which will be part of the states of M', we create a Boolean variable  $y_p$  for each state  $q_p$  of M If the Boolean variable  $y_p$  is set to 1, our interpretation will be that the state  $q_p$  will belong to M'. Will denote the state  $q_p$  by p in the remainder of this section.