# SPARC-V9 ARCHITECTURE SPECIFICATION WITH RAPIDE

Alexandre Santoro Woosang Park David Luckham

Technical Report: CSL-TR-95-677

(Program Analysis and Verification Group Report No. 71)

September 1995

This research has been supported by DARPA under ONR contract N00014-92-J-1928, contract N00014-93-1-1335 and under TRW, subcontract FZ2394LK1S-04.

## SPARC-V9 Architecture Specification with Rapide

Alexandre Santoro Woosang Park David Luckham

Technical Report: CSL-TR-95-677

Program Analysis and Verification Group Report No. 71

September 1995

Computer Systems Laboratory Departments of Electrical Engineering and Computer Science Stanford University Stanford, California 94305-4055

#### Abstract

This report presents an approach to creating an executable standard for the SPARC-V9 instruction set architecture using Rapide-1.0, a language for modeling and prototyping distributed systems. It describes the desired characteristics of a formal specification of the architecture and shows how Rapide can be used to build a model with these characteristics. This is followed by the description of a simple prototype of the proposed model, and a discussion of the issues involved in building and testing the complete specification (with emphasis on some Rapide-specific features such as constraints, causality and mapping). The report concludes with a brief evaluation of the proposed model and suggestions on future areas of research.

Key Words and Phrases: SPARC-V9, Rapide, instruction set architectures, modeling, formal specification, constraints

Copyright © 1995 by Alexandre Santoro Woosang Park David Luckham

# Contents

| 1        | Intr           | oduction                                           | 1         |

|----------|----------------|----------------------------------------------------|-----------|

|          | 1.1            | The SPARC-V9 Instruction Set Architecture Standard | 3         |

|          | 1.2            | The Rapide Prototyping Language                    | 4         |

| <b>2</b> | $\mathrm{The}$ | e Model                                            | 9         |

|          | 2.1            | Objectives                                         | 9         |

|          | 2.2            | Approach                                           | 11        |

|          | 2.3            | Basic Type Set                                     | 13        |

|          | 2.4            | Components                                         | 18        |

|          | 2.5            | Architecture                                       | 22        |

| 3        | Sca            | led-Down Rapide-0.2 Model                          | <b>27</b> |

|          | 3.1            | Model Architecture                                 | 27        |

|          | 3.2            | Sequential Execution in Rapide-0.2                 | 31        |

|          | 3.3            | Pipelined Execution in Rapide-0.2                  | 34        |

| 4        | Obs            | ervations                                          | 39        |

|          | 4.1            | Testing                                            | 39        |

|          | 4.2            | Readability $\ldots$ $\ldots$                      | 41        |

|          | 4.3            | Constraints                                        | 44        |

|          |                | 4.3.1 Example 1: Error Constraint                  | 46        |

|          |                | 4.3.2 Example 2: Behavior Constraint               | 47        |

|          |                | 4.3.3 Example 3: Structural Constraint             | 48        |

|          | 4.4            | Mapping                                            | 49        |

| 5        | Cor            | clusion                                            | 51        |

| Α | $\mathbf{Cod}$ | ing Guidelines                   | 57 |

|---|----------------|----------------------------------|----|

|   | A.1            | Observations                     | 57 |

|   | A.2            | Guidelines                       | 57 |

| в | Rap            | ide Interface for Basic Types    | 60 |

|   | <b>B.</b> 1    | $\operatorname{ReadReg}_t$       | 60 |

|   | B.2            | $\operatorname{ReadWriteReg\_t}$ | 60 |

|   | B.3            | UpCounter_t                      | 61 |

|   | <b>B.</b> 4    | UpDownCounter_t                  | 61 |

|   | <b>B</b> .5    | DispCounter_t                    | 62 |

|   | <b>B.</b> 6    | SPARCint_t                       | 62 |

|   | <b>B.</b> 7    | SPARCreal_t                      | 63 |

|   | <b>B.</b> 8    | $\operatorname{RegStack\_t}$     | 64 |

# List of Figures

| 1.1 | Sample resulting poset                                                                                        | 6  |

|-----|---------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Poset indicating a constraint violation                                                                       | 7  |

| 1.3 | Example of mapping                                                                                            | 8  |

| 2.1 | Type hierarchy tree for register types                                                                        | 16 |

| 2.2 | Simplified SPARC-V9 Architecture                                                                              | 25 |

| 3.1 | Scaled-down SPARC architecture in Rapide-0.2                                                                  | 29 |

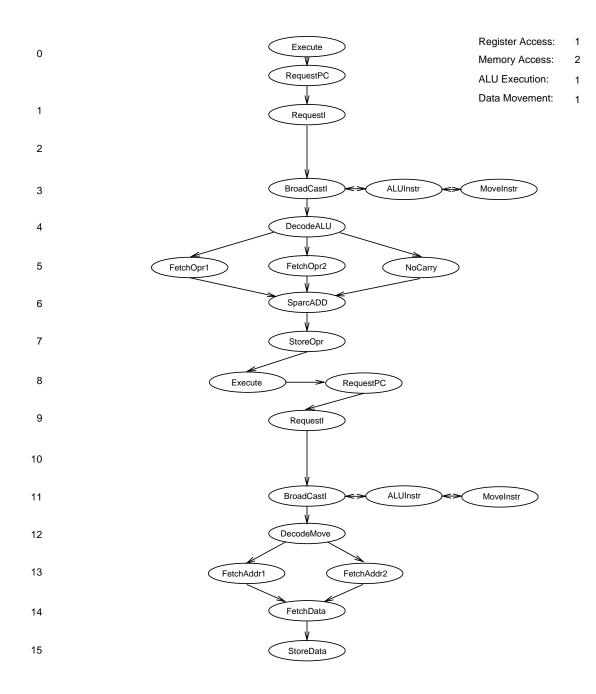

| 3.2 | Poset of Add-Load Execution in Rapide-0.2                                                                     | 32 |

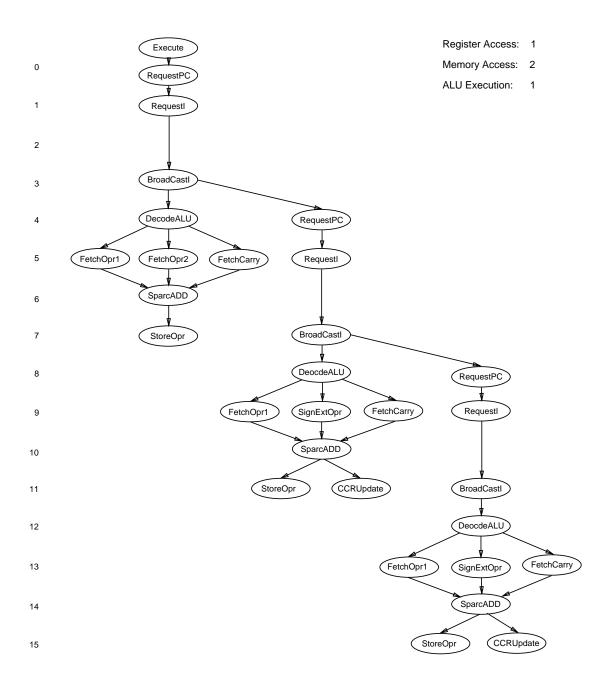

| 3.3 | Poset of Pipelined Execution in Rapide-0.2                                                                    | 36 |

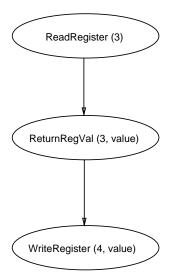

| 4.1 | Ideal poset for the $r[4] := r[3]$ operation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 43 |

| 4.2 | Example of an error constraint violation                                                                      | 47 |

| 4.3 | Example of behavior constraint violation                                                                      | 48 |

# List of Tables

| 2.1  | SPARC-V9 register set characteristics                                                                         | 14 |

|------|---------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Function description for $ReadReg_t$                                                                          | 15 |

| 2.3  | Function description for ReadWriteReg_t $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$             | 17 |

| 2.4  | Added functions for $UpCounter_t$                                                                             | 17 |

| 2.5  | Added functions for UpDownCounter_t                                                                           | 17 |

| 2.6  | Added functions for $RegStack_t$                                                                              | 18 |

| 2.7  | Added functions for DispCounter_t $\hdots$                                                                    | 18 |

| 2.8  | Added functions for SPARCint_t $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 19 |

| 2.9  | Added functions for SPARCReal_t                                                                               | 19 |

| 2.10 | Execution units and their related opcodes                                                                     | 23 |

| 3.1  | action definitions for SPARC-V9 prototype                                                                     | 30 |

| 4.1  | Test vector count for suggested approach                                                                      | 42 |

# Chapter 1

# Introduction

This report describes an implementation-independent model of the SPARC-V9 instruction set architecture standard[WG94] using the Rapide prototyping language. The model described here is intended for multiple use. First, it is to be an on-line *executable* manual to help developers understand the standard. Second, it should serve as a design-verification tool, to which actual implementations will be compared in order to verify conformance to the standard. Finally, it is an exploration tool, enabling the user to easily modify the model in order to create different versions of the standard.

An instruction set architecture (ISA) is a description of a processor. It defines the processor as a series of state storage units (the registers), a list of opcodes, explanations of how the opcodes affect the state of the machine, and how it reacts to other forms of input such as interrupts and reset signals. Usually, ISA descriptions concentrate on defining the behavior of the architecture, leaving actual implementation issues (the width of the data bus, for example) to the processor designer.

The SPARC-V9 instruction set architecture specification[WG94] uses plain English, along with diagrams to explain how the instruction set architecture behaves. Even though that is the usual way of explaining things, the English language is, by nature, ambiguous. Some descriptions may be misinterpreted, possibly leading to an erroneous implementation of the architecture. This makes it necessary to come up with a specification that is preferably both unambiguous and easy to understand.

An approach to this problem is to use a formal specification language to describe the standard. By using a formal specification, one avoids ambiguity problems since the language constructs that describe the model are completely specified and their meaning is unambiguous. This should remove any questions or doubts introduced by the use of the English language.

There is, of course, a price to pay for using a formal specification language to describe the standard. First, in order to make it well-defined, it is necessary to restrict the meaning of each language construct. The resulting code will have to be more verbose and complex when describing something, so that understanding it will take more effort. Second, the precise, well-defined behavior of the language makes it hard to implement non-determinism in the model, should it be so desired. This non-determinism contradicts the concept of complete formal specification and the result is that it is not present in the languages most commonly used for describing hardware: Verilog [TM91] and VHDL[VHD87]. This is not to say that non-determinism cannot be emulated; it can, but usually requires complex coding to circumvent the language's limitations.

A third issue related to specification languages is the choice of the domain. One can specify a model through several different domains. In the case of hardware design, for example, the common domains are behavioral, structural and geometric[GT88]. A *behavioral* specification describes a model in terms of what it does; a *structural* specification defines a model in terms of the structures that have to be present and how they interconnect; a *geometric* specification describes a model in terms of the geometric layout of its components. Each has a different use, depending on the objective of the specification. Specification languages are geared towards different domains and the issue is choosing one that is adequate for the correct model description.

Even within a domain, there is still the issue of at which level one wants to look at the model. Suppose one wants to write a hardware model of a processor, describing only its behavior. One can do it by describing the model at the register-transfer level, indicating which operations result in changes to the model's registers; one could use traditional programming language constructs such as *if* and *case* statements to help describe the flow of information. One could also describe the model as a series of logic equations, which would reflect more thoroughly an implementation, but be much more complex to understand. Clearly, it is necessary to choose which level of abstraction is desired and choose a language that favors that choice.

Still, there are advantages to using hardware description languages for describing architectures. A formal specification provides a framework for verifying the correctness of an implementation. It states the expected behavior/structure/layout of the system and it is up to the designer, maybe with the help of some tools, to check if the implementation conforms to the specification. To achieve this goal, many specification languages are accompanied by compilers, browsers and other tools that simplify their use in simulation and verification.

Since instruction set architectures are usually implemented as hardware, they are often described by hardware description/simulation languages, since these languages serve as the framework for building actual implementations. Verilog and VHDL are the most common languages for hardware description. They are powerful and versatile, allowing mixed-mode (containing both structural and behavioral parts) descriptions of a model. Unfortunately, they are strongly geared towards simulation, thus requiring too much detail in their descriptions, and forcing the designer using such a model as the specification to worry about bit-level design and implementation issues much earlier than one should have to.

Another language commonly used for instructions set specification is ISPS[Bar81]. ISPS is a register-level language designed specifically for describing instruction set architectures, and has been used in previous versions of the SPARC instruction set architecture definitions[Int92]. Though it did a good job of describing the standard, at that time it lacked executability. This made it hard to debug and verify ISPS models for correctness.

In order to formally specify the SPARC-V9 instruction set architecture it is necessary

to use a language that is both *high-level* and *executable*. This will lead to a model that is verifiable and easy to understand. Rapide, as will be seen in section 1.2, has the necessary characteristics for this.

In the next pages we propose an implementation of the SPARC-V9 instruction set architecture standard using Rapide. The rest of this chapter describes the SPARC-V9 standard and the Rapide Prototyping language. Chapter 2 describes the suggested approach for creating the executable standard, while chapter 3 shows the results of a small exercise in creating the model using Rapide-0.2, a previous version of the language. Chapter 4 comments on the results and uses of the model, and chapter 5 presents our conclusions. Finally, the appendices present the guidelines for coding the model and the code for the interface of some basic types.

#### 1.1 The SPARC-V9 Instruction Set Architecture Standard

SPARC-V9 is an instruction set architecture standard for a RISC style processor[WG94]. Among its major characteristics are 64-bit integers, 64-bit virtual addresses, support for superscalar and multiprocessor implementations (through its instruction set), and fast context-switching. There are approximately 20 control/status registers, 32 double-precision floating-point registers and up to 528 integer registers. There are 154 different instructions.

The reference [WG94] describes the SPARC-V9 standard by first defining some terms in order to provide a common language with the reader. It then goes on to broadly define two units, an integer and a floating point unit. This is followed by a definition of the operations on the architecture, the data and instruction formats it uses, the registers that have to be present and the behavior of instructions and traps, as well as the memory model.

All this explanation is done with as little detail as possible. Arithmetic operations are not defined in any detail, other than saying that they are there; if something causes a state change in a register, the exact mechanism of how the state is changed is not mentioned. Take, for example, the case of memory access<sup>1</sup>. Instead of describing each and every instruction for memory access and how they affect the state of the machine, memory access is described by lumping these instructions together and stating what kinds and sizes of transfers there are; from register to memory, from memory to register, in 8-bit, 16-bit, 32-bit and 64-bit sizes. There are no references, at this point, to the exact format of each instruction, its exact operation or possible side-effects.

More rigorous definitions come with the appendices, with their sets of norms. In them, each instructions is treated separately (or in small groups) in one to three pages. These pages specify the instructions' opcode, the suggested assembly syntax and a more detailed explanation of the behavior. The definition of the LDUW instruction<sup>2</sup>, for example, shows the opcode and suggested assembly language syntax for the command, specifies how the instruction works, indicating which registers are affected and even mentioning the required memory alignments. It ends with a list of the possible exceptions that this instruction might

<sup>&</sup>lt;sup>1</sup>Weaver and Germond, The Sparc Architecture Manual, Version 9, page17

<sup>&</sup>lt;sup>2</sup>Weaver and Germond, The SPARC Architecture Manual, Version 9, pages 175-176

cause. All in all, a much more detailed description of the instruction than that found in the body of the text.

It should be noted that, though the manual tries to be as detailed as possible, it never tries to tie the standard to any particular implementation. It suggests only the existence of two loosely defined units, the integer unit and the floating point unit mentioned earlier. These units are defined with respect to the expected state transformations, and no reference is made as to how these transformations are to be accomplished. Instructions, when grouped together at all, are done so solely on the basis of similar functionality. Conditional branches, for example, are grouped together since their behavior only varies in what condition is being tested.

Another aspect that the standard treats by omission is concurrency. It avoids tying in together the behavior of different instructions and, even within one instruction, avoids imposing any order on events. The same LDUW instruction described above, for example, makes no reference as to the order in which the operands that help in computing the effective address are returned; provided that the address is computed correctly, the order in which that is done is not important.

The only attempt at imposing some ordering in the model is made at the inter-instruction level. The standard states that any implementation should behave as if it were a serial model<sup>3</sup>. That is, any implementation should behave as if it executed in *program order*, completing an instruction before starting the next one. How this effect is to be achieved is left open.

So, though the manual does a good job in specifying the architecture, it has some weak points. First, it avoids several issues by describing things at the highest possible level and not getting into necessary detail. Second, it avoids tying in parts of the architecture, unless absolutely necessary. Finally, its use of the English language, though useful for gaining an overall understanding of the model, leaves some details unanswered and provides potential for misinterpretation.

## 1.2 The Rapide Prototyping Language

In order to satisfactorily implement the executable standard, the language used has to have several important characteristics. First, it should have mechanisms that allow abstraction and encapsulation, so that the user does not have to worry about implementation details. Second, it should be executable so that it is easy to simulate the model in order to verify its correctness and functionality. Finally, it should allow behavioral modeling, since this is how the standard defines the instruction set architecture and avoids implementation-dependent issues. Rapide-1.0 satisfies all these requirements.

Rapide is a programming language framework designed with the objective of making it easy and fast to build prototypes of distributed systems. It is an *event-driven* simulation language with constructs that facilitate the description of concurrency and timing. Among its features there are such object-oriented paradigms as inheritance and opera-

<sup>&</sup>lt;sup>3</sup>Weaver and Germond, The SPARC Architecture Manual, implementation note, page 61

tor overloading. Rapide consists of four sublanguages: types, constraints, executable and architecture[Tea94d, Tea94c, Tea94b, Tea94a].

A Rapide model consists of a set of *modules* connected by an *architecture* description. Each module has an interface and a body. The interface defines the type of the object, specifying how an object of that type communicates with the rest of the world. The body of a module is specified by module generators, which are pieces of Rapide code implementing the actual behavior of the module. An architecture connects several modules together to form either a model or, in a hierarchical manner, another higher-level module.

Models written in Rapide can be compiled and executed. Part of the model construction consists of defining event-generating *actions*. When these actions are triggered, they generate events which can then be used to trigger other actions, thus executing a simulation. It is important to note at this point that, in reality, patterns of events are used to trigger actions, allowing for very complex designs. Rapide simulations also use Fidge-Mattern vectors[Fid91, Mat88] in order to collect dependency and causality information between events.

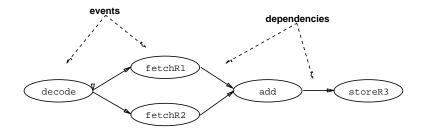

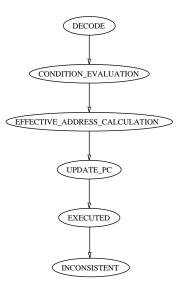

The result of executing a model is a file containing a set of events and dependency relations between them. This simulation output, also known as a *partial-order event set* (*poset*), can be represented as a directed acyclic graph, where each node corresponds to an event and each directed edge represents a causality relationship between the nodes. For example, figure 1.1 shows a possible result of the simulation of an ADD instruction using a Rapide model. In the figure, each ellipse corresponds to an event while the arrows indicate dependency relations between them. This example shows that an ADD operation consists of several events: decoding the instruction, fetching the data from the register set, adding the operands, and storing the result in the appropriate register. Notice that the poset shows no ordering relationship between the two operand fetches; they can be executed in any relative order, even in parallel. All it shows is that the addition operation requires two operands which must be be obtained before the sum can be computed.

Thus, a poset contains more information than the traditional linear traces provided by most simulators. Actually, it can be said that a poset is a compact representation for *all* valid linear traces corresponding to a simulation. In figure 1.1, for example, the poset represents two possible linear traces: *decode*, *fetchR1*, *fetchR2*, *add*, *storeR3* and *decode*, *fetchR2*, *fetchR1*, *add*, *storeR3*. A poset with *n* events may correspond to a set of up to *n*! equivalent linear traces.

There are currently several tools available for analyzing posets. The two most useful ones are, without a doubt, the partial order browser (pob) and the Rapide animator (raptor). The **pob** allows one to display and analyze the poset interactively. One can easily rearrange how the nodes are displayed, trace the dependency chain of an event, inspect the parameters of a node and much more. The other tool, **raptor**, allows one to get an animation of the simulation and observe the event executions. This makes it a very good tool for answering the question of *what* happened, while the **pob** is more suited for explaining *why* things happened.

Up to now we have described the main characteristics of Rapide as a language for building prototypes. There are two other features of the language, that make it well-suited

Figure 1.1: Sample resulting poset

for describing instruction set architectures and aiding in design verification: *constraints* and *maps*. These, as the reader will see, are fundamental in making Rapide an useful language for simulation and verification.

A constraint is a description of some behavior, but not its implementation. It describes what one expects to see in a simulation (or maybe what one never wants to see) but does not enforce it to happen. It works as a checker, informing the user of when the behavior deviates from the one specified in the constraint. With Rapide's pattern language, it is possible to describe complex event patterns that one wants to observe. For example,

> **match** ( (?addr in SPARCint\_t, ?val in ReadWriteReg\_t) Write(?addr, ?val) -> Read(?addr, ?val)  $\land (\sim *) \land (\sim *);$

is a Rapide constraint specifying register file coherence. It states that when one reads a register, the value returned should be the same as the the last value stored in that register.

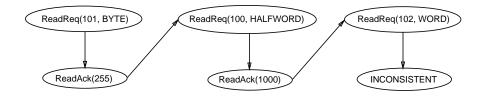

One very nice feature of Rapide is that constraint verification is automatic. During a Rapide simulation, new events are continually being checked against the constraints. If some event causes a pattern to match a "never" constraint or not match an "always" constraint, a *constraint violation* event<sup>4</sup> is generated. Using the **pob** tool described earlier, it is very easy to locate these violations and trace them back to their cause. Figure 1.2 shows such a case, corresponding to the constraint described above. The parameters shown for each event are, in order, the register address and the value stored there. The value returned by the second read to register 16 (0xFF) is different than the one last stored on that register (0xAA), so the *inconsistent* event is generated.

Mapping is the second feature of Rapide that makes it a very useful language for verifying conformance to a standard. As was mentioned earlier, the main use of this model is as a standard for design verification. When actual implementations are coded, it should be possible for them to be compared to this model to see if they do indeed conform to the SPARC-V9 standard by obeying the constraints. To do so, it is necessary to be able to get the poset (or linear trace) generated by some other model, and see if it is a valid poset for a SPARC-V9 implementation.

<sup>&</sup>lt;sup>4</sup>Constraint violation events sometimes are also called *inconsistent* events

Figure 1.2: Poset indicating a constraint violation

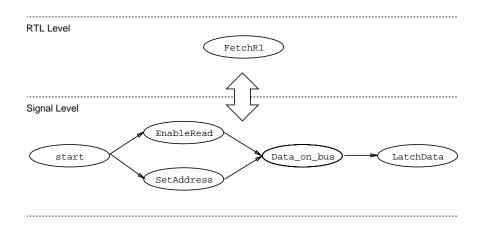

The one problem with this approach is that there might not be a one-to-one correspondence between the events in the implementation and the ones described in the reference model. For example, the implementation being tested might be designed at the gate level, while the model is written at the register transfer level.

Rapide provides a mechanism for dealing with this kind of problem, known as *mapping*. As can be seen in figure 1.3, mapping is a translation of a sequence of events and patterns in one domain to an equivalent event or pattern in another. In this way, a detailed model can be written for a specific implementation, along with a map that would show how the actions in this implementation correspond to actions in the standard. The implementation being verified can then be executed and the resulting poset automatically compared with the reference model.

Constraints and maps make Rapide well-suited for the construction of models for design verification. The ease with which one can describe constraints and the powerful pattern language make it simple to build complex rules. The executability of the model allows one to verify its correctness automatically. Finally, mapping makes it very easy to get an actual implementation and test its behavior.

Figure 1.3: Example of mapping

# Chapter 2

# The Model

## 2.1 Objectives

Before describing an approach to implementing the SPARC-V9 standard it is necessary to define what the desired characteristics of the model are. By describing what is expected of the final model, these characteristics serve as guidelines for the actual implementation of the standard.

In order to determine what are the model's desired characteristics, it is necessary to understand what is its intended use. Since the model is to be an executable formal specification of an instruction set architecture standard, it has to serve two different purposes: it is a *reference* source, and a *template* against which actual implementations are compared. As a reference source, it is used to explain what makes up the system and how it works. In order to do that it should provide a clear and complete description of what the architecture does so as to leave no room for doubt. As a template, it should simplify the comparison process to actual implementations.

In order to efficiently perform these functions, the model should have the following characteristics:

- $\bullet$  correctness

- completeness

- clarity

- precision

- executability

- implementation-independence

*Correctness* is what assures the user that whatever is seen in the model should actually be there. If something is present in the model, it should correspond to an actual constraint or specification in the English language description. Care should be taken to avoid over-specifying the standard by adding restrictions that are not present in the original documentation.

Completeness guarantees that everything that is in the architecture specification is also in the model. Completeness is, in a way, the dual of correctness. While the latter states that if something is in the model it should also be in the manual, the former states the opposite: if it is in the manual, it should also be in the model. This is, of course, a necessary characteristic of any model, because if some part of the specification is left out, it cannot be said that the model corresponds to the standard.

*Clarity* is another fundamental characteristic of the model, since it is to be used as a reference source, both in the source and executable code format. The standard should define the operations of the system not only correctly, but also in an easy to understand fashion.

*Precision* is another of our requirements. While clarity is concerned with how easy it is to read and understand the code and/or simulation results, precision has to do with how well-specified the description is. The manual was written in English, a natural language which allows for misinterpretations and ambiguities. A formal specification should not allow this to happen and must, by necessity, be precise and exact in its statements. Precision should not be confused with determinism; the latter is an implication that the model should always behave in a specific way, while the former just implies that the description should be unequivocal. Thus, it is possible to have a precise (well-defined and understood) construct that is non-deterministic (may take one of several possible behaviors, without the reader being able to determine which beforehand).

*Executability* is a desired characteristic of the model that adds a totally new dimension to it. By making the model executable it is possible to use it as an on-line tool for queries about the behavior and functionality of the instruction set architecture. It also allows one to have animations of the model's behavior that make it easier to grasp some concepts, and trace executions in order to get the order of events that led to an unexpected (or maybe expected) result.

Implementation-independence is, perhaps, the most important characteristic of the model. This comes directly from the manual, which makes no mention of hardware implementation details. It does not imply in any way that an implementation of the architecture should be pipelined, superscalar or anything; it just presents information on how the state changes in response to specific input to the system. This lack of restrictions as to how actual implementations of the architecture should behave is an intrinsic characteristic of the standard and should be preserved, which makes it necessary for the reference model to be flexible enough so as not to restrict all possible architectural variations one might find in an implementation.

The list of characteristics defined above describe what is expected of the Rapide-1.0 model of the SPARC-V9 instruction set architecture. It is necessary for the model to have all these characteristics, in order to be an adequate tool for answering questions about the standard. This implies that these characteristics should serve as guidelines for how the model is to be built. The next section describes an approach to building the model based on these desired characteristics.

## 2.2 Approach

In the previous section we defined several characteristics that the model must have in order to be an adequate tool for answering questions about the standard. In this section we present an approach to specifying the SPARC-V9 standard using Rapide-1.0 that, we hope, will fulfill all these requirements. These characteristics will be tackled, one at a time, with methods and solutions being proposed for obtaining the desired goal.

There is, unfortunately, no simple method for guaranteeing completeness and correctness. The only way to attain this goal is by careful programming, attention to detail and extensive testing. There are many software engineering techniques that are of aid in attaining this goal, such as top-down design, modularity of all the model's components, object-oriented techniques, and well-defined interfaces for the several components of the model.

Clarity, in this report's context, means the ability to make the source code readable and the simulation results simple to understand. To attain this goal there are several orthogonal approaches:

- Model decomposition: The first thing that can be done is to decompose the model into several components, each dealing with a different aspect of the standard. This will break up the model into several small and less complex units which can be dealt with independently. Since each component can then be studied in isolation, the amount of information that has to be absorbed at a time by the user is much smaller. Rapide has characteristics that make it suitable for this decomposition approach. Its type language[Tea94d] allows not only for the definition of components with well defined interfaces, but also the decoupling of the interface from the implementation of the component's behavior. The issue, then, is how to break down the model. In section 2.4 the suggested decomposition of the model into its constituent components is discussed in more detail.

- Uniform coding style: The second approach to dealing with readability is writing the source code in a clear, consistent and uniform style. Such a commonality in coding simplifies the task of understanding the program, since several important attributes of the source code will not change. The way to do this is by coming up with a series of guidelines for writing the code to give it a uniform look. Such guidelines would deal with several aspects of code writing like naming conventions, templates for common pieces of code and the organization of the code itself. Guidelines are presented in appendix A.

- Library of basic types: A third way to make the code easier to understand is to define a series of basic, well-understood types that can be shared by all the components. These basic types, implementing things like registers, stacks and 64-bit integers will make the code simpler, since it will not be necessary to reinvent them for each component in which they will be used. Another advantage of using this approach is that it adds another level of abstraction to the model itself, freeing the user from having

to worry about details such as how a register is implemented. Section 2.3 suggests a collection of such basic types and presents their interfaces.

It is interesting to note that all three of the above suggestions do more than just improve the clarity. Decomposition, abstraction through the use of basic types and uniformity of code also simplify testing and make it easier to build correct programs.

Precision, as was defined earlier, is intended so as to avoid misinterpretations and ambiguities in understanding the architecture. Most of these arise out of the fact that English, the language used to describe the architecture, is naturally ambiguous. By using a formal specification language such as Rapide-1.0, this requirement is fulfilled automatically. Rapide is completely specified and its constructs have well-defined meanings, so these ambiguities should not appear. Rapide also has the advantage that it allows non-determinism in its constructs, so that any *intentional* non-determinism of the model can be easily implemented.

Executability was another required characteristic of the model, since that would simplify testing of the model for correctness and completeness, as well as provide, through simulation results, a new way to analyze and understand the model. Fortunately, the Rapide specification language comes with tools for compiling and analyzing Rapide models. In order to make the model executable, then, all that is necessary is to construct a top-level architecture connecting all the components of the model and then compile it.

The final, and probably most important characteristic of the model should be implementation-independence. The instruction set architecture manual attains this goal by avoiding overspecifying. Whenever possible, it describes the behavior of some part of the architecture without connecting it in any way to the rest of the standard. The same thing should be done for the executable model. When defining the top-level architecture connecting all the components, care should be taken to avoid tying the model down to a specific implementation. There are many ways that this can be done such as, for example, using generic broadcast buses for communication between the components. By making this architecture as generic as possible, it is possible to avoid adding constraints to the model that were not in the original instruction set architecture.

In order for the model to be satisfactory it has to have the characteristics mentioned in the previous section: correctness, completeness, clarity, precision, executability and implementation-independence. These characteristics define the basic approach to building the model. These involve guidelines for coding, the use of a set of basic types to add a level of abstraction to the model, the break down of the model into several distinct components and the definition of an architecture loosely connecting them. The model should be coded in Rapide, which provides constructs and mechanisms for implementing all these requirements, as well as adding precision and executability.

The next three sections explain in some more detail some of the concepts described in this suggested approach. Section 2.3 describes the basic types used as building blocks for the model, while section 2.4 defines the components that make up the model. Finally, section 2.5 describes the architecture connecting the components in order to form the complete model itself.

## 2.3 Basic Type Set

A basic type set is a collection of types implementing objects with a desired functionality, that serve as building blocks for building more complex models. From the discussion in the previous section, it should be obvious that there are several advantages in using a basic type set. First of all, they provide basic blocks which can be reused throughout the model, thus saving on development time. Second, they make the code more uniform and thus improve its clarity and precision. Third, they provide a layer of abstraction, freeing the user and/or developer from having to worry about low-level implementation details. These are all desired characteristics of the SPARC-V9 model, and using a basic type set in the model's development is, thus, very useful.

Earlier on it was mentioned that Rapide has the necessary object-oriented paradigms, such as interface/implementation isolation and inheritance. Together with Rapide's behavioral constraint constructs, these facilities make it easy to build basic types with well defined behavior. The question left to be answered is, then, what these basic types should be.

The purpose of the basic type set is to provide the model designer with a homogeneous and consistent collection of types that one can use to build the model. To be useful, this set of basic types must have several properties. First, it must provide the desired level of abstraction so that the designer is not bogged down with details. Second, it must contain type definitions that correspond to hardware entities described in the manual. Finally, it must contain a big enough variety of types so that the user does not have to build new ones, possibly adding errors, just so as to complete the set of useful types.

Reading the SPARC-V9 standard[WG94], one notices that there is only one type of structure defined in the whole text: registers. To be precise, most of the document consists either of register definitions or descriptions of how instructions affect them. This makes a register the natural candidate for the starting point of the type set.

All these registers are not equal. Not only do they vary in size, they also differ in what operations may be performed on them. Some registers, for example, can only be read, while others can also be written to. There are also registers that store data with a specific meaning, such as the integer registers and the floating point registers. This variety suggests that it would be useful to list the main characteristics of each register and use that to group similar registers together. The resulting list is shown in table 2.1, with each group of similar registers separated by horizontal lines.

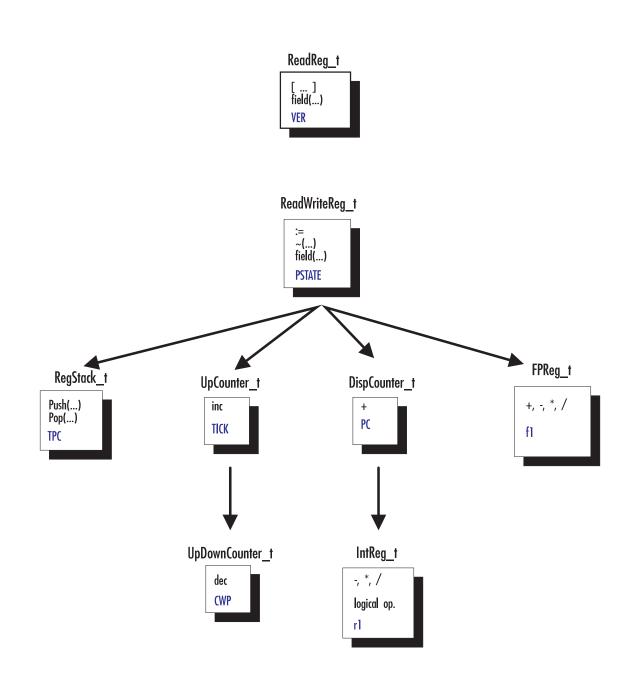

Table 2.1 suggests that an appropriate approach would be the creation of a register type for each group. Since all groups share some characteristics, the best way to represent them is as a tree, with the root consisting of a base type. New types are derived from the base type by adding new functionality to the type interface. Figure 2.1 shows the resulting type hierarchy. Each box has the type name on top. Inside the box can be found some sample functions and an example of a SPARC register of that type. Arrows go from a supertype to its derived subtype. As can be seen, **ReadReg\_t** is the only type that is not part of the hierarchy.

In defining the several register types some conventions have been observed. They are:

| Name           | Size | READ/WRITE          | Operations                |

|----------------|------|---------------------|---------------------------|

| r0r527         | 64   | RW                  | arithmetic & logic        |

| f0f31          | 64   | RW                  | floating point arithmetic |

| PC             | 64   | RW                  | sign-extended addition    |

| nPC            | 64   | $\operatorname{RW}$ | sign-extended addition    |

| Υ              | 64   | RW                  |                           |

| PSTATE         | 10   | $\operatorname{RW}$ |                           |

| PIL            | 4    | $\operatorname{RW}$ |                           |

| TBA            | 64   | $\operatorname{RW}$ |                           |

| $\mathbf{CCR}$ | 8    | $\operatorname{RW}$ |                           |

| FPRS           | 3    | $\operatorname{RW}$ |                           |

| FPSR           | 64   | $\operatorname{RW}$ |                           |

| WSTATE         | 6    | $\operatorname{RW}$ |                           |

| ASI            | 8    | $\operatorname{RW}$ |                           |

| TICK           | 64   | $\operatorname{RW}$ | increment                 |

| TPC            | 64   | $\operatorname{RW}$ | push, pop                 |

| TNPC           | 64   | $\operatorname{RW}$ | push, pop                 |

| TSTATE         | 64   | $\operatorname{RW}$ | push, pop                 |

| ΤТ             | 64   | $\operatorname{RW}$ | push, pop                 |

| VER            | 64   | R                   |                           |

| CWP            | 5    | $\operatorname{RW}$ | increment, decrement      |

| CANSAVE        | 5    | $\operatorname{RW}$ | increment, decrement      |

| CANRESTORE     | 5    | $\operatorname{RW}$ | increment, decrement      |

| OTHERWIN       | 5    | $\operatorname{RW}$ | increment, decrement      |

| CLEANWIN       | 5    | $\operatorname{RW}$ | increment, decrement      |

| TL             | 5    | RW                  | increment, decrement      |

Table 2.1: SPARC-V9 register set characteristics

| Function | Description                                    |

|----------|------------------------------------------------|

| []       | Returns the bit value stored at the position   |

|          | specified by the parameter.                    |

| field    | Returns the field value stored at the position |

|          | specified by the parameters.                   |

| regsize  | Returns the size of the register.              |

| intval   | Returns the integer value of the register.     |

| sform    | Returns the contents of the register in hex    |

|          | form.                                          |

Table 2.2: Function description for ReadReg\_t

- Bits in a register are ordered from least significant (LSB) to most significant (MSB) in increasing order. The first bit has the index 0.

- Fields are referred to by providing two indices, *index1* and *index2*. The first index is the position in the register of the most significant bit of the field, while the second index is the position of the least significant bit.

The following is the description of the types presented in figure 2.1. Each entry gives a brief description of what the type is like, what is its intended use, and a table with the *added* functionality of each type. We follow the convention that all type names end with ' $_t$ '.

One thing that will be noticed in the description is that most of the types have an **intval** function. This function returns an integer representation of the register's contents and its intended use is in debugging, solely as a means to present the value in a form that the programmer can easily read.

The basic types are:

- **ReadReg\_t:** This is a read-only register type. It describes the most basic of all register types. As can be seen in figure 2.1, it is the only type among the basic types that is not part of the hierarchy. This happens because, being the only type that cannot be written to, it is inherently different from all other types. It was designed specifically for implementing the VER register. Table 2.2 shows the associated functions.

- **ReadWriteReg\_t:** This is the base type for all subsequent types. Its form is very similar to **ReadReg\_t**, except that it has been structured so as to allow writing to it. The associated functions are shown in table 2.3. It is intended for the implementation of the basic register structures like PSTATE.

- UpCounter\_t: This type is a subtype of ReadWriteReg\_t. It is the first type in which the content of the register has a meaning other than just a collection of bits. In this case, the register type is supposed to store an unsigned integer that can be

Figure 2.1: Type hierarchy tree for register types

| Function | Description                                  |

|----------|----------------------------------------------|

| []       | Returns the bit referenced by the parameter. |

| field    | Returns the field referenced by the parame-  |

|          | ters.                                        |

| ~        | Toggles all bits in register.                |

| ##       | Register concatenation operator.             |

| :=       | Assigns a value to the register.             |

| regsize  | Returns the size of the register.            |

| intval   | Returns the integer value of the register.   |

| sform    | Returns the contents of the register in hex  |

|          | form.                                        |

Table 2.3: Function description for ReadWriteReg\_t

| Function | Description                          |

|----------|--------------------------------------|

| Reset    | Sets the register content to 0.      |

| inc      | Adds 1 to the value of the register. |

Table 2.4: Added functions for UpCounter\_t

incremented. There is no provision for overflow; when the maximum value is exceeded the counter wraps around to 0. It was specifically designed for implementing the TICK register.

- UpDownCounter\_t: This type is almost the same as UpCounter\_t, of which it is a subtype. Its functionality is the same, except that it counts both up and down. Again, there is no overflow or underflow; the counter just wraps around. Table 2.5 shows the added functions. It may be used to implement CWP, CANSAVE and the other registers related to register-window control.

- **RegStack\_t:** This type is a special type of **ReadWriteReg\_t**. As the name implies, it is a stack. Writing to it does not make the previous value disappear, it only pushes it further into the stack. This type was created for implementing the stack-like structures used in trap handling, such as the TT and TPC registers.

| Function | Description                                  |

|----------|----------------------------------------------|

| dec      | Decreases the value stored in the counter by |

|          | 1.                                           |

Table 2.5: Added functions for UpDownCounter\_t

| Function | Description                                             |  |

|----------|---------------------------------------------------------|--|

| push     | Adds an element to the top of the stack.                |  |

| рор      | Removes the top element from the stack.                 |  |

| top      | op Returns the value of the top element from the stack. |  |

Table 2.6: Added functions for RegStack\_t

| Function | Description                                   |

|----------|-----------------------------------------------|

| +        | Adds a sign-extended value to the contents of |

|          | the register.                                 |

Table 2.7: Added functions for DispCounter\_t

- **DispCounter\_t:** This type stores an unsigned integer to which a displacement value may be added. This displacement value is supposed to be in two's complement format and is sign-extended for the operation. Note that there is no overflow or underflow, just wraparound. It is intended for the implementation of PC and nPC.

- **SPARCint\_t:** This type is the subtype of the **ReadWriteReg\_t** type, and implements a 64-bit integer. Its intended use is in the 64-bit integer arithmetic module. As such, you can perform all integer arithmetic functions with them, as well as the standard logical ones. All arithmetic operations assume that the integers are in two's complement format.

- **SPARCreal\_t:** This is the subtype of **ReadWriteReg\_t** intended for the implementation of the floating point unit. It is analogous to the **SPARCint\_t** type, but deals with floating point arithmetic instead. It follows the IEEE standard for floating point representation and operations mentioned in section 2.4. The basic arithmetic and comparison operations are provided.

The types presented above are all variations of the basic concept of a register. They vary in the functionality provided, which in turn is a result of the functionality required of the registers defined in the SPARC-V9 instruction set architecture manual. This one-to-one correspondence ensures that the basic type set presented here is more than adequate for building the SPARC-V9 model with the desired level of abstraction. Appendix B presents the code for the basic type interfaces.

#### 2.4 Components

As suggested in section 2.2, it is interesting to break down the model into several distinct components, each one dealing with a different aspect of the instruction set architecture.

| Function             | Description                                |

|----------------------|--------------------------------------------|

| &                    | Bit-wise logical and.                      |

| or                   | Bit-wise logical or.                       |

| xor                  | Bit-wise logical <i>xor</i> .              |

| neg                  | Two's complement negation.                 |

| +                    | Two's complement integer addition.         |

| -                    | Two's complement integer subtraction.      |

| *                    | Two's complement integer multiplication.   |

| /                    | Two's complement integer division.         |

| mod                  | Two's complement integer remainder.        |

| $^{\mathrm{shr}}$    | Shift right operator.                      |

| $\operatorname{shl}$ | Shift left operator.                       |

| ashiftr              | arithmetic shift right operator.           |

| =                    | Equality comparison operator.              |

| /=                   | Inequality comparison operator.            |

| >                    | Greater-than comparison operator.          |

| <                    | Smaller-than comparison operator.          |

| >=                   | Greater-than-or-equal comparison operator. |

| <=                   | Smaller-than-or-equal comparison operator. |

Table 2.8: Added functions for SPARCint\_t

| Function | Description                                |

|----------|--------------------------------------------|

| +        | Floating point addition.                   |

| -        | Floating point subtraction.                |

| *        | Floating point multiplication.             |

| /        | Floating point division.                   |

| sqrt     | Floating point square root.                |

| =        | Equality comparison operator.              |

| /=       | Inequality comparison operator.            |

| >        | Greater-than comparison operator.          |

| <        | Smaller-than comparison operator.          |

| >=       | Greater-than-or-equal comparison operator. |

| <=       | Smaller-than-or-equal comparison operator. |

Table 2.9: Added functions for SPARCReal\_t

This decomposition allows one to study, debug and test the model one piece at a time, which reduces the complexity of the problem and improves the model's correctness. It just remains to be decided how this decomposition should happen.

One problem is that there are many possible decompositions of the model, all equally valid in that they result in a working model. Choosing between them, then, is a matter of functionality, i.e., finding an organization that reflects the kind of information one wishes to convey.

A first step in deciding how to decompose the units is to define what are the main characteristics of any component. Basically, components can be fit into two broad categories: *state units* and *execution units*. State units are those that consist of sets of registers that store the state of the system, such as the integer registers, the program counter, etc. The execution units are those responsible for actually performing operations that cause the state of the model to change.

The SPARC-V9 architecture defines both state that has to be stored and operations that change the state. Our suggested approach is, therefore, to divide the system into both state and execution units. Having just one state unit and one execution unit, though, still result in unmanageable chunks of code, so further decomposition is necessary. Here again the English manual suggest a good approach; in its description of the opcodes, it groups similar instructions together and we will borrow that concept.

This suggests the following decomposition for the units (all references are to chapter 5 of [WG94]):

- State units decomposition:

- control/status registers: This unit contains all registers associated with processor status and control such as the program counter, nPC, PSTATE, etc. Most, but not all, of the control/status registers would be placed here. Those that are intimately associated with some specific function, such as the register window control registers, will be placed elsewhere.

- integer register set: This unit contains the integer register set, as well as the register window state registers defined in section 5.2.10 of [WG94]. Since the actual size of the integer register set is implementation-dependent, the suggested approach is to use a parameterized module generator with the desired number of register windows as the parameter. This way, any possible integer register set implementation can easily be created. The behavior of this unit is quite simple, consisting exclusively of actions for reading and writing its registers.

- floating point register set: This register set contains the 32 single-precision / 32 double-precision / 16 quad-precision floating point registers defined in section 5.1.4 of [WG94] Care should be taken to implement the overlapping, or aliasing, of registers defined by the standard. Like the previous two register sets, the only actions associated with this unit consists of either reading or writing to it.

- Execution units decomposition:

- instruction fetch: This unit is responsible for triggering the execution of an instruction. When activated, either by a *start* event<sup>1</sup> or by the completion of the last operation, it accesses the program counter and initiates the fetching of the next opcode from the outside environment. Once the opcode is obtained, it is made available to all execution units in the model.

- **memory access:** This unit, as the name implies, is responsible for controlling the communication between the SPARC CPU and the environment. Like the instruction fetch unit described before, it is not an opcode executing unit. Instead, it provides a service for all other execution units, through which they can access the main memory.

- interrupt/trap handling: This is another unit that is responsible for treating two distinct, but related types of events. As an interrupt handler, it observes events coming from the CPU environment (such as a RESET) and takes the appropriate action. As a trap handler, it deals with all internally generated traps (such as overflow, software reset, etc.).

- data movement: This unit is responsible for all opcodes related to moving data from one place to another within the architecture. It deals with such simple moves as from one register to another, as well as with loads/stores from/to main memory. In order to perform its function it will have to work closely with the memory access unit.

- integer logic and arithmetic: This unit implements a 64-bit arithmetic and logic unit. It performs all the integer operations defined on the standard, on both 32 and 64-bit data. It does not contain any registers for storing data, using instead immediate data passed along with the opcode and/or data from the integer register set.

- floating point arithmetic: This unit is analogous to the integer logic and arithmetic unit, the difference being that it operates on the floating point register set. It implements operations such as FADD, FMUL and FDIV, and would consist of a 128/64/32 (quad, double and single precision, respectively) bit floating point ALU conforming to the IEEE 754 binary floating-point arithmetic standard[IEE85].

- branch control: The branch control unit deals with all program flow related opcodes. As such it processes commands like JMPL, BPcc and RETURN. It must, by necessity, be able to access and change the value of nPC.

- privileged operations: This is the unit that deals with all the privileged instructions. These instructions usually consists of reading and/or writing a set of control registers that change the state of the CPU. Some examples of privileged operations are RDPR, RDTICK and LDDA.

- miscellaneous: This unit would group together any opcodes that do not fit into any of the units above. It could, for example, deal with such opcodes as MEMBAR, SIGM and WRCCR.

<sup>&</sup>lt;sup>1</sup>Start events are events that are automatically generated in a Rapide program when an object is created. They are used, as the name suggests, to start the simulation

The memory access unit and the instruction fetch unit are special, in that they are not directly related to any opcodes, but rather serve as *auxiliary* execution units for the model. Their job is to isolate the model from the environment and provide it with the instructions for execution. The rest of the execution units, on the other hand, are directly connected to SPARC-V9 opcodes. Each opcode is processed totally by one of these execution units (which may have to access some or all of the state units in order to do this), and thus, there is a one-to-one correspondence between execution units and opcodes. This is shown in table 2.10.

It should be emphasized at this point that this is a suggested organization, not a mandatory one. Many other equally good arrangements are possible. For example, both the memory control unit and the interrupt/trap handling unit could be broken up into smaller independent units. Another possible approach would be not to isolate the state from the execution, but keep related operations and registers in the same unit (i.e., have the trap registers inside the trap handling unit).

## 2.5 Architecture

The previous section described the units that make up the model. The next and final step is to define an architecture connecting these modules. In this case, we follow the definition of architecture proposed in [LVM95], in that an architecture consists not only of components and their interconnections, but also includes protocols defining how these components communicate. This should provide a complete description of the instruction set architecture, not leaving any ambiguities.

The definition of the architecture is a crucial part of the model's design, since that is the point at which the model is usually bound to one specific implementation. In this case, it is desirable to make this binding as loose as possible, so that the model remains implementation-independent. The instruction set architecture manual achieves this goal by avoiding defining any binding architecture at all; instead it keeps the opcode definitions loosely coupled, describing how the architecture reacts to events without tying one event to another.

This approach is, unfortunately, not one that can be used in the definition of the model's architecture. One of the model's objectives is that it is to be used as an *executable* standard and to attain this objective an architecture must be completely specified. The challenge is, then to make this specification as flexible as possible.

The best way to attain this goal is by making the communication mechanism between modules as generic as possible. Instead of defining point-to-point communication between the components, broadcasting should be used. By defining several specialized broadcast channels to which a component can connect, an executable model can be built that retains most, if not all, of the intended implementation-independence and flexibility.

There are many possible such broadcast channel organizations, ranging from "one channel for everything" to the equivalent of point to point connections between modules. Neither of the extreme solutions are ideal: the former complicates the interface of the components,

| unit               | opcode                |                        |                        |                                       |  |

|--------------------|-----------------------|------------------------|------------------------|---------------------------------------|--|

|                    | ADD,                  | ADDcc,                 | ADDC,                  | ADDCcc,                               |  |

|                    | AND,                  | ANDcc,                 | ANDN,                  | ANDNcc,                               |  |

|                    | MULScc,               | MULX,                  | OR,                    | ORcc,                                 |  |

|                    | ORN,                  | ORNcc,                 | POPC,                  | SDIV,                                 |  |

|                    | SDIVcc,               | SDIVX,                 | SETHI,                 | SLL,                                  |  |

| Integer Arithmetic | SLLX,                 | SMUL,                  | SMULcc,                | SRA,                                  |  |

|                    | SRAX,                 | $\mathrm{SRL},$        | SRLX,                  | SUB,                                  |  |

|                    | SUBcc,                | $\operatorname{SUBC},$ | SUBCcc,                | TADDcc,                               |  |

|                    | TADDccTV,             | TSUBcc,                | TSUBccTV,              | UDIV,                                 |  |

|                    | UDIVcc,               | UMUL,                  | UMULcc,                | XNOR,                                 |  |

|                    | XNORcc,               | XOR,                   | XORcc                  |                                       |  |

| Branch Control     | BPcc,                 | Bicc,                  | BPr,                   | CALL,                                 |  |

|                    | FBfcc,                | FBPfcc,                | JMPL,                  | RETURN                                |  |

| FP Arithmetic      | FABS,                 | FADD,                  | FCMP,                  | FCMPE,                                |  |

|                    | FDIV,                 | FdMULq,                | FiTO(s,d,q),           | FsMULd,                               |  |

|                    | FSQRT,                | F(s,d,q)TOi,           |                        | FMUL,                                 |  |

|                    | FNEG,                 | F(s,d,q)TOx,           | FSUB,                  | FxTO(s,d,q),                          |  |

|                    | F(s,d,q)TO(s,d,q)     |                        |                        |                                       |  |

|                    | CASA,                 | CASXA,                 | FLUSHW,                | FMOV,                                 |  |

|                    | FMOVcc,               | FMOVr,                 | LDD,                   | LDDA,                                 |  |

|                    | LDDF,                 | IDDFA,                 | LDF,                   | LDFA,                                 |  |

|                    | LDFSR,                | LDQF,                  | LDQFA,                 | LDSB,                                 |  |

| Data Movement      | LDSBA,                | LDSH,                  | LDSHA,                 | LDSTUB,                               |  |

|                    | LDSTUBA,              | LDSW,                  | LDSWA,                 | LDUB,                                 |  |

|                    | LDUBA,                | LDUH,                  | LDUHA,                 | LDUW,                                 |  |

|                    | LDUWA,                | LDX,                   | LDXA,                  | LDXFSR,                               |  |

|                    | MOV,                  | MOVr,                  | MOVcc,                 | RDASI,                                |  |

|                    | RDASR,                | RDCCR,                 | RDFPRS,                | RDPC,                                 |  |

|                    | RESTORE,              | $\mathrm{RDY},$        | RDTICK,                | SAVE,                                 |  |

|                    | $\operatorname{STD},$ | STDA,                  | $\mathrm{STDF},$       | STDFA,                                |  |

|                    | STB,                  | STBA,                  | STF,                   | STFA,                                 |  |

|                    | $\mathbf{STFSR},$     | STH,                   | STHA,                  | $\operatorname{ST}\operatorname{QF},$ |  |

|                    | STQFA,                | STW,                   | $\operatorname{STWA},$ | STX,                                  |  |

|                    | STXA,                 | STXFSR,                | SWAP,                  | SWAPA,                                |  |

|                    | WRASI,                | WRASR,                 | WRCCR,                 | WRFPRS,                               |  |

|                    | WRPR,                 | WRY                    |                        |                                       |  |

| Miscellaneous      | FLUSH,                | IMPDEP1,               | IMPDEP2,               | MEMBAR,                               |  |

|                    | NOP,                  | SIGM,                  | STBAR                  |                                       |  |

| Priv. Operations   | SAVED                 | RDPR                   | PREFETCH,              | PREFETCHA,                            |  |

|                    | RESTORED              |                        |                        |                                       |  |

| Trap Handling      | DONE,                 | ILLTRAP,               | RETRY,                 | Tcc.                                  |  |

Table 2.10: Execution units and their related opcodes.

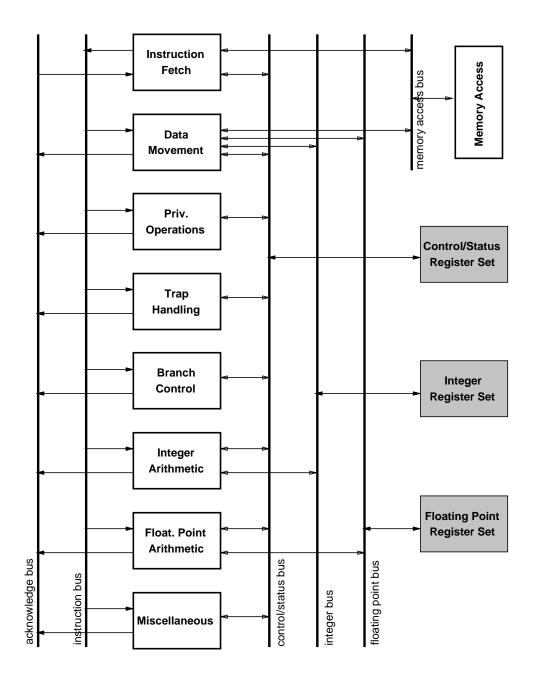

while the latter removes all flexibility from the model. Clearly, a middle-ground approach would be best. By keeping in mind that the model consists of execution units responsible for changing state and state units responsible exclusively for storing state, the authors considered the following bus partition to be adequate:

- **control/status bus:** Connects the control/status unit to all the execution units that might want to access it.

- **integer bus:** Connects the integer register set to all units that might want to access it.

- floating point bus: Connects the floating point unit to all units that might want to access it.

- **memory access bus:** Connects the memory access unit to all units that might want to access the main memory.

- instruction bus: Connects all units that might want to either issue or execute an instruction.

- acknowledge bus: Connects all units that might want to signal or be aware than an instruction has been executed.

This bus partition allows for a detailed enough description so that the model is manageable and understandable, while not adding any implementation dependence.

Having determined what the necessary buses are, the next step is to decide which components should be in the model. The suggested approach for its implementation in Rapide-1.0 is a minimalist one. There should be no more than one instance of each type of unit. One of each type of the units described in section 2.4 is necessary, otherwise it would not be possible to build the model. More than one would make some coordination effort between them necessary, and that would add unwanted implementation dependencies and constraints to the model.

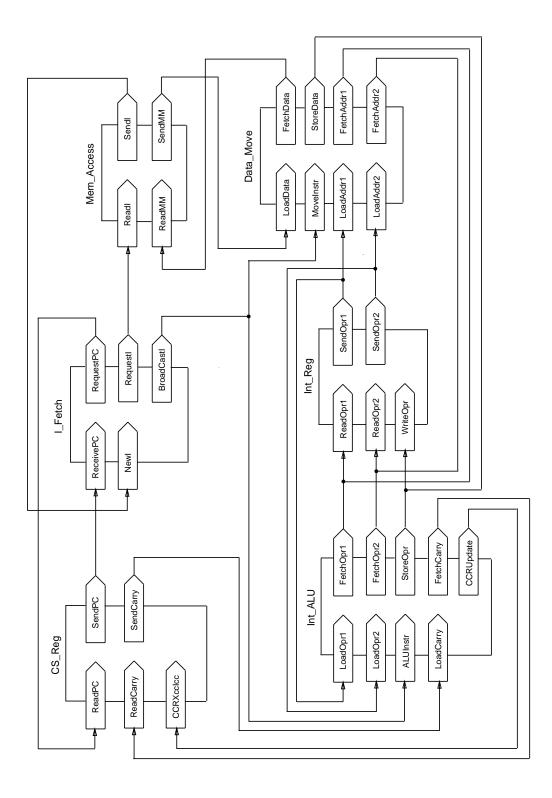

Figure 2.2 shows the architecture of the proposed system. The units are represented by rectangles, with the execution units being white while the state units are shaded gray. The vertical lines represent the communication buses described above, while the horizontal ones represent the connections between the units and the buses, with the arrows indicating the direction of the flow of information.

Once the components making up the model and the interconnection mechanism between them is defined, the next step is to define the protocol for the model's top-level behavior. This protocol describes how the model should deal with the instruction "fetch-and-execute" cycle, and should be generic enough so as to avoid adding any implementation dependencies. Based on the broadcasting principles and buses defined in the previous paragraphs, the behavior of the system is the following:

1. The instruction-fetch unit retrieves the current PC value from the control/status register set and uses that to issue a memory access request.

Figure 2.2: Simplified SPARC-V9 Architecture

- 2. The memory access unit performs the required access and returns the opcode to the instruction fetch unit.

- 3. The instruction fetch unit broadcasts the opcode to all execution units.

- 4. The execution unit that has this opcode in its domain decodes it and executes the required operation. This may involve exchanging information with the control/status register units and/or the integer and floating point register sets.

- 5. The execution unit signals the end of the opcode execution to the instruction fetch unit, indicating that a new instruction cycle may begin.

This protocol preserves implementation-independence by loosely binding the individual components' behaviors. The instruction fetch unit does not care where the instruction is going to, and the execution units do not care where it comes from or if any other unit is also processing it. This adds flexibility, in that it allows for the actual computation to be distributed in several different ways.

Another major characteristic of this model is that it is *sequential* in nature, just like the model described in in the instruction set architecture manual. This serialization, though, is done entirely in the instruction fetch unit and is invisible to any other component of the system. By changing the instruction fetch unit it is quite easy to create other implementations of the architecture, using a pipelined, superscalar or some other approach. Since this is all done inside the instruction fetch unit, it is transparent to anyone looking at the top-level model.

This chapter described what an implementation-independent model of the SPARC-V9 instruction set architecture should look like. It described the desired characteristics of such a model and how one should go about building a model that satisfies these requirements. It then described a basic type set to use as building blocks for constructing the model, as well as the major components that the model should have. Finally, it described an architecture for connecting these components in an implementation-independent way.

Rapide, as a prototyping and simulation language, has all the necessary constructs for implementing the model as described here. It allows the designer to break down the model into distinct components, connect them in the desired way and provides inheritance and polymorphism mechanisms for creating the basic types.

# Chapter 3

# Scaled-Down Rapide-0.2 Model

Before attempting to build the complete SPARC-V9 model, it is interesting to do a small scale experiment, in order to check the validity of the concepts presented in the previous chapter. This prototype can be used to test the broadcast-bus architecture concept, provide an estimate of its flexibility, and give an idea of what kind of results one can expect from such a model.

The language used for implementing this scaled-down version of the SPARC-V9 is Rapide-0.2[Bry92]. Rapide-0.2, a preliminary "proof of concept" version of Rapide. It was chosen because, at that time the model was built, Rapide-1.0 was still in its early design stages while the 0.2 compiler was complete and stable. Since both Rapide-0.2 and Rapide-1.0 share the same philosophy and language constructs, using the former to create this prototype in no way invalidates the result.

The rest of this chapter describes the scaled-down SPARC-V9 model. Section 3.1 describes the architecture of the model chosen for implementation, while sections 3.2 and 3.3 respectively describe the results of a simulation of a sequential and a pipelined implementation.

## 3.1 Model Architecture

The objective of this exercise was to build a prototype to test if the approach suggested in the previous chapter is valid. To do so, the model must satisfy two requirements. First, it has to be complete enough so that it can actually represent the SPARC-V9 architecture described in the preceding chapter. On the other hand, it has to be simple enough so that the designer can build it in a short amount of time. After all, the objective of this exercise is only to verify if the approach is feasible, not to construct a full implementation.

Clearly, these two requirements contradict each other; the former implies the use of as many components as possible (to closer approximate the suggested architecture), while the latter tries to minimize the number of units so as to keep the model simple. A compromise must be attained in order to satisfy both of these goals. The main characteristic of the suggested architecture is the principle of broadcasting instructions and request-acknowledge pairs through a set of buses. This implies that the prototype should have at least two units on the receiving end of any broadcast, otherwise the architecture would correspond to a point-to-point connection and the broadcasting feature would not be tested. This suggests that there should be at least two opcode execution units in the prototype, executing two distinct opcodes. The authors arbitrarily chose ADD and LOAD as the opcodes for testing.