# **AUTOMATIC SYNTHESIS OF GATE-LEVEL SPEED-INDEPENDENT CIRCUITS**

Peter A. Beerel Chris J. Myers Teresa H.-Y. Meng

Technical Report: CSL-TR-94-648

December, 1994

This research was supported in part by ARPA, contract DABT63-91-K-0002, the Center for Integrated Systems, Stanford University, and an NSF Fellowship.

# AUTOMATIC SYNTHESIS OF GATE-LEVEL SPEED-INDEPENDENT CIRCUITS

# Peter A. Beerel\*, Chris J. Myers, and Teresa H.-Y. Meng

# **Technical Report: CSL-TR-94-648**

December, 1994

Computer Systems Laboratory Departments of Electrical Engineering and Computer Science Stanford University Stanford, CA 943054055

# Abstract

This paper presents a CAD tool for the synthesis of robust asynchronous control circuits using limited-fanin basic gates such as AND gates, OR gates, and C-elements. The synthesized circuits are speed-independent; that is, they work correctly regardless of individual gate delays. Included in our synthesis procedure is an efficient procedure for logic optimizations using *observability don't cares* and *incremental verification*. We apply the procedure to a variety of specifications taken from industry and previously published examples and compare our speed-independent implementations to those generated using a non-speed-independent synthesis procedure included in Berkeley's SIS. Our implementations are not only more robust to delay variations since those produced by SIS rely on bounded delay lines to avoid circuit hazards but also are on average 13% faster with an area penalty of only 14%.

# Key Words and Phrases:

Computer-aided design, asynchronous circuit synthesis, gate-level speed-independent circuits, state graph specifications, standard C-implementations, hazard-preserving logic transformations, acknowledgement and monotonicity, binate covering, multi-level logic, conservative incremental verification, and observability don't cares.

<sup>\*</sup>Peter A. Beerel is now an affiliated with the EE-Systems Dept., University of Southern California, Los Angeles, CA 90089-2562

Copyright © 1994

Peter A. Beerel, Chris J. Myers, and Teresa H.-Y. Meng

# Contents

| 1 | Introduction                                                                                                                                                                                                        | 1                                                                     |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 2 | Specification and implementation         2.1 Stategraph         2.2 Circuit implementation                                                                                                                          | 2<br>2<br>3                                                           |

| 3 | The gate-level synthesis problem         3.1 Complex-gate implementations         3.2 Gate-level implementations         3.2.1 The request/acknowledge protocol         3.2.2 Acknowledgement and monotonicity      | 4<br>5<br>5<br>5                                                      |

| 4 | Standard C-implementation         4.1 Theory         4.1.1 Excitation and quiescent regions         4.1.2 Correct covers         4.2 Algorithms         4.2.1 General algorithm         4.2.2 Single-cube algorithm | 7<br>7<br>8<br>9<br>9<br>11                                           |

| 5 | Implementing region functions5.1 Acknowledgement wire forks5.2 Algorithm for repairing a decomposition                                                                                                              | <b>13</b><br>14<br>14                                                 |

| 6 | Logic optimizations         6.1 Removing redundant gate inputs         6.2 Sharing and merging gates         6.3 Signal network simplification         6.4 Inverter bubble shuffling                                | 17<br>17<br>17<br>17<br>17<br>18                                      |

| 7 | Performing logic transformations and optimizations         7.1 Overview.                                                                                                                                            | <b>18</b><br>18<br>19<br>19<br>20<br>20<br>21<br>21<br>21<br>22<br>22 |

| 8 | Results and conclusions         8.1 Breaking up complex and high-fanin gates         8.2 Comparison with SIS         8.3 Summary                                                                                    | 22<br>23<br>24<br>24                                                  |

| A | Definition of Correctness         A. 1 Complex-gate equivalence         A.2 Hazard-freedom                                                                                                                          | 28<br>28<br>28                                                        |

| B | <ul> <li>B Necessary and sufficient conditions for correctness</li> <li>B. 1 Formalization of monotonicity and acknowledgement</li></ul>                                                                            | 29<br>29<br>30                                                        |

| С | The cube approximation                                 | 30 |

|---|--------------------------------------------------------|----|

|   | C. 1 Mapping the cube approximation to a set of states | 31 |

|   | C.2 Required fanins and acknowledgement,               | 31 |

| D | Sufficient conditions for correctness                  | 32 |

| E | Proof of correctness                                   | 34 |

|   | E.1 Defining a cube approximation fixpoint             | 34 |

|   | E.2 Acknowledgement and stability                      | 35 |

|   | E.3 Final proof of our synthesis algorithm             | 35 |

# **1** Introduction

As competitive asynchronous chips gain attention [10, 15, 20, 31, 42, 47, 49], asynchronous design is increasingly being considered as a practical and efficient design alternative. Asynchronous designs do not require a global clock for synchronization. Instead, synchronization is event-driven that is transitions on wires act to request the start of a computation and acknowledge its completion. By removing the global clock, this design style has several advantages including absence of problems related to clock-skew, freedom from designing for worst-case delay, and automatic power-down of unused circuitry.

Speed-independent circuits are an attractive subclass of asynchronous circuits because they can tolerate delay variations resulting from variations in IC processing, temperature, and voltage. More precisely, these circuits work correctly regardless of the delays of individual gates, while assuming constant wire delays for multiple fanouts [39]. As a result, achieving speed-independence avoids the need for timing assumptions and delay lines that tend to increase area and delay while reducing the reliability of the circuit. This insensitivity to variation in gate delays also means that components within a speed-independent system can be replaced by faster components without needing to redesign any other part of the system. Moreover, speed-independent circuits can exhibit more concurrency than fundamental mode circuits [43, 48] which require that inputs change only after the entire circuit is guaranteed to be stable. Speed-independent circuits can also be easily verified [3, 18] and have a testability advantage-they are self-checking with respect to a broad class of multiple output stuck-at-faults [2].

Previously, automated synthesis of speed-independent circuits required complex-gates-every specified output signal was implemented with a single, possibly very complicated, atomic gate [12, 37]. Unfortunately, such circuits can be unreliable, since unmodeled glitches within the complex-gates may cause circuit malfunction. These unmodeled glitches are especially problematic in standard-cell and programmable gate-array implementations in which complex-gates are usually implemented with a collection of standard logic cells. A more reliable approach is to synthesize gate-level implementations comprised of only basic gates that can be easily incorporated into standard-cell and gate-array libraries.

To build gate-level speed-independent circuits, Martin and Burns add state variables to the specification to simplify all complex-gates to gates that exist in the gate library or can be reliably generated using a module generator [33]. Unfortunately, the addition of state variables often requires user intervention and some circuits require specialized gates which may not be suited for gate-array and standard-cell implementations. Nevertheless, this semi-automated method has been used to build many large custom designs including a sixteen-bit asynchronous microprocessor [34, 47].

Kishinevsky and Varshavsky proved that a gate-level speed-independent implementation can always be found for a limited class of specifications (Chapter 5 of [52]). They considered *distributive* specifications of autonomous circuits [38], which have no inputs. They proved that all such specifications can be implemented speed-independently using 2-input NAND gates. Their goal, however, was theoretical in nature and did not include practical considerations such as speed and area. As a result, their algorithm produces large, complex circuits because it unnecessarily adds many state variables to avoid hazards. In addition, since their circuits do not model inputs, their algorithm is restricted to circuits that do not exhibit conditional behavior modeled by input (environmental) choice.

Since then, there have been several works on synthesizing speed-independent circuits from specifications with choice to basic gates with unlimited fanin. First, in a preliminary version of this work [5], we developed an algorithm to generate unlimited-fanin gate-level speed-independent circuits from state graph (SG) specifications that can model input choice. Subsequently, K. Lin and C. Lin developed an algorithm transforming a free-choice signal transition graph (STG) into an unlimited-fanin gate-level speed-independent circuit [30]. In addition, Kondratyev et al. proposed a similar synthesis algorithm to our previous work [25]. Both the works of [30] and [25] do not address the problem of synthesis using limited-fanin gates and restrict the circuit's combinational blocks to two-level logic which may not be the optimal implementation. In addition, the theory in [25] is ambiguous, allowing some hazardous circuits to be synthesized. Fortunately, this ambiguity can be resolved with an amendment [24], making their theory essentially equivalent to our results presented in [5].

This paper describes a CAD tool for the synthesis of gate-level speed-independent circuits from a class of SG specifications that include input choice. Our synthesis procedure differs from those described in [30] and [25] in that it addresses synthesis using only limited-fanin gate libraries, and it is capable of using multi-level logic when necessary. Allowing multi-level implementations can increase gate sharing, reducing circuit area, and can shorten the critical path, increasing circuit speed.

The synthesis procedure has three steps. First, the procedure implements the circuit using a *standard Cimplementation* logic template. The procedure employs efficient *binate covering algorithms to* find the optimal circuit using this template. While this circuit often can be implemented with limited-fanin basic **gates**, larger or very concurrent specifications sometimes require using high-fahin and/or complex gates. Therefore, the second step of the procedure heuristically decomposes all high-fanin and/or complex gates into limited-fanin basic gates. This decomposition often requires the addition of connections between gates to remove any hazards caused by the added delay elements associated with the introduction of new internal signals. Third, the procedure applies a variety of logic optimizations that improve circuit area and delay.

Both the decomposition and logic optimization procedures explore logic transformations that are not guaranteed to preserve hazard-freedom. Hence, before accepting any logic transformation, the procedure verifies that the transformed circuit is hazard-free. Circuit verification has traditionally been computationally expensive, and our synthesis procedure may require hundreds of verification subtasks. Therefore, to reduce the complexity of the verification subtasks the procedure uses a logic transformation framework that utilizes *observability don't cares* (ODCs) and *incremental verification*. This framework dramatically reduces the amount of computationally feasible.

We present the area and performance results of the synthesized circuits for all benchmark specifications given in [27]. Our tool successfully synthesized all circuits with limited-fanin (4-input or less) basic gates. We compare our synthesized circuits with their non-speed-independent counterparts synthesized by the asynchronous circuit synthesis package provided in Berkeley's SIS, in which bounded delay lines are used to remove circuit hazards. The comparison shows that our circuits are on average 14% larger but 13% faster. These results suggest that while our constrained logic synthesis strategy to achieve speed-independence may cost marginally in area, the lack of bounded delay lines often yields faster, more robust circuits than can otherwise be achieved.

# 2 Specification and implementation

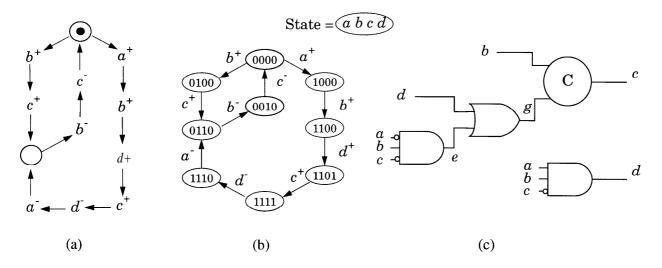

Automated circuit synthesis begins with a high-level specification that describes the desired input/output behavior of the circuit. For asynchronous circuits, many styles of high-level specifications have been proposed including languages [32, 50], graphs [12, 14], and state machines [43]. Although there are many differences between the various specification styles, they all model (at least implicitly) both the desired circuit behavior and the circuit's environment. Thus, unlike many synchronous specification styles, these specifications dictate the input behavior the circuit can expect, without which it would be quite difficult, if not impossible, to synthesize a hazard-free implementation. An example of a simple specification using a *signal transition graph* STG with choice [12] is given in Figure 1(a).

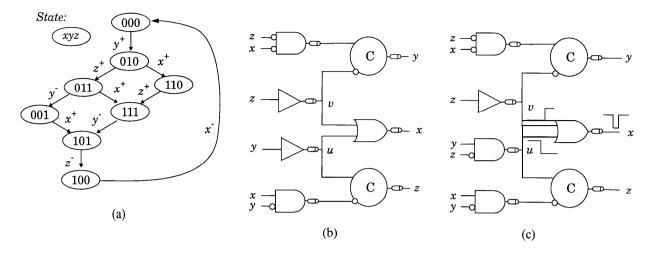

The first step in our synthesis strategy is to translate the high-level specification into an intermediate format called a state graph (SG). A SG is general enough to capture all external behavior of a system and can be easily obtained from most high-level languages. The SG obtained from the STG depicted in Figure 1(a) is depicted in Figure 1(b). From the SG, our synthesis procedure synthesized a circuit that implements all output signals with a netlist of basic gates such as AND gates, OR gates, and C-elements with arbitrary inverted inputs and number of fanins limited by a given maximum. A hazard-free gate-level speed-independent circuit for the SG depicted in Figure 1(b) is depicted in Figure 1(c). This section formalizes both our state graph and circuit implementation models.

#### 2.1 State graph

A state graph (SG) is modeled by the tuple (I, 0,  $\Phi$ ,  $\Gamma$ , s<sub>0</sub>,  $\lambda$ ), where *I* is a set of input signals, *O* is a set of output signals,  $\Phi$  is a set of states,  $\Gamma \subseteq \Phi \times \Phi$  is a set of state transitions,  $s_0$  is the initial, or *reset*, state, and  $\lambda$  is a labeling function for states. *The* set of *external signals* is the union of the input and output signals (denoted A <sub>Spec</sub>).

The labeling function  $\lambda$  labels each state  $s \in \Phi$  with a bitvector over the external signals, i.e.,  $\lambda(s) \in \mathcal{B}^{A_{Spec}}$ . The value of a signal  $u \in A_{Spec}$  in a state s is the value of u in the label of s, i.e.,  $s(u) \equiv X(s)(u)$ . The function *bitcomp*(s, u) returns the label formed from s by complementing the bit corresponding to u. For example, for the state s labeled [0000] in the SG in Figure 1 (b), *bitcomp*(s, a) = [1000].

A state graph must be strongly connected and each ordered pair (s, s') must differ in exactly one signal, i.e.,  $\lambda(s') = bitcomp(s, u)$  for some  $u \in A_{Spec}$ . For a state transition  $(s, s') \in \Gamma$  in which  $\lambda(s') = bitcomp(s, u)$ , the notation  $s \xrightarrow{u} s'$  may be used. A signal  $u \in A_{S,u}$  is enabled in state s (denoted *enabled*(u, s)) if u can change in state s, that is, if there exists an  $s' \in \Phi$  such that  $s \xrightarrow{u} s'$  holds.

A SG has unique state coding [12] if every state in the state graph has a unique label. A SG has complete state coding [12] if for every pair of states s and s' that have the same label, s and s' have the same output signals

Figure 1: (a) A STG with input choice (motivated by the example STG in Figure 3(d) of [13]), (b) the corresponding determinate SG and, (c) a corresponding hazard-free gate-level circuit.

enabled. Complete state coding is a necessary property for a state graph to be implementable as a speed-independent circuit [12]. It has been reported that adding state variables can transform an arbitrary SG into one that satisfies complete state coding [13, 28, 51]. We therefore assume that one of these algorithms is used before the SG is fed into our synthesis tool.

A SG with complete state coding can be transformed into a SG with unique state coding by folding states with the same label into a single state. More precisely, to fold states, take every pair of states s and s' with the same label, remove s' from the set of states  $\Phi$ , and replace s' with s in every place s' appears in  $\Gamma$ . Also, if  $s_0 = s'$ , reassign  $s_0$  to s. Note that folding such states has no effect on the semantics of the specified output signal behavior and guarantees that states can be unambiguously referred to by their label, thereby simplifying algorithm presentation. Therefore, without loss of generality, our algorithms assume that the state graph has unique state coding.

A signal u is disabled by a signal  $v, v \neq u$ , in a state s if u is enabled in state s and not enabled in s' where  $s \xrightarrow{v} s'$ . A SG is *determinate speed-independent* if in every state transition in the SG, output signals may not disable any signals (no output choice) and input signals may not disable output signals but may disable other input signals (input choice).

The SG in Figure 1(b) is determinate speed-independent. Formally, this SG is modeled by (I,  $O, \Phi, \Gamma$ ,  $s_0, \lambda$ ) where  $I = \{a, b\}$  and  $0 = \{c, d\}$ . There are 9 states in the set of states  $\Phi$  including states [0000] and [0100]. There are 9 transitions in the set of transitions  $\Gamma$  including [0000]  $\xrightarrow{a}$  [1000] and [0000]  $\xrightarrow{b}$  [0100]. These two state transitions illustrate input choice between a and b since when a fires, b is disabled and when b fires, a is disabled.

#### 2.2 Circuit implementation

A circuit implementation is modeled by a graph (I, 0, N, E, F), where I is the set of input signals, 0 is the set of output signals, N is the set of internal signals, E is a set of connections between signals, and F is a set of local gate functions. The set of *circuit signals* is the union of inputs, outputs, and internal signals (denoted  $A_{Impl}$ ). Each edge  $e \in E$  represents a connection between circuit signals. An edge e is directed, connecting a source signal to a sink signal. The set of fanins of u, denoted FI(u), is all sources of edges that have u as its sink. Similarly, the set of fanouts of u, denoted FO(u), is all sinks of edges that have u as its source. This paper considers only *externally-cut* circuits in which outputs of all memory elements are primary outputs and external signals cut the circuit.

The status of an implementation at some point in time is modeled using an *implementation state* that is either a bitvector over  $A_{Impl}$ , i.e.,  $q \in 2^{A_{Impl}}$ , or the special value,  $q_{fail}$ , that models the failure state of an implementation entered after the occurrence of a *hazard* (defined formally in Appendix E). Each gate output signal u has an associated Boolean function  $f \in F$  of arity |Fl(u)| + 1. We refer to  $f_u(q(u), q(v_1), \ldots, q(v_r))$ , where FI(u) = $\{v_1, \ldots, v_r\}$ , as the *internal evaluation* of u in q since it depends on the values of circuit signals in state q and we abbreviate it as  $f_u(q)$ .

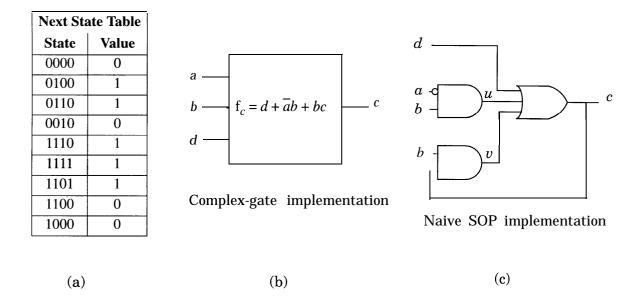

Figure 2: (a) The next-state table for c, (b) a complex-gate implementation for the SG depicted in Figure 1, and (c) the naive sum-of-products implementation.

Figure 1(c) depicts a circuit implementation of the SG shown in Figure 1(a). Formally, the circuit is modeled by (I, 0, N, E, F), where  $I = \{a, b\}$ ,  $0 = \{c, d\}$ ,  $N = \{e, g\}$ . There are 10 edges in E including (a, d), (b, d), and (c, d) which correspond to the famins of d. The functions  $f \in F$  that are associated with each internal and output signal are  $f_d = AND$ -N-3(a, b, c),  $f_e = AND$ -N-I-3(u, b, c),  $f_g = OR(d, e)$ , and  $f_c = C$ -ELEMENT(c, b, g). The circuit signals a and b are input signals and thus have no associated gate function; their behavior is derived from the specification. Notice that the inverter bubbles are included in the gate function. For example, the gate AND-N-3 is an AND gate whose third input is inverted.

# **3** The gate-level synthesis problem

The gate-level synthesis problem is to find a netlist of library gates that implements a given state graph. Previously, Chu [12] and Meng [37] solved the problem by assuming the gate library had all possible complex gates such that each output function could be implemented with a single complex gate. When the gate library is more constrained, such as is in standard cell-based and gate-array designs, each output function must be decomposed into a netlist of gates available in the library while preserving speed-independence. This section reviews the complex-gate solution and describes how naive gate-level implementations of output functions can introduce hazards into the circuit, to present an intuitive overview of our new necessary and sufficient conditions that guarantee hazard-freedom.

#### 3.1 Complex-gate implementations

The synthesis problem using complex gates amounts to deriving the next-state equations for each output signal from the SG, finding the optimal logic function satisfying the next-state equation, and implementing the optimal logic function with a single complex gate. As described in [12] and [37], the next-state equation of an output signal u is an incompletely specified function derived from the state graph. For each state  $s \in \Phi$  in which u is enabled to rise or has already risen and is not enabled to fall, its next state is assigned 1. For all other states in  $s \in \Phi$ , its next state is assigned 0. The remaining unreachable states in the Boolean space ( $\mathcal{B}^{A_{Spec}} - \Phi$ ) are don't cares. Standard Boolean techniques can be used to optimize the next-state equation [8]. The resulting equation is then assumed to be implemented using a single complex gate. For the output signal c in Figure 1, the next-state function and complex-gate implementation is illustrated in Figures 2(a) and 2(b).

A complex-gate correctly implements a next-state function if the gate evaluates to the next-state function in each state. When every complex gate correctly implements the corresponding next-state function, the circuit is *complex*-

gate equivalent to its specification. Informally speaking, a circuit is said to be hazard-free if logic glitches cannot occur at the output of any gate. If every output signal is implemented with a single complex gate, complex-gate equivalence is sufficient to guarantee that the circuit is hazard-free.

#### 3.2 Gate-level implementations

Gate-level implementations are circuits in which each output signal is implemented with a netlist of basic gates. The key difference between gate-level implementations and complex-gate implementations is the presence of internal signals and their associated arbitrary delay elements whose behavior is not modeled in the SG. Since these arbitrary delays can result in unexpected changes in the arrival order of signal transitions, naive decompositions of complex gates into netlists of basic gates often introduce hazards. For example, in this section we show that the naive sum-of-products decomposition of the complex-gate implementation shown in Figure 2(c) has numerous sources of hazards.

To find hazard-free decompositions, we must understand the sources of such hazards and ensure that our decompositions do not introduce any of these sources. This subsection describes a classification of hazard sources based on an interpretation of the request/acknowledge handshaking protocol on circuit gates. First we describe our interpretation of this protocol in general terms and then use the above example to explain the details.

#### 3.2.1 The request/acknowledge protocol

In its general form, the request/acknowledge handshaking protocol is a method of managing the communication between modules. For example, a request can represent that data is valid on the inputs of a function block F and that F should begin to compute. A corresponding acknowledgement from F indicates that the computation has been completed and that valid data exists on its outputs.

For gate-level speed-independent circuits, a request is a set of states in which a circuit signal u is supposed to change to a particular value. An acknowledgement of this request is any primary output transition that cannot occur until after the signal reaches the particular value. A necessary condition to guarantee hazard-freedom is that every request is *acknowledged* before a new request is sent to the same signal. Otherwise, the two requests can collide which causes a hazard.

Acknowledgement, however, is a necessary but not a sufficient condition for hazard-freedom. Since the request may need to travel through many gates until it reaches the input to the gate that drives the signal, the request must be guaranteed to be glitch-free. In other words, the request must reach the signal *monotonically*. Acknowledgement and monotonicity together form *necessary and sufficient conditions* for hazard-freedom. These concepts are formalized in Appendices A and B.

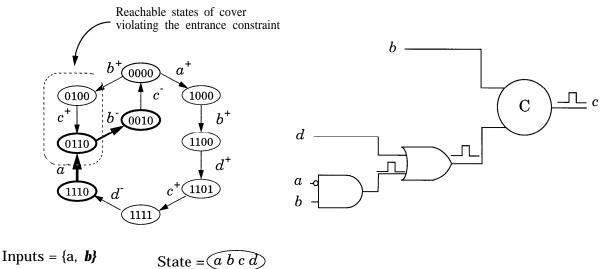

#### 3.2.2 Acknowledgement and monotonicity

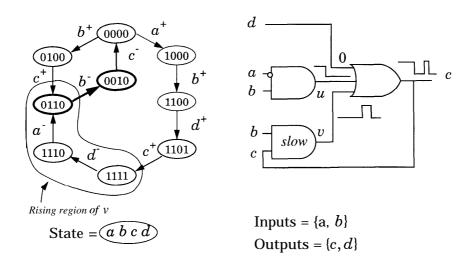

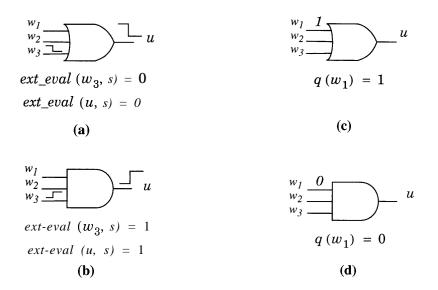

Since our circuits are externally-cut, only acyclic combinational logic connects internal signals to external signals. Hence, each circuit signal is either driven high or driven low in each state s but does not necessarily reach this value before the circuit leaves state s. The value that a signal u is driven to is referred to as the *external evaluation* of u in state s, denoted *ext\_eval(s)(u)*. A *signal region* of u is a maximal *connected* set of states in which u has the same external evaluation, where a set of states is connected if any two members are mutually reachable through an undirected path of states in the set. Each signal region is a single request for the signal u to change to its external evaluation. For example, a request for signal v to rise is represented by the signal region { [1111], [1110], [0110]} because v evaluates to 1 in all these states, as depicted in Figure 3.

A path of states through a signal region of u is acknowledged by a transition of a primary output v if the path includes a state transition  $s \xrightarrow{v} s'$  which cannot fire until after u reaches its new external evaluation. A signal region is *acknowledged* if all paths through the region are acknowledged. There may be many primary output transitions that can acknowledge the same path through a request. In fact, in the presence of input choice, many primary output transitions may be needed to acknowledge a single request.

Every request must be acknowledged before a new request is sent to the same signal to prevent two requests from colliding. Consider the decomposition of the complex gate for the signal c described in Figure 3. Consider the highlighted path through the rising request for v following states [0110] and [0010]. Notice that the path is not acknowledged since it does not contain any output signal transition that acknowledges v rising. As a result, this rising request on v can collide with the subsequent falling request on v. In other words, if the AND gate bc is

slow, it may not rise before the circuit enters state [0010] and can later be disabled. This can cause the sequence of transitions  $u^-$ ,  $c^-$ ,  $v^+$ ,  $c_+$ ,  $v^-$ ,  $c^-$ , representing a dynamic hazard at signal c.

Figure 3: Illustration of a naive decomposition introducing an acknowledgement violation into the circuit.

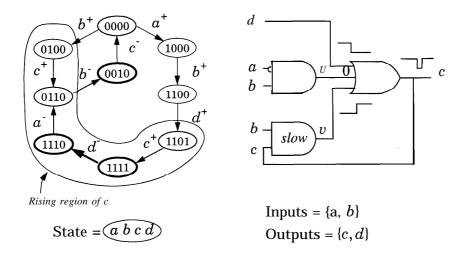

As mentioned earlier, the request for a signal transition must be monotonic. Consider the rising request of c in Figure 4 corresponding to the signal region consisting of states { [0100], [0110], [1110], [1111], [1101]}. In state transition [ 111 1]  $\stackrel{d}{\rightarrow}$  [ 11 10], the request must travel through the AND gate driving signal v before it reaches the OR gate that drives signal c. To ensure that c sees this request glitch free during this state transition, c must be *insensitive* to d, the falling input to the OR gate. In other words, the request must travel through the AND gate and drive v high before d can fall. Unfortunately this ordering is not guaranteed and the sequence of transitions  $d^{-}, c^{-}, v^{+}, c^{+}$  depicted in Figure 4 can occur, representing a static O-hazard on output c.

Figure 4: Illustration of a naive decomposition introducing monotonicity violation into a circuit,

Appendix C formalizes a procedure that conservatively identifies when internal signals are guaranteed to be high or low. Appendix D then formalizes the corresponding notions of acknowledgement and monotonicity and shows that they are sufficient (but not necessary) to guarantee hazard-freedom. We use these sufficient conditions to prove that our synthesis algorithm generates hazard-free circuits and that our logic transformations do not introduce hazards.

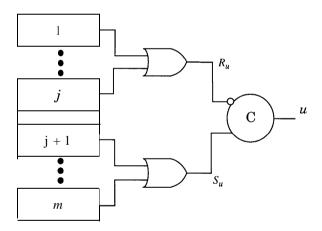

# 4 Standard C-implementation

The first step of our proposed procedure is to generate an optimal block-level implementation. To accomplish this, set and reset excitation regions of each output signal are identified in the SG and are implemented in independent blocks called region functions. Intuitively, each region function implements a different output signal transition in a higher-level specification. For example, the two  $c^+$  transitions in the STG depicted in Figure 1(a) are independently implemented using two region functions. The region functions for each output are merged into a signal network, depicted in Figure 5, using two OR gates and one two-input Muller C-element, an asynchronous memory element. This C-element has a non-inverted input from the set network  $S_u$ , an inverted input from the reset network  $R_u$ , and one output u. The next state equation is  $f_u = (S_u + R_u) \cdot u + S_u \cdot \overline{R_u}$ . In other words, when  $S_u$  is high and  $R_u$  is low, the signal u is driven high. When  $S_u$  is low and  $R_u$  is high, u is driven low. Otherwise, the signal u retains its old value. The collection of signal networks, one for each output, is referred to as the circuit's standard C-implementation. Note that while this implementation strategy may not immediately represent an optimal hazard-free circuit, particularly when logic can be shared across set and reset region functions, optimizations presented in Section 6 can be used to significantly improve circuit quality.

To ensure hazard-freedom of the block-level implementation, the covers of the region function must satisfy certain *correct cover* constraints. This section first develops these constraints and describes their relationship to ensuring hazard-freedom, i.e., acknowledgement and monotonicity. Next, this section casts the problem of finding the optimal correct cover into a binate covering problem and presents two efficient algorithms to find the optimal correct cover.

Figure 5: A signal network for an output signal u consisting of m region blocks denoted 1 through m.

#### 4.1 Theory

#### 4.1.1 Excitation and quiescent regions

For each output signal, the state graph is partitioned into a collection of excitation and quiescent regions. An excitation region is a maximally connected set of states in which the output signal is both enabled and at a constant value. Excitation regions are divided into two types depending on the value of the output signal in the excitation region. If the value is 0, the region is a *set excitation region* since in all excitation region states the output signal is enabled to rise; otherwise the region is a *reset excitation region*. A maximally connected set of states in which the output signal is not enabled is called a quiescent region of the output signal. In a determinate speed-independent SG, there exists at most one quiescent region directly reachable from a given excitation region, but a quiescent region may be entered from multiple excitation regions. The excitation regions for a signal u are indexed with the variable k and the  $k^{th}$  excitation region of signal u is denoted ER(u, k). The associated quiescent region is denoted

QR(u, k). For example, there are two excitation regions for the signal c to rise in Figure 1. The first, denoted ER(c, 1), is the set of states { [0100]} and the second, denoted ER(c, 2), is the set of states { [1101]}. Both these excitation regions share the same quiescent region  $QR(c, 1) = QR(c, 2) = \{[0110], [1110], [1111]\}$ .

#### 4.1.2 Correct covers

The *cover* of an excitation region C(u, k) is a set of states in which the corresponding region function externally evaluates to one. A cover is a correct cover if it satisfies two conditions. First, it must satisfy the *covering constraint* which says that the reachable states in the cover must include the entire excitation region but must not include any states outside of the union of the excitation and associated quiescent region, i.e.,

$$ER(u,k) \subseteq [C(u,k)) \cap \Phi] \subseteq [ER(u,k) \cup QR(u,k)].$$

Second, it must satisfy the *entrance constraint* which says that a correct cover must only be entered through excitation region states, i.e.,

$$[s \notin C(u, k) \land s' \in C(u, k) \land (s, s') \in \Gamma] \Rightarrow s' \in ER(u, k).$$

As proven in Appendix E, ensuring that all region function covers are correct covers is sufficient to guarantee that the standard C-implementation is a correct circuit provided that each region function is implemented with a single atomic gate. The covering constraint guarantees that the circuit is complex-gate equivalent to the specification. A correct cover guarantees that each region function is only allowed to turn on when it is actively trying to fire u. This guarantees that every request of the region functions, the OR gates, and the C-element is acknowledged by the output signal changing. Moreover, it guarantees that no two inputs to the OR gates are simultaneously one, avoiding what has traditionally been called a delay hazard [1]. We also show that a correct cover guarantees the monotonicity of all requests on all gates in the signal network.

To illustrate the importance of the entrance constraint in correct covers consider the cover and corresponding standard C-implementation for the output signal c shown in Figure 6. The cover { [0100], [0110], [0111] }

outputs =  $\{c, d\}$

Figure 6: (a) A cover violating the entrance constraint for a set excitation region of the signal c, and (b) the corresponding hazardous logic implementation.

(which includes unreachable states [0101] and [0111]) fails to satisfy the entrance constraint since it can be entered from the state [1110] which is not in the excitation region. As a result, the corresponding region function AND-N-l@, b can turn on and off without being acknowledged. This can cause a glitch at the output of the AND gate which may cause the circuit to malfunction.

The relationship between cover constraints and the acknowledgement of the region function requests is subtle. Kondratyev et al. in [25] misinterpreted these conditions, which we first presented in [5], and erroneously claimed that our covering constraints do not guarantee acknowledgement and allow hazardous implementations to be synthesized [24]. In fact, the constraints described in their paper are not complete, allowing hazardous covers such as the one shown in Figure 6. This ambiguity, however, can be resolved with a simple amendment to their theory, making the two sets of covering constraints essentially equivalent [24].

#### 4.2 Algorithms

While standard logic minimization techniques exist to find optimal covers [8], they do not guarantee hazard-free logic. In particular, they are not suited to solve our more constrained covering problem. To guarantee hazard-free logic, we included the notion of an entrance constraint which requires that a correct cover can be entered only through excitation region states. The entrance constraint ensures that if a state in the quiescent region is covered than each of its predecessor states must also be covered. This implication leads to a *binate covering problem* [22].

This section presents algorithms to solve this binate covering problem obtaining an optimal region function. In general, a region function is composed of a set of *cubes*. A cube is a set of *literals* which are either an external signal or its complement. First, we present a general algorithm that finds an implementation for each region function composed of the minimal number of cubes. It is often the case, however, that a region function can be implemented using only a single cube. If this is the case, we use a more efficient algorithm which finds a single-cube implementation for each region function composed of the minimal number of the minimal number of literals.

#### 4.2.1 General algorithm

The goal of the general algorithm is to find an optimal sum-of-products function for each region function that satisfies our definition of a correct cover. The final hazard-free multi-level logic implementation of this function is obtained using the decomposition techniques described in the next section.

The sum-of-products cover consists of a disjunction of *implicants*. An implicant of an excitation region is a cube that may be part of a correct cover. In other words, a cube c is an implicant of an excitation region ER(u, k) if the set of reachable states covered by c is a subset of the states in the union of the excitation region and associated quiescent region, i.e.,

$$[c \cap \Phi] \subseteq [ER(u,k) \cup QR(u,k)].$$

A *prime implicant* is an implicant which is not contained by any other implicant of the excitation region [35]. A sum-of-products cover is optimal if there exist no other cover with fewer implicants.

To capture the entrance constraint, each implicant c is said to have a corresponding set of *implied states* (denoted IS(c)). An implied state of a cube c is a state that is not covered by the implicant but due to the entrance constraint must be covered if the implicant is to be part of the cover. More precisely, a state s is an implied state of an implicant c for the excitation region ER(u, k) if s is not covered by c and is a predecessor of a state that is both covered by c and in the quiescent region, i.e.,

$$IS(c) = \{ \mathbf{s} \mid \mathbf{s} \notin \mathbf{c} \in \mathbf{A} \; \mathbf{3s'} \; [(\mathbf{s}, \mathbf{s'}) \in \Gamma) \; \mathbf{A} \; (s' \in c) \; \mathbf{A} \; (s' \in QR(u, k)) ] \}$$

It is important to note that an implicant may have implied states that are outside the excitation and quiescent regions and cannot be covered by any correct cover. For this reason, some instances of our covering problem cannot be solved using only prime implicants and non-prime implicants must be considered.

To this end, we define an implicant to be a *candidate implicant* if there exists no other implicant which properly contains it and has a subset of the implied states. In other words, c is a candidate implicant if there does not exist an implicant c' that satisfies the following two conditions:

$$c' \supset \mathbf{c}$$

$$IS(c') \subseteq IS(c).$$

Notice that prime implicants are always candidate implicants, but that a candidate implicant need not be prime. It is easy to prove that an optimal cover always exists that consists of only candidate implicants.

Using these candidate implicants, our covering problem is formulated by creating a binary function in conjunctive (product-of-sums) form to be satisfied with minimum cost. The binary function is defined over a set of Boolean variables  $l_i$ , one for each candidate implicant  $c_i$ . The variable  $l_i$  is *TRUE* if the cube  $c_i$  is included in the cover

and *FALSE* otherwise. A conjunctive function over these variables is composed of two types of disjunctive clauses. This function is *TRUE* when the included cubes make up a correct cover.

First, a *covering clause* is included for each state s in the excitation region of an output signal. Each clause consists of a disjunction of candidate implicants that cover s, i.e.,

$$\bigvee_{i:s \in c_i} l_i.$$

To satisfy the covering clause for a state s, at least one  $l_i$  must be set to *TRUE*. This means that one cube that covers s must be included in the cover. It follows that the set of covering clauses for an excitation region guarantee all excitation region states are covered. Since all candidate implicants are guaranteed not to include states outside of the excitation and associated quiescent region, the cover is guaranteed to satisfy the covering constraint.

Second, for each candidate implicant  $c_i$ , a *closure clause* is included for each of its implied states  $s \in IS(c_i)$ . Each closure clause represents an implication that states if the Boolean variable associated with the cube  $c_i$  is true then the implied state s must be covered. To fit into a conjunctive form the implication is translated to the equivalent disjunction, i.e.,

$$\overline{l_i} \vee \bigvee_{j:s \in c_j} l_j.$$

A closure clause states that if  $c_i$  is in the cover, some other cube must also be selected that covers the implied state s. The covering and closure clauses together ensure that the cover satisfies the entrance constraint.

When the entire conjunctive function is satisfied, the corresponding cover is correct. Our goal is to find an assignment of Boolean variables that satisfies the function with the minimum cost. The cost function we minimize is the number of implicants, though, the number of literals can also be used. Since the implication introduces negated variables into the satisfiability product-of-sums framework, our optimization problem is a binate covering problem.

We now present an algorithm to find a cover using the minimum number of candidate implicants. First, the algorithm finds the prime implicants for each region function. Second, it uses this set to find all the candidate implicants. Then, it solves the binate covering problem represented as a *covering and closure table* (or *CC table*) [21], using traditional reduction and branching techniques. We are currently exploring newer algorithms that may solve our binate covering problems more efficiently [9, 23, 29, 44].

In order to find the set of prime implicants, our algorithm partitions the Boolean space into three sets, the on-set, the off-set, and the don't care-set. The on-set is composed of every state in the excitation region. The don't-care set is composed of every state in the associated quiescent region as well as every unreachable state. The off-set is composed of every other reachable state. The prime implicants are found using standard techniques [8].

Next, the algorithm expands the set of prime implicants to include all candidate implicants using the procedure described in [21]. The algorithm first seeds the list of candidate implicants with the prime implicants, sorted by the number of literals in the implicant. Beginning with the candidate prime with the fewest number of literals, the algorithm considers all implicants extended with a literal not already used in the prime. If any new implicant satisfies the conditions given above then the algorithm inserts it into the list. Each subsequent implicant is considered in order until no new candidate implicants can be added.

To solve the binate covering problem, a CC table is constructed to represent the conjunctive function described above. The table has one row for each candidate implicant and one column for each clause. The columns are divided into a *covering section* and a *closure section*, corresponding to covering and closure clauses. In the covering section, for each excitation region state s, a column exists containing a cross in every row corresponding to a candidate implicant that covers s. In the closure section, for each implied state s of each candidate implicant  $c_i$ , a column exists containing a dot in the row corresponding to c  $_i$  and a cross in each row corresponding to a candidate implicant  $c_i$  that covers the implied state s.

As an example, the CC table for excitation region ER(c, 1) in our example is depicted in Table 1. The CC table is solved using the reduction rules described in [21], which are listed here for convenience:

- Rule 1: (Select essential rows) If a column contains only a single cross and blanks elsewhere, then the row with the cross must be selected. This row is deleted together with all columns in which it has crosses.

- Rule 2: (Remove columns with only dots) If a column has only a single dot and blanks elsewhere, the row containing the dot must be deleted together with all columns in which it has dots.

| CC Table                    |                  |                                 |                                 |                                 |                                 |

|-----------------------------|------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|

|                             | Covering Section | Closure Section                 |                                 |                                 |                                 |

|                             | [0100]           | $[1110] \xrightarrow{a} [0110]$ | $[1101] \xrightarrow{c} [1111]$ | $[1101] \xrightarrow{c} [1111]$ | $[1101] \xrightarrow{c} [1111]$ |

| $\overline{a}b$             | ×                | 0                               |                                 |                                 |                                 |

| $\overline{a}b\overline{c}$ | ×                |                                 |                                 |                                 |                                 |

| ac                          |                  | ×                               | 0                               |                                 |                                 |

| $a\overline{b}c$            |                  |                                 |                                 |                                 |                                 |

| bc                          |                  | ×                               |                                 | 0                               |                                 |

| $\overline{a}d$             |                  |                                 |                                 |                                 |                                 |

| bd                          |                  |                                 |                                 |                                 |                                 |

| cd                          |                  |                                 |                                 |                                 | 0                               |

Table 1: The CC table for the general covering algorithm applied to ER(c, 1).

- Rule 3: (Remove dominating columns) A column  $C_j$  dominates a column  $C_i$  if it has all the crosses and dots of  $C_i$ . If  $C_j$  dominates  $C_i$ , then  $C_j$  is deleted.

- Rule 4: (Remove dominated rows) A row  $R_i$  dominates a row  $R_j$  if it (a) has all the crosses of  $R_j$ , and (b) for every column  $C_p$  in which  $R_i$  has a dot, either  $R_j$  has a dot in  $C_p$  or there exists a column  $C_q$  in which  $R_j$  has a dot, such that, disregarding the entries in rows  $R_i$  and  $R_j$ ,  $C_p$  dominates C,. If  $R_i$  dominates  $R_j$ , then  $R_j$  is deleted together with all columns in which it has dots.

- Rule 5: (Remove rows with only dots) If a row only has dots, then the row is deleted together with all columns in which it has dots.

It is important to note that when applying rule 4, two rows may mutually dominate each other. To break this tie, our algorithm removes the row corresponding to the implicant composed of the larger number of literals.

The table is completely solved when all columns are eliminated, and the resulting cover is the set of essential rows selected by Rule 1. In our limited experience, these reduction rules are usually sufficient to solve the table. For some cases, however, the reduction rules do not reduce the table completely, leaving a *cyclic table*. To solve the cyclic table, we currently use traditional branching techniques [35] and are exploring the use of newer branch and bound techniques [9, 23, 44].

The reduction steps solve the table depicted in Table 1 as follows. First, the rows ac, bc, and cd along with the three columns labeled  $[1101] \xrightarrow{c} [1111]$  can be removed by Rule 2. Moreover, rows  $\overline{a}b$ , abc,  $\overline{a}d$ , and  $\overline{b}d$  are dominated by row  $\overline{a}b\overline{c}$  and can be removed along with the column  $[1110] \xrightarrow{a} [0110]$  by Rule 4. The remaining candidate implicant,  $\overline{a}b\overline{c}$  is essential and is picked by Rule 1, solving the table. Note that in this case the table can only be solved by selecting an implicant that is not prime.

This example motivates two optimizations. First, prime implicants that cover only don't care states need not be considered in the generation of the candidate implicants, since such candidate implicants are never part of an optimal cover. Second, quiescent region states that are not reachable from some state in the excitation region through a path consisting of only other quiescent region states can be put in the off-set when determining the prime implicants, since the entrance constraint excludes them from being part of a correct cover. These optimizations can make the initial CC table significantly smaller.

#### 4.2.2 Single-cube algorithm

The above binate covering formulation is often more general than needed since many region functions can be implemented with a single-cube cover. In this subsection, we present a more efficient algorithm designed to find an optimal single-cube cover if one exists. This algorithm is derived from an algorithm used to synthesize complex-gate timed circuits [40] by adding the necessary closure constraints needed to handle gate-level hazards, and it has also been applied to the synthesis of gate-level timed circuits [41]. Our synthesis procedure initially attempts to find single-cube covers, and only when this algorithm fails is the general algorithm described above invoked.

For a single-cube cover to hazard-freely implement a region function, all literals in the cube must correspond to signals that are *persistent*, i.e., constant throughout the excitation region (this is a slightly more general definition

|             |           | -        |         |

|-------------|-----------|----------|---------|

| u, k        | set/reset | EC(u, k) | TC(u,k) |

| c, 1        | set       | 0100     | X1XX    |

| c, 2        | set       | 1101     | XXX1    |

| <i>c</i> ,3 | reset     | 0010     | X0XX    |

| d, 1        | set       | 1100     | X1XX    |

| d, 2        | reset     | 1111     | XX1X    |

Table 2: Enabled cubes and trigger cubes for our example, where the cube vector is (a, b, c, d)

than the one in [12]). Otherwise, the single-cube cover would not cover all excitation region states. When a single-cube cover exists, an excitation region ER(u, k) can be sufficiently approximated using a cube called an *enabled cube*, denoted EC(u, k), defined on each signal v as follows:

$$EC(u, k)(v) \equiv \begin{cases} 0 & \text{if } \forall s \in ER(u, k) [s(v) = 0] \\ 1 & \text{if } \forall s \in ER(u, k) [s(w) = 1] \\ X & \text{otherwise} \end{cases}$$

If a signal is 0 or 1 in the enabled cube, it can be used in the cube implementing the region. A cube, such as the enabled cube, implicitly represents a set of states in the obvious way. The set of states implicitly represented by the enabled cube is always a superset of the set of excitation region states.

Each single-cube cover in the implementation is composed of *trigger signals* and *context signals*. For a given excitation region, a trigger signal is a signal whose firing can cause the circuit to enter the excitation region while any non-trigger signal which is stable in the excitation region can be a context signal. The set of trigger signals for an excitation region ER(u, k) can also be represented with a cube called a *trigger cube*, denoted TC(u, k), defined as follows for each signal v:

$$TC(u, k)(v) \equiv \begin{cases} s'(w) & \text{If } \exists s, s' \left[ (s \stackrel{v}{\to} s') \land (s \notin ER(u, k)) \land (s' \in ER(u, k)) \right] \\ X & \text{otherwise} \end{cases}$$

It is easy to show that in order for a single-cube cover to satisfy the covering constraint it must contain all its trigger signals. Since only persistent signals can be included in a single-cube cover, a necessary condition for a single-cube cover to exist is that all trigger signals be persistent. In other words, for a given excitation region ER(u, k), the following must be true:

$$\forall v \in A_{Spec} \left[ (TC(u,k)(v) = X) \lor (TC(u,k)(v) = EC(u,k)(v)) \right]$$

The enabled cubes and trigger cubes are easily found with a single pass through the state graph. The enabled cubes and trigger cubes corresponding to all the excitation regions in our example are shown in Table 4.2.2. Notice that every trigger signal is persistent and our algorithm proceeds to find the optimal single-cube cover.

Our algorithm starts with a cube consisting only of the trigger signals. If this cover contains no *conflicts*, i.e., states that violate either the covering or entrance constraint, we are done. This, however, is often not the case, and context signals must be added to the cube to remove any conflicting states. For each conflict detected, the procedure determines the choices of context signals which would exclude the conflicting state. Finding the smallest set of context signals to resolve all conflicts is a covering problem. Due to the implication in the entrance constraint, inclusion of certain context signals may introduce additional conflicts which must be resolved. Therefore, the covering problem is *binate*.

To solve this binate covering problem, we again create a CC table for each region. There is a row in the CC table for each context signal, and there is a column for each conflict and each conflict that could potentially arise from a context rule choice. An entry in the table contains a cross (x) if the context signal resolves the conflict. An entry in the table contains a dot  $(\circ)$  if the inclusion of the context signal would require the conflict to be resolved.

To construct the table for a given excitation region ER(u, k), the algorithm first finds all states in the initial cover which conflict with the covering constraint. In other words, a conflict exists if a state s is (implicitly) contained by TC(u, k) but is not in the excitation or associated quiescent region. If a conflict exists, the algorithm adds a new column to the table with a cross in each row corresponding to a context signal v that would exclude the conflicting state (i.e., EC(u, k)(v) = s(v)). The next step in the table construction is to find all state transitions which conflict with the entrance constraint in the initial cover or may conflict due to a context signal choice. For any state transition  $s \xrightarrow{v} s'$ , this is possible when s is not in the excitation region (i.e.,  $s \notin EC(u, k)$ ), s' is in the quiescent region (i.e.,  $s' \in QR(u, k)$ ), s' is in the initial cover (i.e.,  $s' \in TC(u, k)$ ), and v excludes s (i.e., EC(u, k)(v) = s(v)). For each entrance conflict detected, the algorithm adds a new column to the table again with a cross in each row corresponding to a context signal that would exclude the conflicting state. If the signal v in the state transition is a context signal, the state s ' only needs to be excluded if v is included in the cover. This implication is represented with a dot being placed in the row corresponding to the signal v.

In a single pass through the state graph, all the CC tables can be constructed. Returning to our example, the CC table for the excitation region ER(c, 1) is given in Figure 3. For this excitation region, the enabled state is [0100]

| CC Table |         |           |                                 |                                 |  |  |

|----------|---------|-----------|---------------------------------|---------------------------------|--|--|

|          | Coverin | g Section | - Closure                       | Section                         |  |  |

|          | [1100]  | [1101]    | $[1110] \xrightarrow{a} [0110]$ | $[1111] \xrightarrow{d} [1110]$ |  |  |

| a        | ×       | ×         | 0                               | ×                               |  |  |

| c        |         |           | ×                               | ×                               |  |  |

| d        |         | ×         |                                 | 0                               |  |  |

Table 3: The CC table for the single-cube covering algorithm applied to ER(c, 1).

and b is its only trigger signal. The covering section includes states [1100] and [1101] because all other states are either in the excitation or quiescent region or are excluded by the trigger signal b. There are two closure columns. The first, corresponding to the transition [1110]  $\stackrel{a}{\rightarrow}$  [0110], indicates that if a is included then state [0110] must be excluded. The only context signal that excludes this state is c. The second closure column corresponds to the transition [1111]  $\stackrel{d}{\rightarrow}$  [1110] and is formed similarly. Note that the transition [1101]  $\stackrel{c}{\rightarrow}$  [1111] does not have a column since c does not exclude state [1101].

When the construction of the CC table is successful, the table is solved using essentially the same reduction algorithm used in the general case outlined above. In this case, however, ties that occur in Rule 4 are resolved by picking the rule that provides symmetry between different regions of the same signal. This symmetry can often be exploited later during logic optimizations (see Section 6). Returning to our example, the table is solved as follows. First, row a is picked since it is an essential row (Rule 1), removing it as well as columns [ 1100], [ 1101], and  $[1111] \xrightarrow{d} [1110]$  from the table. Since this removes a dot in column  $[1110] \xrightarrow{a} [0110]$ , this column is covered next. To accomplish this, row c is picked since it is an essential row (Rule 1), removing the column  $[1110] \xrightarrow{a} [0110]$  solving the table. The resulting correct cover, as expected, is the same single cube ubc found by the general algorithm.

When a trigger signal is not persistent or when the CC table construction fails, we can use the more general algorithm described in Section 4.2.1 to find a multi-cube cover. Alternatively, we can change the specification by constraining concurrency [37] or by adding state variables [25, 52, 6] such that a single-cube cover can be found. We note that this alternative may not be possible *without changing the interface behavior of the circuit* (i.e., without constraining an input signal).

# 5 Implementing region functions

Once an optimal cover is found, the cover must be implemented using limited-fanin basic gates. Often, the cover is reduced to a single cube with only a small number of literals where an AND gate that implements the cube is usually found in the target library. In addition, simple multi-cube covers can often be implemented safely with carefully designed and-or-invert gates. For larger, more concurrent specifications, however, single-cube covers that correspond to high-fanin AND gates or multi-cube covers may be needed. Therefore, it is important to consider how such covers can be implemented hazard-freely at the gate-level.

Our approach is to iteratively decompose the function into smaller functions until all base functions can be implemented by gates in the target library. This decomposition follows a break-and-repair strategy. First, the function is decomposed into two functions introducing a new internal signal into the circuit, adding a new delay element into the circuit which often causes a hazard, i.e., breaks the circuit. The repair step of our strategy adds connections to the circuit to reestablish hazard-freedom. The steps are iterated until all functions are of manageable size or no more functions can be successfully decomposed.

The most common function to be decomposed is a conjunction of many literals corresponding to a single-cube cover that covers relatively few states. For such functions, the obvious decomposition is a cascade of two smaller conjunctions. Since there may be many such decompositions, heuristics are used to order the attempts in such a way as to help find a decomposition leading to a correct circuit quickly.

For multi-cube covers there are many possible strategies for decomposition, including kernel extraction and function decomposition [17]. In [5], we describe an efficient decomposition heuristic in which the function is recursively decomposed into multi-level logic, guided by the relative ordering of signal transitions. We refer the reader to [5] for more details and focus in this paper on the repair aspects of our methodology which are general enough to be applicable to all decomposition techniques.

#### 5.1 Acknowledgement wire forks

When a function is decomposed into two functions a new gate is introduced into the circuit and with it an associated arbitrary delay. While some decompositions maintain correctness [46], many introduce hazards into the circuit. When the only decompositions found introduce hazards, the algorithm attempts to repair the damage by adding connections between gates, called *acknowledgement wire forks*.

Decompositions can generate two sources of acknowledgement and monotonicity violations. Consider a decomposition of a function  $f_v$  into two functions  $f_u$  and  $f'_v$  such that  $f_v = f'_v$  o  $f_u$ . Recall from Section 3.2 that the new signal u has its own set of requests for changes that must be acknowledged and be monotonic for the circuit to be hazard-free. The requests for signal v are unchanged. Signal v, however, may now have new violations of monotonicity which must be removed. The monotonicity violations are caused by the added delay element in the network. Before the decomposition, the stability of some fanins of v may have made it insensitive to inputs that might cause hazards. After the decomposition, the functionality of these inputs may have been pulled out into  $f_u$  which may not stabilize soon enough to prevent the monotonicity violation on v.

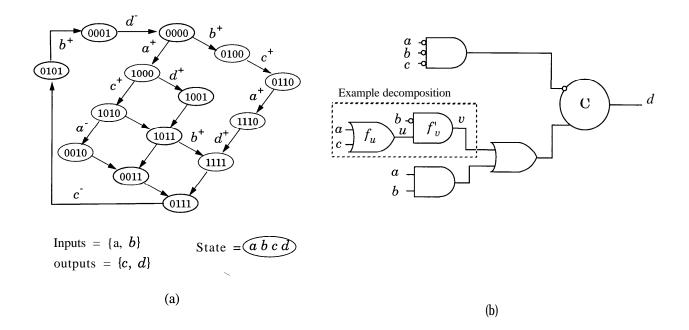

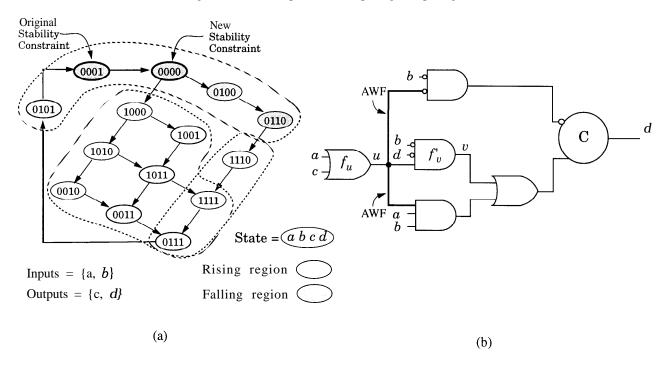

#### 5.2 Algorithm for repairing a decomposition

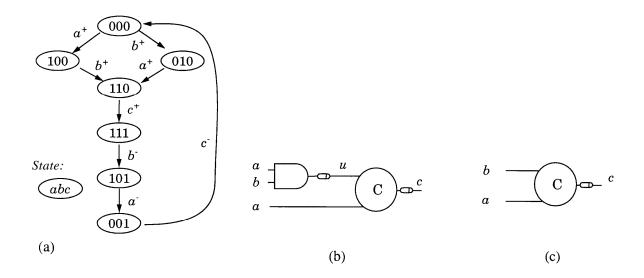

Our algorithm to repair a decomposition, depicted in Figure 7, is described using a circuit synthesized from a specification borrowed from [25], shown in Figure 8(a). In the synthesized circuit, shown in Figure 8(b), we attempt to decompose the complex gate  $f_v = a\overline{b} + c\overline{b}$  into two functions  $f_u = a + c$  and  $f'_v = \overline{b}f_u$ . The goal of the repair decomposition algorithm is to repair any acknowledgement or monotonicity violations caused by the presence of the new internal signal u. In other words, the algorithm attempts to ensure that all requests on u are acknowledged and monotonic. Recall from Section 3.2 that this means that every path through every signal region of u must be acknowledged. By adding an acknowledgement wire fork from u to some gate that controls an output signal, a transition of the output signal can be made to acknowledge previously unacknowledged paths. An obvious goal is to add a minimal number of such acknowledgement wire forks that guarantee that every path through the request is acknowledged. In other words, an optimal algorithm would find a minimal cut-set of acknowledging transitions.

Since finding the minimal cut-set is intractable, our algorithm uses a heuristic which may require more than the minimal number of acknowledgement wire forks, but works well in practice. The heuristic is to decompose each signal region into overlapping *subregions* that are independently acknowledged. The function *decompose-regions* finds the set of subregions for the region. Each subregion is formed from a different possible sequence of input choices made before and during the signal region. The distinguishing feature of a subregion is that both signal transitions between subregion states and signal transitions between a subregion state and a different signal region cut the subregion. As illustrated in Figure 9(a), the rising region of u in our example is decomposed into two overlapping subregions. One consisting of 8 states and the other of 3 states. These subregions arise from different ways that the rising signal region can be entered due to the input choice in the specification. The falling region of u is a single subregion.

Before examining possible acknowledgement wire forks, however, the algorithm must also consider the monotonicity violations of v caused by the decomposition. The function find\_stability\_constraints() identifies the stability constraints of the subregion. A stability constraint of a subregion is any state in which  $f_u$  must be stable in order to prevent a monotonicity violation of  $f'_v$ . In the example, a stability constraint of the falling region is state [0001] since u must be stable to avoid a monotonicity violation of v. That is, u must be guaranteed not to fall before b falls, since this can cause a glitch at v. If the stability constraint is initially satisfied, i.e. the function satisfies\_stability() returns **TRUE**, no acknowledgement wire fork is needed for the current subregion.

#### Algorithm 5.1 (Repair decomposition)

/\* Let G contain a new internal signal u with associated function  $f_u$  and a different function  $f'_u$  for signal v such that  $f_v = f'_v \circ f_u$ . \*/ repair\_decomposition(u, v, G, M) $R = find\_regions(u, G)$ : R' = decompose-regions(R);foreach  $R'_i \in R'$  $P_i = find\_stability\_constraints(v, R');$ if (satisfies\_stability( $R'_i$ ,  $P_i$ )  $\neq$  **TRUE**)  $c = find\_cuts(R'_i, P_i);$ if (c == NULL)relax-constraints(u, v, G, M) $c = find\_cuts(R'_i, P_i);$ if (c = NULL)exit with failure:  $e = find\_best\_awf(R'_i, P_i, c);$ if (e == NULL) $P_i = add\_conn(u, v, G, M);$  $e = find\_best\_awf(R'_i, P_i, c);$ if (e == NULL)exit with failure;  $build_awf(e);$

Figure 7: Algorithm for repairing a decomposition.

Otherwise, the stability constraints limit the choices of acknowledgement wire forks of a signal u. They indicate that u must be stable before entering the stability constraint state. The function *find\_cuts()* finds the output signal transitions that precede the stability constraint which might acknowledge u. For the falling subregion of the signal u in our example, there are no output signal transitions that cut the subregion which also precede the stability constraints. Hence, no acknowledgement wire forks can possibly be found that would guarantee that u is stable before state [0001] is entered. Fortunately, by adding additional inputs using the function *relax-constraints()* to the gate controlling v, the algorithm can sometimes relax the stability constraints. In this example, by adding  $\overline{d}$  to the AND gate controlling v, the stability constraint is moved to state [0000]. Once moved, the function *find\_cuts()* determines that a  $d^-$  transition can now acknowledge the falling subregion of u.

Once the set of acknowledging transitions is found, the function  $find\_best\_awf()$  locates the best potential acknowledgement wire forks. The function searches wire forks to all gates that control each potential acknowledging transition. A wire fork is a *potential acknowledgement wire fork* if the connection acknowledges the region and does not introduce additional acknowledgement or monotonicity violations. The implementation of checking the last requirement is addressed in Section 6. We note that one reason a wire fork is not a potential acknowledgement wire fork is that the wire fork would introduce extra unacknowledged requests on the acknowledging gate. By adding inputs to these acknowledging gates, using the function  $add\_conn()$ , the extra requests can be prevented. Of course, since our goal is to minimize fanin and complexity, the addition of gate inputs is only done when necessary.

Finally, the function *find\_best\_awf()* returns the acknowledgement wire fork to the acknowledging gate with the lowest fanin, thereby attempting to avoid the creation of new high-fanin gates. In our example, one of the three subregions is already acknowledged and satisfies its stability constraints and requires no acknowledgement wire forks. The other two subregions are acknowledged by two acknowledgement wire forks shown in Figure 9(b). Once acknowledgement wire forks are built, inputs to the acknowledging gates may become redundant and may be removed with optimizations discussed in Section 6. In this example, both the inputs  $\overline{a}$  and  $\overline{c}$  of the top AND gate can be removed. As a result the net overhead for the acknowledgement wire forks is negligible-one additional connection.

Although successful for this example, this heuristic break-and-repair methodology can fail when  $find_best_awf()$  fails to find a connection that acknowledges the region and satisfies the stability constraints. When using this decomposition technique to break up high-fanin gates, the addition of acknowledgement wire forks can also introduce

Figure 8: An example of decomposing complex gates.

Figure 9: An example of acknowledging subregions.

new high-fanin gates, which must be subsequently decomposed. When this approach successfully decomposes all gates, the circuits generated are usually very efficient. The approach, however, is not guaranteed to successfully decompose all circuits. For such circuits, carefully designed complex gates can be used to ensure hazard-freedom, or the circuits' specifications can be altered by adding state variables. Identifying the class of specifications with choice for which all functions can be sufficiently decomposed while preserving the circuit's interface behavior is an open research problem. Nevertheless, our algorithm has successfully synthesized all SIS benchmark specifications with gates of fanin 4 or less.

# 6 Logic optimizations

This section describes a variety of logic optimization techniques that can improve the initial gate-level circuit. Namely, this section describes removing redundant gate inputs, sharing and merging gates, signal-network simplification, and inverter bubble shuffling. Algorithms used to implement the optimizations are discussed in Section 7.

#### 6.1 Removing redundant gate inputs

A redundant gate input is one which can be removed from the circuit while preserving correctness. The removal of the input must preserve both complex-gate equivalence and hazard-freedom. A gate input can be functionally redundant, i.e., its removal preserves complex gate equivalence, while still not being a redundant gate input (e.g., an acknowledgement wire fork).

Redundant gate inputs arise for three reasons. First, since both set and reset functions of a signal are implemented separately and merged, they may duplicate needed logic. Sometimes the functions can be simplified while preserving correctness as illustrated in Section 7.2. Second, when an acknowledgement wire fork is added to a gate, other existing inputs of the gate may become redundant. Third, gate inputs may become redundant as a consequence of other optimizations, such as merging gates.

#### 6.2 Sharing and merging gates

Two *internal gates*, gates whose outputs are internal signals, that have the same function can be safely shared as long as one of the internal gates is not used to acknowledge a request of an internal signal that is not also acknowledged by the other gate. Similarly, two internal gates that have exactly the opposite function can be implemented with one gate by adding inverter bubbles to the fanout of one of the gates. If two *output gates*, gates whose outputs are primary outputs, have the same function, then, instead of inverter bubbles, an inverter is necessary. Moreover, an internal and output gate can be shared, but the output gate must be replaced with a buffer or inverter, depending on if the two gates have the same or opposite functions, respectively. Otherwise, two outputs which are specified to be ordered may become concurrent in the implementation, violating the specification.

A generalization to the sharing gate optimization is when two arbitrary gates can be implemented with one gate. It is easy to see that within a sum-of-product, two AND gates that differ in only the phase of one literal can be safely merged into one gate. In addition, other AND gates in sum-of-product blocks that are logically distance-one apart can often be symmetrized and then merged. Similarly, if AND gates in different parts of the circuit can be safely symmetrized to the point that they have the same functionality, the AND gates can be shared.

Two different approaches have been proposed to implement this optimization. The first approach, suggested by Kondratyev et al. [25], is a one-step process, but is limited to unoptimized AND gates implementing region functions. They suggest to formulate the covering constraints for a group of excitation regions to see if a single cube cover exists for the group. As long as each excitation region is covered by exactly one cube, correctness is guaranteed. The second approach is a two-step process. A minimum set of signals is added to the two AND gates that make them distance-one apart yet preserve the correctness of the circuit. Then, the distance-one-apart gates are merged. Checking that the first step preserves correctness can be a computationally expensive task and its implementation is deferred to Section 7. The second step, merging distance-one-apart gates in a sum-of-products, however, is always correctness-preserving. Once merged, inputs to the gate may become redundant which can be removed by subsequent optimizations.

#### 6.3 Signal network simplification

If the covers of either the set (reset) excitation regions of a signal u include their entire associated quiescent regions, then the set (reset) network is functionally equivalent to u. Unfortunately, even though the reset (set) network is not needed to implement signal u, it may still be necessary for acknowledgement of other internal signals. If all the acknowledgement wire forks attached to the reset (set) network can be relocated, the redundant logic can be removed. Specifically, u's reset (set) network and the C-element can be removed, reducing u's signal network to u's set (reset) network.

In addition, if the set and reset region networks of a signal network differ in phase the signal network can often be simplified. Consider the simplest case in which  $S_u = v_1 v_2$  and  $R_u = \overline{v_1} \overline{v_2}$ . In this case, the two AND gates can be removed and the inputs to the C-element are reassigned to  $S'_u = v_1$  and  $R'_u = v_2$ . Note that  $v_1$  and  $v_2$  may be outputs of other gates. In fact, when the set and reset networks consist of AND gates with more than 2-inputs, it is still possible to split the AND gate inputs while preserving correctness.

#### 6.4 Inverter bubble shuffling

An additional optimization technique is the shuffling of inverter bubbles [11]. Using DeMorgan's law, inverters can be pushed through gates, converting AND and OR gates to their duals. This is beneficial for two reasons. First NOR and NAND gates are smaller and faster than AND and OR gates in CMOS technology. Second, by applying this transformation, inverter bubbles on both ends of a wire can cancel out. Our CAD tool uses a simple greedy algorithm that finds a local optimum of inverter bubble placement.

# 7 Performing logic transformations and optimizations

Sharing of identical gates, signal network simplification, and bubble shuffling are guaranteed to be correctnesspreserving. The implementation of these techniques, therefore, is straight-forward. The other two optimization techniques, removing gate inputs and gate symmetrization, however, must be performed selectively to ensure hazards are not introduced. Similarly, adding acknowledgement wire forks must also be done selectively.

In fact, the impact of such logic transformations can be far from obvious and naive analysis techniques are computationally prohibiting. This section describes an algorithm that efficiently verifies that a logic transformation does not introduce new hazards into the circuit, i.e., is *non-hazard-increasing*.

#### 7.1 Overview