## Using Checking Experiments To Test Two-State Latches

Samy R. Makar and Edward J. McCluskey

| 94-11             | <b>Center for Reliable Computing</b><br>ERL 460                                                                  |

|-------------------|------------------------------------------------------------------------------------------------------------------|

| (CSL TR # 94-641) | Computer Systems Laboratory<br>Departments of Electrical Engineering and Computer Science<br>Stanford University |

| November 1995     | Stanford, California 94305-4055                                                                                  |

#### Abstract:

A general technique to determine conditions for exhaustive functional testing (checking experiment) of two-state latches is derived. This technique is used to derive conditions for checking experiments of various two-state latches. Minimum-length checking experiments are also presented. One of the checking experiments for the D-latch is simulated using an HSpice implementation of the transmission gate latch. All detectable shorted interconnects, open interconnects, short-to-power, short-to-ground, stuck-open, and stuck-on faults are detected. A pin fault test set and a multiplexer-based test set are also simulated. These tests miss some faults detected by the checking experiment.

## **Funding:**

This work was supported in part by the Ballistic Missile Defense Organization, Innovative Science and Technology (BMDO/IST) Directorate and administered through the Department of the Navy, Office of Naval Research under Grant No. N00014-92-J-1782, in part by the Advanced Research Projects Agency under Contract No. DABT63-94-C-0045, and in part by the National Science Foundation under Grant No. MIP-9107760. It was also funded in part by Cirrus Logic.

Imprimatur: Erin Kan and Jonathan Chang

Copyright © 1995 by the Center for Reliable Computing, Stanford University. All rights reserved, including the right to reproduce this report, or portions thereof, in any form.

## **Table of Contents**

| 1. Introduction                                          | 1  |

|----------------------------------------------------------|----|

| 2. Latches and Their Minimum-Length Checking Experiments | 2  |

| 3. Deriving Checking Experiments for Two-State Latches   | 4  |

| 3.1 Two-State SR-Latch                                   | 14 |

| 3.2 Two-State D-Latch                                    | 15 |

| 3.3 Two-State D-Latch With Asynchronous Set/Reset        | 16 |

| 3.4 Two-State MD-Latch                                   | 17 |

| 3.5 Two-State Two-Port Latch                             |    |

| 3.6 Two-State Load Enable Latch                          | 19 |

| 3.7 Two-State D-Enable Latch                             | 20 |

| 3.8 Two-State XOR Input Latch                            |    |

| 3.9 Two-State BILBO Latch                                | 22 |

| 3.10 Two-State CBILBO Latches                            |    |

| 4. D-Latch Simulation                                    | 25 |

| 5. Conclusions                                           | 32 |

| 6. Acknowledgments                                       | 32 |

| 7. References                                            | 32 |

| Appendix A Details of the Two-State MD-Latch             | 34 |

| Appendix B Details of the Two-State Two-Port Latch       | 35 |

| Appendix C Details of the Two-State Load Enable Latch    | 37 |

| Appendix D Details of the Two-State D-Enable Latch       | 38 |

| Appendix E Details of the Two-State BILBO Latch          | 40 |

| Appendix F Details of the Two-State CBILBO Latch         |    |

#### 1. Introduction

Tests for stuck-at faults at latch inputs and outputs miss many internal faults [Reddy 86], [Lee 90] and [Al-Assadi 93]. Reddy, in [Reddy 86], derived tests for stuck-open faults in different latch implementations. Lee, in [Lee 90], analyzed bridging faults in scan registers, and combined the use of current and voltage tests. Al-Assadi, in [Al-Assadi 93], mapped many, but not all, of the internal faults to functional fault models. He also showed that some of the internal faults cannot be mapped to functional fault models. What is needed is a test set that detects all faults (both internal and I/O faults). This paper presents such test sets.

A *checking experiment* is an input-output sequence that distinguishes a given state machine from all other state machines with the same inputs and outputs, and the same number of or fewer states. Checking experiments were first defined by Hennie as follows, "Any circuit that responds to the *checking experiment* in accordance with a given state table and starting state either must be operating correctly or else must have suffered a malfunction not in the given class." [Hennie 64]. The important property of a checking experiment is that it contains enough information to derive the flow table.

Even though Hennie's work was for pulse-mode circuits (often called synchronous sequential circuits), checking experiments can be derived for fundamental-mode circuits (often called asynchronous circuits) by modifying the procedure. Friedman, in [Friedman 71], discusses the restrictions in fundamental-mode circuits. Since there is no inherent clock, the machine can change state after any input changes, and the same input cannot be repeated. Also, for deterministic behavior, only one input can be changed at a time. Some faults can cause critical races, making the behavior non-deterministic, and can thus not be guaranteed to be detected. We did not encounter such faults in our simulations.

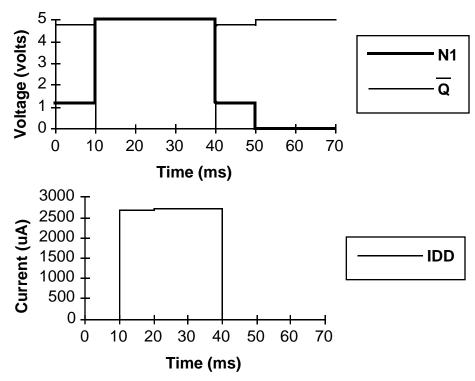

In Section 2, we present various latches and minimum-length checking experiments for them. In Section 3, we present a general technique for deriving checking experiments for twostate latches. Separate sub-sections are devoted to the derivation of checking experiment requirements and minimum-length checking experiments for each latch type, with details given in the appendices. The checking experiment for the D-latch was simulated in HSpice using a transmission gate implementation. The results of this simulation are compared with those of a pin fault test set and a multiplexer-based test set in Section 4.

#### 2. Latches and Their Minimum-Length Checking Experiments

Various latches are discussed in this paper (see Table 2-1). The simplest latch type is the SR-latch. An *SR-latch* is a sequential element that can be set or reset by activating the appropriate input. Even though the SR-latch is still occasionally used, the most commonly used latch today is the D-latch. A *D-latch* is a sequential element, in which the data input is propagated to the output when the clock is active, otherwise it holds the stored value. A *D-latch with Asynchronous Set/Reset* is a D-latch that can be set or reset when the clock is not active. Scan-paths require latches with two different data sources. These can be either Multiplexed-Data latches or Two-Port latches. A *Multiplexed-Data latch (MD-latch)* is a D-latch with multiplexed data inputs; a *Two-Port latch* has two control inputs with the data source determined by the active control input [McCluskey 86]. A *Load Enable latch* is a D-latch with a gated control input, and a *D-Enable latch* is a D-latch with gated data. An *XOR Input latch* performs an exclusive-or operation on its two data inputs. This latch is commonly used in an LFSR to generate pseudo-random vectors, and to compress results. Other latches commonly used for BIST are the *Built-In Logic Block Observer latches*). The BILBO latch has two data inputs. It can

| Latch Type                             | <b>Excitation Function</b>                                                                                                        | Assumptions       | M* |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|----|

| SR-Latch                               | $Q = S + \overline{R}q$                                                                                                           | SR = 0            | 6  |

| D-Latch                                | $Q = CD + \overline{C}q$                                                                                                          |                   | 7  |

| D-Latch with<br>Asynchronous Set/Reset | $Q = \overline{R}(S + CD + \overline{C}q)$                                                                                        | $\mathbf{SR} = 0$ | 14 |

| MD-Latch                               | $\mathbf{Q} = \mathbf{C}(\mathbf{T}\mathbf{S} + \overline{\mathbf{T}}\mathbf{D}) + \overline{\mathbf{C}}\mathbf{q}$               |                   | 26 |

| Two-Port Latch                         | $\mathbf{Q} = \mathbf{C}_1 \mathbf{D}_1 + \mathbf{C}_2 \mathbf{D}_2 + \overline{\mathbf{C}_1} \overline{\mathbf{C}_2} \mathbf{q}$ | $C_1C_2 = 0$      | 23 |

| Load Enable Latch                      | $Q = CLD + \overline{(LC)}q$                                                                                                      |                   | 15 |

| D-Enable Latch                         | $Q = CDE + \overline{C}q$                                                                                                         |                   | 16 |

| XOR Input Latch                        | $Q = C(D \oplus S) + \overline{C}q$                                                                                               |                   | 13 |

| BILBO Latch                            | $Q = C(B_1D \oplus \overline{B_2}S) + \overline{C}q$                                                                              |                   | 58 |

| CBILBO Latch                           | $Q_1 = C(\overline{B_1}D \oplus S) + \overline{C}q_1$                                                                             |                   | 25 |

|                                        | $Q_2 = C(B_2S + \overline{B_2}D) + \overline{C}q_2$                                                                               |                   | 26 |

**Table 2-1 Latches and Their Excitation Functions.**

\*M - minimum length of checking experiment.

be configured to load either of the two inputs (one a scan input, and the other for normal operation), load the exclusive-or of the two inputs (for signature analysis), or load 0. The CBILBO latches, an extension of the BILBO latch, are two latches that can operate simultaneously as a pseudo-random pattern generator and a signature analyzer. The two latches are treated separately, with outputs Q1 and Q2. Table 2-1 shows the excitation function of each of these latches and the minimum-length of a checking experiment. Minimum-length checking experiments for each of these latches are shown in Tables 2-2 through 2-11. Details for each latch type are presented in Section 3.

Table 2-2 A Minimum-Length (6) Checking Experiment for SR-Latch.

| S | 0 | 0 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|

| R | 1 | 0 | 0 | 0 | 1 | 0 |

| Q | 0 | 0 | 1 | 1 | 0 | 0 |

Table 2-3 A Minimum-Length (7) Checking Experiment for D-Latch.

| С | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

|---|---|---|---|---|---|---|---|

| D | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

# Table 2-4 A Minimum-Length (14) Checking Experiment for Asynchronous Set/Reset Latch.

| С | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| D | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| R | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| S | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| Q | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

## Table 2-5 A Minimum-Length (26) Checking Experiment for MD-Latch.

| D | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| Т | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| С | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| Q | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

## Table 2-6 A Minimum Length (23) Checking Experiment for Two-Port Latch.

| D1         | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

|------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Cī         | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| $D_2$      | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| $C\bar{2}$ | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0          | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

## Table 2-7 A Minimum-Length (15) Checking Experiment for Load Enable Latch.

| L | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| D | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| С | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| D | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| E | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| С | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

#### Table 2-8 A Minimum-Length (16) Checking Experiment for D-Enable Latch.

#### Table 2-9 A Minimum-Length (13) Checking Experiment for XOR Input Latch.

| D |        | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

|---|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S |        | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| C | l<br>, | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| Q |        | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

## Table 2-10 A Minimum-Length (58) Checking Experiment for BILBO Latch.

| D                     | 0 | 0 | 0 | 0 | 0 | 0   | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0                 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

|-----------------------|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-------------------|---|---|---|---|---|---|---|---|

| S                     | 0 | 0 | 0 | 0 | 0 | 0   | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0                 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| B2                    | 0 | 0 | 0 | 0 | 0 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1                 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| $B_1$                 | 0 | 1 | 1 | 0 | 0 | 0   | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0                 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| С                     | 1 | 1 | 0 | 0 | 1 | 0   | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0                 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| Q                     | 1 | 0 | 0 | 0 | 1 | 1   | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0                 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

| D                     | 1 | 1 | 1 | 1 | 1 | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1                 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| S                     | 1 | 1 | 1 | 0 | 0 | 0   | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1                 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| B2                    | 0 | 0 | 0 | 0 | 0 | 0   | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1                 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| <b>B</b> <sub>1</sub> | 0 | 0 | 0 | 0 | 0 | 0   | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1                 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| С                     | 0 | 1 | 0 | 0 | 1 | 0   | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |   | 0 | 0                 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

|                       |   | 0 | 0 | 0 |   | - 1 | 4 | 0 | 0 | 0 | 4 | 4 | 0 | 0 | 0 | 4 | 4 | 1 | 0 | 0 | $\mathbf{\Omega}$ | 4 | 1 | 4 | 4 | 4 | 4 | 0 | 0 |

## Table 2-11a A Minimum-Length (25) Checking Experiment for CBILBO Latch 1.

| D  | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S  | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| B1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Ċ  | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| Q1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

Table 2-11b A Minimum-Length (26) Checking Experiment for CBILBO Latch 2.

| D  | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| B2 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Ċ  | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| Q2 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

## 3. Deriving Checking Experiments for Two-State Latches

All latches described in Table 2-1 are typically implemented as two-state latches; the flow tables of these latches have only two rows. In this section, special properties of two-state flow tables are analyzed and a method for generating checking experiments for them is developed. This method was used to generate the checking experiments in Tables 2-2 through 2-11. The details are presented in sub-sections of this section.

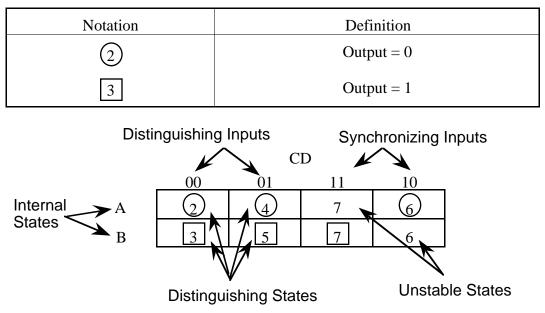

Each cell in a flow table, a *total state*, corresponds to an assignment of values to the circuit inputs and internal states. A total state is an *unstable state* if it causes a change in internal state of the machine. A total state is a *stable state* if the next internal state is the same as the current internal state. The notation used in this paper for stable total states is shown in Table 3-1. A total state is *unspecified* if it is not adjacent to a stable total state. Such states cannot be reached because of the single-input change restriction on fundamental mode circuits [McCluskey 86]. Unspecified states are shown with "–" in the flow tables. A sequence *visits* a total state of the total state. A total state is *identified* by a sequence if the sequence provides enough information to reconstruct the corresponding entry in the flow table.

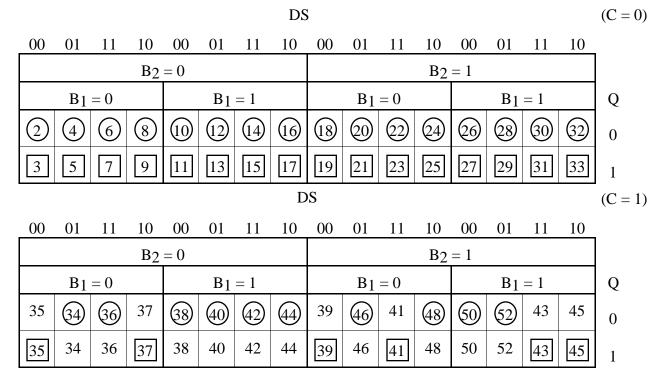

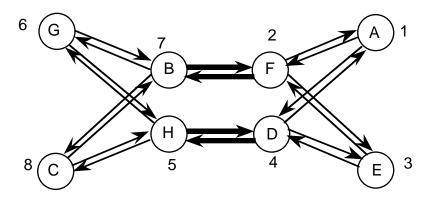

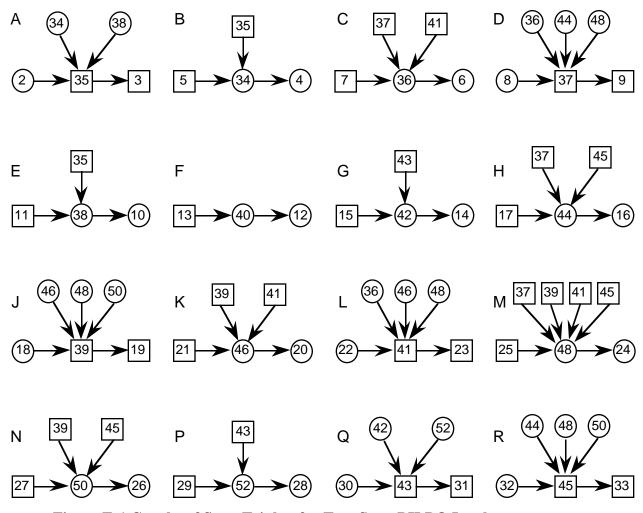

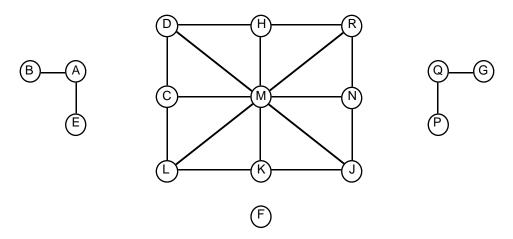

For a state machine to have sequential behavior, there must be at least one column in the flow table with different outputs. Otherwise, the machine acts as pure combinational logic. The total states in a column of a two-state flow table with differing outputs are called *distinguishing states*, and the input is called a *distinguishing input*. A state machine must also have two columns that change the internal state, so that both internal states are reachable. Inputs of such columns are called *synchronizing inputs* because they force the machine into a known state. These definitions are shown in Fig. 3-1.

As mentioned earlier, a checking experiment contains enough information to reconstruct the flow table. Therefore, it must identify all total states in the flow table. In this paper, we analyze flow tables that have distinguishing inputs and synchronizing inputs only (i.e. no

**Figure 3-1 Definitions in Flow Table.**

columns in the table have two stable states with the same output), because all latches studied here have flow tables that fall into this class of flow tables. The requirement for reconstructing the flow table can be refined into three simpler requirements (proof of this will come later): all total states must be visited, all unstable states must be identified, and all distinguishing states must be identified.

We start with the first requirement, all total states must be visited. If a total state is not visited by the sequence, then the effect of applying the input of the total state when the machine is in the internal state of the total state is not known. This requirement is proven in Lemma 1.

**Lemma 1:** A checking experiment for a two-state flow table with only distinguishing and synchronizing inputs must visit all total states in the flow table.

*Proof*: Suppose that a sequence does not visit one of the stable total states. Create a second flow table by copying the original flow table and changing the output of the state not visited by the sequence. The output response of the sequence when applied to the second flow table would be the same as that of the original one because the sequence never enters the only total state that differs in the two flow tables. Since the two flow tables give the same response to the same input sequence, the sequence cannot be a checking experiment. Now suppose that the sequence does not visit one of the unstable states. In this case, the sequence would have the same response for a flow table that had the unstable total state replaced by a stable total state (the output does not matter). Since the input sequence has the same response for two flow tables, it cannot be a checking experiment. Therefore, a checking experiment must visit all total states (stable and unstable) in the flow table.

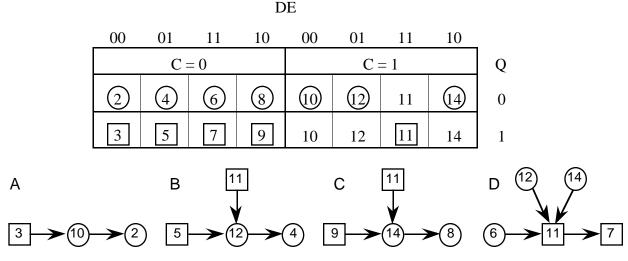

Even though visiting all the total states is a necessary requirement for a checking experiment, it is not a sufficient one. Consider the flow tables in Table 3-2. The sequence in Table 3-2c visits all the states of the two flow tables, Tables 3-2a and 3-2b, but the output response is the same for the two flow tables. Since the two flow tables are different, the sequence is not a checking experiment. Assuming that the flow table in Table 3-2a is the desired flow table, the sequence did not identify the unstable states 8 and 9. An unstable state is identified, when the sequence shows that the input caused a change in internal state. To show that an input causes a change in internal state, we need to show that the total states before and after the application of the input have different internal states. The internal state after the application of the input can be identified by following the input with a distinguishing input. The total state would then be a distinguishing state, but its internal state must be known. This analysis suggests the creation of state triples. A *state triple* is a set of three total states that contains the *setup state* (same internal state as unstable state and input unit distance from unstable state input), the total state associated with the unstable state, and a distinguishing state. The setup state and the distinguishing state must have different internal states. The last state of the triple is a distinguishing state. Visiting a distinguishing state does not change the internal state of the machine.

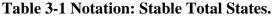

Table 3-2a Two-State Flow Table.

|     |       |     | C   | D   |     |    |    |

|-----|-------|-----|-----|-----|-----|----|----|

| 00  | 01    | 11  | 10  | 00  | 01  | 11 | 10 |

|     | A     | =0  |     |     | A   | =1 |    |

| 2,0 | (4),0 | 7   | 6,0 | 9   | 8,0 |    |    |

| 3,1 | 5,1   | 7,1 | 6   | 9,1 | 8   |    |    |

Table 3-2b Another Flow Table That Produces Same Output Sequence WhenTable 3-2c Sequence Is Applied.

Table 3-2c Sequence That Visits All Total States, But Is Not A Checking Experiment.

| Α     | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

|-------|---|---|---|---|---|---|---|---|

| С     | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| D     | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

| Q     | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| State | 7 | 5 | 3 | 6 | 2 | 4 | 8 | 9 |

**Lemma 2:** A checking experiment for a two-state flow table with only distinguishing and synchronizing inputs must identify all unstable states.

*Proof*: An unstable state is identified by a sequence if the sequence successively visits the three states of a triple corresponding to the unstable state. We have already shown that a checking experiment must visit all the total states, including the unstable states. Visiting an unstable state implies visiting the setup state and the unstable state of the triple. Therefore, a sequence that visits an unstable state but does not identify it is not visiting a distinguishing state after visiting the

unstable state (i.e. it only visits the first two states of the triple). In this case, the input applied by the sequence after visiting the unstable state is a synchronizing input. Create a second flow table by copying the original flow table and changing the unidentified unstable state to a stable total state and give it the same output of the other total state in the same column. When the input corresponding to our unstable state is applied to either flow table, we get the same output. Since the next input is a synchronizing input, the next output and internal state will be the same for both flow tables. Therefore, a checking experiment must identify all unstable transitions.

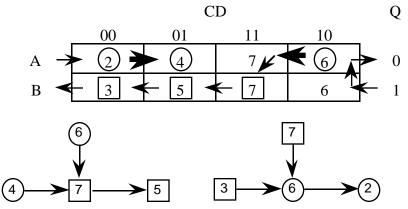

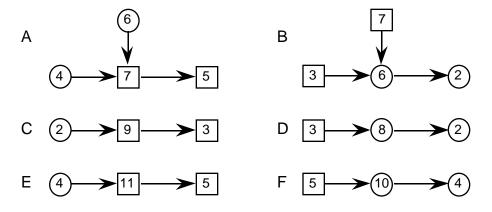

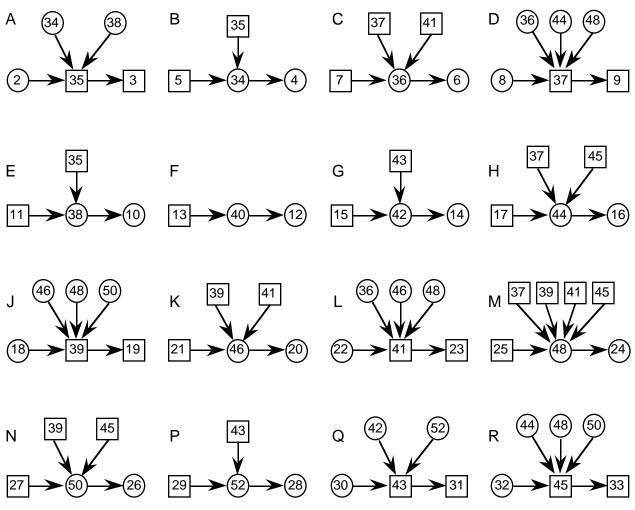

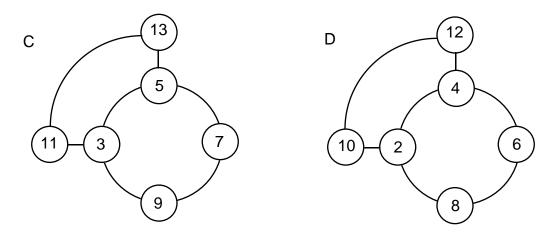

Consider the flow tables in Table 3-3. Graphs for the state triples of Table 3-3a are shown in Fig. 3-2. The sequence shown in Table 3-3c visits all the total states, and identifies all the unstable states. However, both flow tables in Tables 3-3a and 3-3b, produce the same output response for the input sequence of Table 3-3c.

The sequence in Table 3-3c produces different outputs for both 00 and 01, indicating that they are distinguishing inputs. However, there are two possible permutations (barring isomorphism) for the distinguishing states in the flow table. These are shown in the first two columns of Tables 3-3a and 3-3b. To distinguish between the two flow tables, a sequence must have CD = 00,01 or CD = 01,00 as sub-sequences.

#### Table 3-3a Two-State Flow Table.

|   |     |       |     | С   | D   |     |    |    |

|---|-----|-------|-----|-----|-----|-----|----|----|

| 0 | 0   | 01    | 11  | 10  | 00  | 01  | 11 | 10 |

|   |     | A     | =0  |     |     | A   | =1 |    |

| 2 | ),0 | (4),0 | 7   | 6,0 | 9   | 8,0 | _  | _  |

| 3 | ],1 | 5,1   | 7,1 | 6   | 9,1 | 8   | _  | -  |

Table 3-3b Another Flow Table That Produces Same Output Sequence WhenTable 3-3c Sequence Is Applied.

|     |       |     | C   | D   |     |    |    |

|-----|-------|-----|-----|-----|-----|----|----|

| 00  | 01    | 11  | 10  | 00  | 01  | 11 | 10 |

|     | A     | =0  |     |     | A   | =1 |    |

| 2,0 | 5,1   | 7,1 | 6,0 | 9   | 8   | Ι  | _  |

| 3,1 | (4),0 | 7   | 6   | 9,1 | 8,0 |    | _  |

|   | А       | 0 | 0 | 1   | 0     | 0   | 0    | 0           | 0 | 0    | 1   | 0 |

|---|---------|---|---|-----|-------|-----|------|-------------|---|------|-----|---|

|   | С       | 1 | 0 | 0   | 0     | 1   | 0    | 1           | 1 | 0    | 0   | 0 |

|   | D       | 1 | 1 | 1   | 1     | 1   | 1    | 1           | 0 | 0    | 0   | 0 |

|   | Q       | 1 | 1 | 0   | 0     | 1   | 1    | 1           | 0 | 0    | 1   | 1 |

|   | State   | 7 | 5 | 8   | 4     | 7   | 5    | 7           | 6 | 2    | 9   | 3 |

|   | Triples |   |   | А   |       |     |      |             |   |      | D   |   |

|   | -       |   |   |     |       | В   |      |             | С |      |     |   |

| A |         |   | В |     |       | С   |      |             | [ | )    | -   |   |

| 5 | →8      |   | 4 | ->7 | ·]->[ | 5 3 | ]->( | 6 <b>)→</b> | 2 | 2)-> | 9 → | 3 |

Table 3-3c Sequence That Visits All Total States, Identifies Unstable States, But Is Not A Checking Experiment.

Figure 3-2 Graphs of State Triples for Flow Table in Table 3-3a.

This brings us to the third requirement: identifying the distinguishing states. As shown in this example, it is not enough to visit the distinguishing states. Two distinguishing inputs are said to be *linked* in a sequence, if the sequence provides enough information to determine the order of the distinguishing states in their two columns. If a distinguishing input follows another distinguishing input in the sequence, and the distinguishing states of both inputs are visited, then the two are linked. However, there can be many distinguishing inputs. Every distinguishing input can have one of two possible permutations of distinguishing states. Therefore, for n distinguishing inputs there are 2<sup>n</sup> possible column permutations. Half of these permutations are nothing more than other permutations with the rows exchanged. Thus they do not need to be considered, and there are  $2^{n-1}$  possible unique permutations. For a single distinguishing input, there is one unique permutation. Therefore, any distinguishing input is linked to itself, making the link relation reflexive. From the definition of link, link is a symmetric property. If a is linked to b, then b is linked to a. Now suppose that there are three distinguishing inputs a, b and c. If a is linked to b, then there is only one unique permutation for the distinguishing states in columns of a and b. Similarly, if a is linked to c, then there is only one unique permutation for the distinguishing states in columns of a and c. Therefore, there is one unique permutation for the all three columns, and so the link relationship is transitive. Since the link relationship is reflexive, symmetric, and transitive, it must be an equivalence relationship.

If a sequence links all pairs of distinguishing inputs then there can only be one permutation of the distinguishing states, and all distinguishing states are identified. Since the link relationship is an equivalence relationship, it suffices to show that the distinguishing inputs are all members of the same equivalence class. Therefore, distinguishing states are identified if they are all visited, and if they are all linked to each other. **Lemma 3:** A checking experiment for a two-state flow table with only distinguishing and synchronizing inputs must identify all distinguishing states.

*Proof*: Distinguishing states are identified by a sequence if the sequence visits the states, and if all the distinguishing inputs are linked. We have already shown that a checking experiment must visit all the total states, including the distinguishing states. Suppose that two distinguishing inputs are not linked in a sequence. Since link is an equivalence relation between distinguishing inputs, the distinguishing inputs would fall into two equivalence classes. Within each of the classes, there is only one unique permutation of distinguishing states. Create a second flow table by copying the original flow table, and swapping the rows in the distinguishing input columns of one of the equivalence classes. Also, swap the rows of any synchronizing inputs that are a unit distance from any of the distinguishing inputs in that class. Applying the sequence to the new flow table would give the same response as when applied to the original flow table. Therefore, if the distinguishing inputs are not linked in a sequence, the sequence is not a checking experiment.

Now that we have shown that the three conditions (visiting all states, identifying all unstable states, and identifying all distinguishing states) are necessary for a sequence to be a checking experiment, we show that if all three conditions are satisfied that the sequence is a checking experiment. In other words, given a two-state flow table with distinguishing and synchronizing inputs, any sequence that satisfies all three conditions is guaranteed to be a checking experiment. These conditions are necessary and sufficient. The proof is given in Theorem 1. Lemma 2 and Lemma 3 showed that visiting a state was necessary to identify it. Thus visiting a state can be eliminated as an explicit condition for a sequence to be a checking experiment. However, the condition is retained here just for emphasis.

### **Theorem 1**: A sequence for a two-state machine with distinguishing and synchronizing

inputs is a checking experiment if and only if it satisfies the following properties: 1. Visits all the total states.

- 2. Identifies all the unstable states.

- 3. Identifies all the distinguishing states.

*Proof*: From Lemmas 1, 2 and 3, a checking experiment must satisfy all the above conditions. Now, we need to show that if a sequence satisfies the three conditions, then it is a checking experiment. If a sequence identifies all the distinguishing states, then there can only be one permutation of distinguishing states in the flow table. If the sequence also identifies all the unstable states, then all entries in the flow table are identified. Therefore only one flow table can be constructed from the response of the sequence, making it a checking experiment.

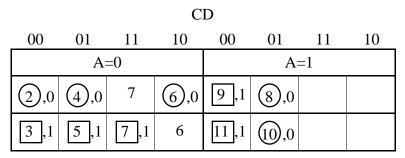

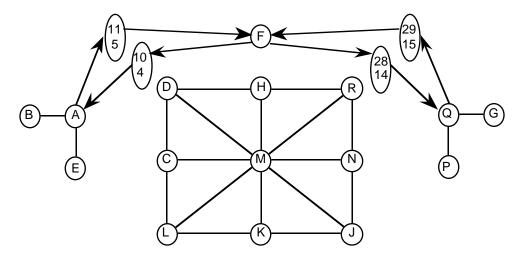

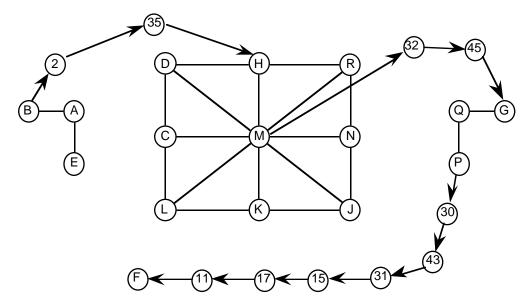

An important consequence of Theorem 1 is that a checking experiment does not have to ensure all possible transitions in a two-state flow table. For example, consider the flow table in Table 3-4. The graphs of the triples are shown in Fig. 3-3. A sequence formed by combining the triples is 6,7,5,3,6,2. Since state 3 follows state 5, the distinguishing inputs are linked. State 4 can be added to the end of the sequence to satisfy the first requirement of Theorem 1. Therefore, the state sequence becomes: 6,7,5,3,6,2,4. The transitions through this sequence are shown graphically in Table 3-4. Thick arrows are used to indicate the beginning and end of the sequence. The following six transitions are not included in this sequence:  $4 \rightarrow 2$ ,  $2 \rightarrow 6$ ,  $4 \rightarrow 7$ ,  $3 \rightarrow 5$ ,  $5 \rightarrow 7$ , and  $7 \rightarrow 6$ .

#### Table 3-4 Flow Table Marked With Checking Sequence.

Figure 3-3 Graph of Triples for Flow Table in Table 3-4.

From Theorem 1, the following procedure can be used to generate a checking experiment for a two-state flow table with distinguishing and synchronizing inputs.

#### Procedure for deriving checking experiments from two-state flow tables.

- 1. Determine all the state triples for the unstable states.

- 2. Combine the triples of step 1.

- 3. If the sequence resulting from step 2 does not form a link among all the distinguishing inputs then modify the sequence so that it does, without destroying the triples.

- 4. Add any missing total states to the sequence.

- 5. Convert the state sequence into an input sequence, adding a synchronizing input, if necessary.

The first pattern in the sequence for a two-state flow table should force the machine into a known state. Therefore, in step 2 of the procedure, the setup state of the first triple should correspond to a synchronizing input whenever possible.

Combining triples would be most efficient if the distinguishing state of one triple is the setup state of another. Since triples cause a change in the internal state, the final state of one triple can be the setup state of another if the two triples cause internal state changes in the opposite directions (i.e. if the first triple causes the machine to change from internal state A to internal state B, then the second triple should cause the machine to change from internal state B back to internal state A). If there are more triples that cause state changes in one direction than in the other, then some of the state changes will need to be repeated in order to get to the setup states of all the triples.

**Lower Bound on Sequence Length of Two-State Latches:** The length of a checking experiment (L) is bound by the following equation.

$$L \ge S + 1 + \sum_{i=0}^{S} \max(n_{i} - 1, 0) \quad \text{if } v = 0$$

$$L \ge S + v + \sum_{i=0}^{S} \max(n_{i} - 1, 0) \quad \text{if } v > 0$$

where S = number of total States

$n_i$  = number of times state i appears as the only distinguishing state of a triple

v = difference between the number of unstable states in the two rows *Proof*: As seen from Lemma 1, a checking experiment must visit every total state. A machine can only be in one stable total state for every input pattern. Therefore, there must be at least as many patterns in the sequence as there are total states. There will always be at least one extra pattern for initialization. To be useful, the first pattern should force the machine into a known state (a synchronizing input). If a state  $s_i$  appears as the only distinguishing state of  $n_i$  triples, then  $s_i$  must appear at least  $n_i$  times. One of the occurrences of state  $s_i$  is accounted for in S (the total number of states). Therefore  $s_i$  must appear an additional  $n_i - 1$  times. If  $s_i$  never appears as the only distinguishing state of a triple, then nothing should be added. Hence the term max( $n_i - 1,0$ ) is added for each total state. If the number of unstable states in one row differs from the number of unstable states in the other row by v, then at least v - 1 extra internal state changes have to be applied. Each extra state change requires at least one more pattern. Adding v - 1 to the initialization pattern gives v.

In many of the latch flow tables, half the inputs are distinguishing inputs, and the other half are synchronizing inputs. A single input variable determines whether an input is a

distinguishing input or a synchronizing input. This class of state machines will be referred to as *single-input control state machines*, and the variable that determines the input type will be called a *control input*. For example, in Table 3-4, all inputs are distinguishing inputs when C = 0, and all inputs are synchronizing inputs when C = 1. Therefore, the flow table describes a single-input control state machine with C as the control input. An interesting property of such state machines is that the distinguishing state of one triple cannot be a setup state of another triple, because there are no unstable states adjacent to a distinguishing state of a triple. Therefore, if there are *v* more unstable states in one row than in the other, then 2(v - 1) extra patterns are needed. This is used to derive a tighter lower bound on the length of the checking experiment.

## **Lower Bound on Sequence Length of Single-Input Control State Machine**: The length of a checking experiment (L) of a Single-Input Control State Machine is

bound by

| $L \ge S + 1$      | if $v = 0$ |

|--------------------|------------|

| $L \ge S + 2v - 1$ | if v > 0   |

where S = number of total States

v = difference between the number of unstable states in the two rows *Proof*: The distinguishing state of one triple cannot be the setup state of another triple, because there are no unstable states adjacent to a distinguishing state of a triple. Therefore, the summation term in the original bound will always be 0. If v = 0, then the arguments for the previous bound apply. If v = 1, then two patterns are needed for each additional transition. Therefore 2(v - 1) extra patterns are needed. Combining this with the initialization pattern gives 2v - 1.

Another property of single-input control state machines is that a sequence that uses distinguishing states as setup states for all except the first triple, will identify the distinguishing states as well as the unstable states. This property is proved in Theorem 2.

**Theorem 2:** If a sequence is applied to a single-input control state machine, and the setup states of all but the first triple are distinguishing states, then the sequence links all the distinguishing inputs.

*Proof*: In a single-input control state machine each distinguishing input has a distinguishing state that is a setup state of a triple, and another distinguishing state that is a distinguishing state of the same triple. Therefore, there is a one-to-one correspondence between distinguishing inputs and triples. Now, if triple B is applied after triple A, the distinguishing input corresponding to triple A is linked to the one corresponding to triple B. Suppose triple C is applied after triple B,

then the distinguishing input corresponding to triple B is linked to the one corresponding to triple C. Since link is an equivalence relation, the distinguishing input corresponding to triple A is linked to the one corresponding to triple C. Using the same arguments, it can be shown that the distinguishing input corresponding to triple A is linked to all the distinguishing inputs. Therefore, the sequence links all the distinguishing inputs.

#### 3.1 Two-State SR-Latch

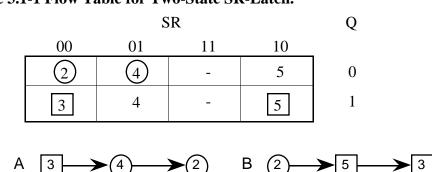

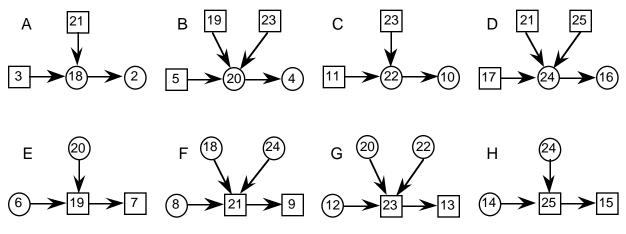

The equation for the SR-latch is  $Q = S + \overline{R}q$ . The latch is set when S = 1 and reset when R = 1. S and R should not be 1 at the same time. The flow table for the SR-latch is shown in Table 3.1-1. The graphs of the state triples are shown in Fig. 3.1-1.

Table 3.1-1 Flow Table for Two-State SR-Latch.

Figure 3.1-1 Graphs of State Triples for Two-State SR-Latch.

The setup state of one triple is the distinguishing state of the other triple. Therefore, the two triples can be combined without adding any states between them. Two possible state sequences are 2,5,3,4,2 and 3,4,2,5,3. Since there is only one distinguishing input, the distinguishing states are identified by simply visiting them. The two sequences contain all the total states in the flow table. The input sequence that would generate these state sequences is shown in Table 3.1-2. Since the sequences satisfy Theorem 1, they are checking experiments.

Table 3.1-2 Minimum-Length (6) Checking Experiments for Two-State SR-Latch.

| S       | 0 | 0 | 1 | 0 | 0 | 0 | S       | 1 | 0 | 0 | 0 | 1 | 0 |

|---------|---|---|---|---|---|---|---------|---|---|---|---|---|---|

| R       | 1 | 0 | 0 | 0 | 1 | 0 | R       | 0 | 0 | 1 | 0 | 0 | 0 |

| Q       | 0 | 0 | 1 | 1 | 0 | 0 | Q       | 1 | 1 | 0 | 0 | 1 | 1 |

| State   | 4 | 2 | 5 | 3 | 4 | 2 | State   | 5 | 3 | 4 | 2 | 5 | 3 |

| Triples |   |   | В |   |   |   | Triples |   |   | А |   |   |   |

|         |   |   |   |   | А |   |         |   |   |   |   | В |   |

Since the setup state in both triples is a distinguishing state, a synchronizing input needs to be added to the beginning of either sequence. The sequences in Table 3.1-2 are minimum length.

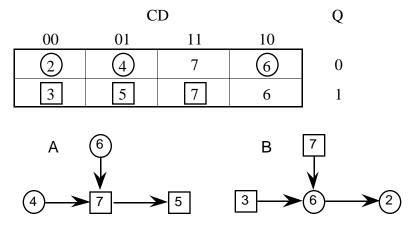

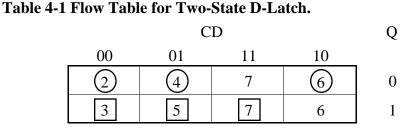

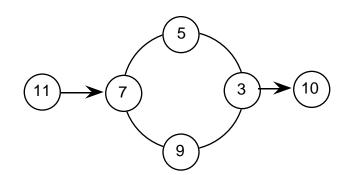

#### 3.2 Two-State D-Latch

The equation for a D-latch is  $Q = CD + \overline{C}q$ , and the flow table for the D-latch is shown in Table 3.2-1. The graphs of the state triples are shown in Fig. 3.2-1. The two triples can be combined in any order. Suppose we start with the triple A. The first part of the state sequence is 6,7,5 (state 6 is picked because it is a synchronizing input). Now, looking at triple B, there are two choices: 7,6,2 or 3,6,2. State 7 has already been entered in the first sequence, thus entering it again has no benefit. Choosing state 3 as the setup state would make state 3 follow state 5, linking the two distinguishing inputs. Thus the sequence becomes 6,7,5,3,6,2. The sequence is missing state 4, which can be added to the end of the sequence. This makes the final sequence 6,7,5,3,6,2,4. The same approach can be used starting with triple B in Fig. 3.2-1. The sequence in that case would be 7,6,2,4,7,5,3. These two state sequences, and the checking experiments that would generate them, are shown in Table 3.2-2. Since the lengths of these sequences meet the lower bound, these sequences are minimum length.

Table 3.2-1 Flow Table for Two-State D-Latch.

Figure 3.2-1 Graphs of State Triples for Two-State D-Latch.

| -       |   |   |   |   |   |   |   | 1       |   |   |   |   |   |   |   |

|---------|---|---|---|---|---|---|---|---------|---|---|---|---|---|---|---|

| С       | 1 | 1 | 0 | 0 | 1 | 0 | 0 | С       | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| D       | 1 | 0 | 0 | 1 | 1 | 1 | 0 | D       | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| Q       | 1 | 0 | 0 | 0 | 1 | 1 | 1 | Q       | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

| State   | 7 | 6 | 2 | 4 | 7 | 5 | 3 | State   | 6 | 7 | 5 | 3 | 6 | 2 | 4 |

| Triples |   | В |   |   | А |   |   | Triples |   | А |   |   | В |   |   |

Table 3.2-2 Minimum-Length (7) Checking Experiments for Two-State D-Latch.

#### 3.3 Two-State D-Latch With Asynchronous Set/Reset

The equation for the D-latch with Asynchronous Set/Reset is  $Q = \overline{R}(S + CD + \overline{C}q)$ . The latch is set when S = 1 and reset when R = 1. S and R should not be 1 at the same time, and neither should be 1 when C = 1. When both R and S are 0, the latch behaves exactly like a D-latch. The flow table for this latch is shown in Table 3.3-1, and graphs of the state triples are shown in Fig. 3.3-1.

| 00 | 01            | 11 | 10  | 00  | 01 | 11 | 10 | 00 | 01         | 11  | 10  | 00  | 01         | 11  | 10 |   |

|----|---------------|----|-----|-----|----|----|----|----|------------|-----|-----|-----|------------|-----|----|---|

|    |               |    | R = | = 0 |    |    |    |    |            |     | R = | = 1 |            |     |    |   |

|    | S = 0 $S = 1$ |    |     |     |    |    |    |    | <b>S</b> = | = 0 |     |     | <b>S</b> = | = 1 |    | Q |

| 2  | 4             | 7  | 6   | 9   | 11 | I  | -  | 8  | 10         | -   | -   | -   | I          | -   | -  | 0 |

| 3  | 5             | 7  | 6   | 9   | 11 | -  | -  | 8  | 10         | -   | -   | -   | -          | -   | -  | 1 |

Table 3.3-1 Flow Table for Two-State Asynchronous Set/Reset Latch.CD

In Fig. 3.3-1 only the first two triples have synchronizing setup states. Therefore, a minimum-length sequence should start with one of these two triples. There are ten total states, and state 2 and state 5 appear twice as the only distinguishing inputs of state triples. From the first bound derived in Section 3, the minimum test length must be at least 13. State 4 and state 3 appear twice as setup states. However, in the first two triples there are alternate setup states. If these are used, then one of them could be the synchronizing input, but the other would appear twice in the sequence, raising the minimum length to 14. One such sequence is shown in Table 3.3-2. Since state 4 directly follows state 2, the distinguishing inputs are linked.

Figure 3.3-1 Graphs of State Triples for Two-State D-Latch With Asynchronous Set/Reset.

| С       | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0  | 0 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|----|---|----|---|---|---|

| D       | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1  | 1 | 1  | 1 | 1 | 1 |

| R       | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0  | 0 | 1  | 0 | 0 | 0 |

| S       | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1  | 0 | 0  | 0 | 0 | 0 |

| Q       | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1  | 1 | 0  | 0 | 1 | 1 |

| State   | 7 | 6 | 2 | 9 | 3 | 8 | 2 | 4 | 11 | 5 | 10 | 4 | 7 | 5 |

| Triples |   | В |   |   |   | D |   |   |    |   | F  |   |   |   |

|         |   |   |   | С |   |   |   |   | Е  |   |    |   | А |   |

Table 3.3-2 A Minimum-Length (14) Checking Experiment for Asynchronous Set/Reset Latch.

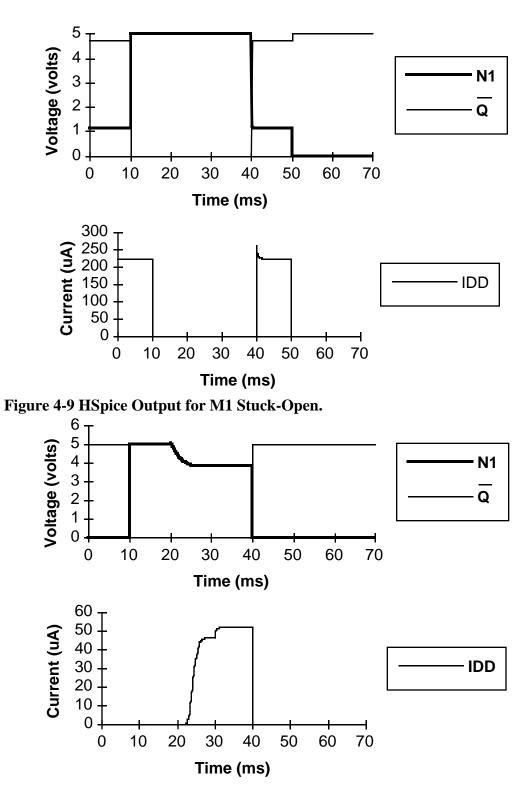

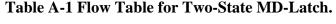

#### 3.4 Two-State MD-Latch

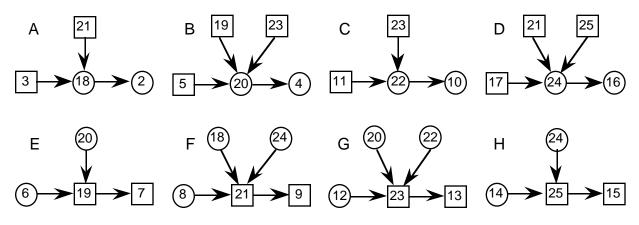

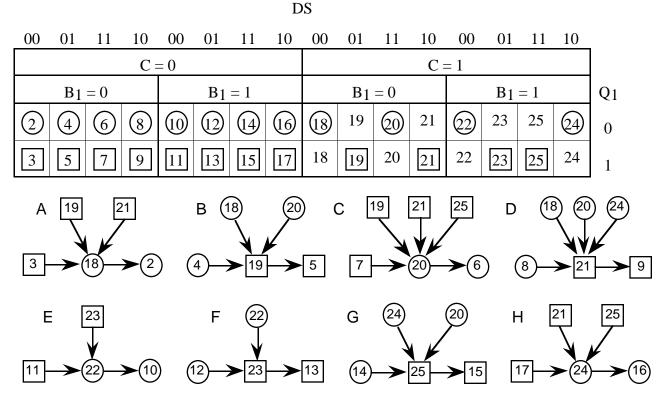

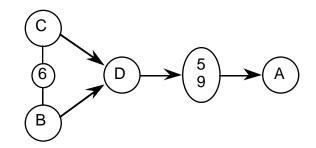

The equation for an MD-latch (Multiplexed-Data latch) is  $Q = C(TS + \overline{T}D) + \overline{C}q$ . When T = 0, the latch operates in normal mode (D is used as the input), and when T = 1 it uses S as input. The flow table for the MD-latch is given in Table 3.4-1. The graphs of the triples are shown in Fig. 3.4-1.

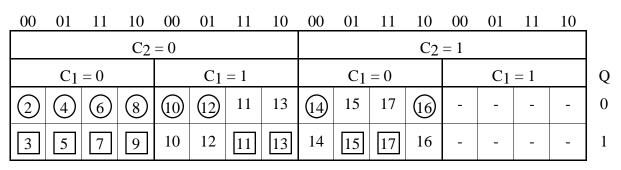

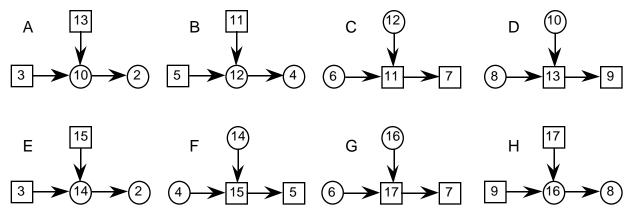

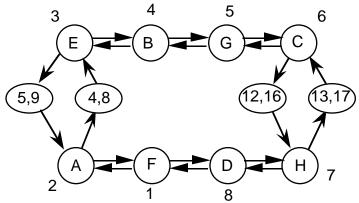

Looking at the flow table, all the distinguishing states occur when C = 0, and all the unstable states occur when C = 1. Therefore, the MD-latch is a single-input control state machine, and C is the control input. There are 24 total states, and the number of unstable states in each of the rows is 4. Therefore, the length of a checking experiment must be at least 25. Appendix A shows that the length must be at least 26. The details of combining the triples to derive minimum-length sequences also appear in Appendix A. One such sequence is shown in Table 3.4-2.

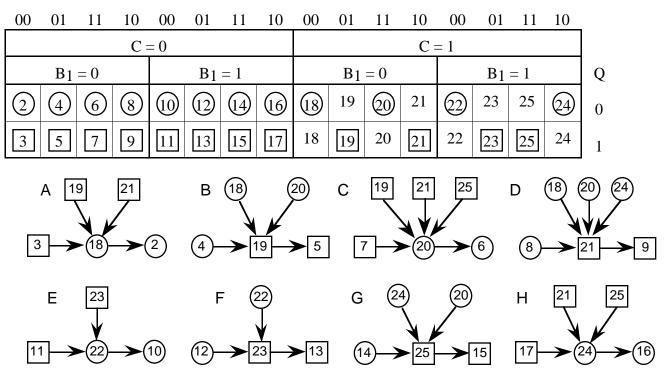

#### Table 3.4-1 Flow Table for Two-State MD-Latch.

DS

| 00 | 01         | 11  | 10  | 00  | 01   | 11   | 10   | 00 | 01         | 11  | 10  | 00  | 01         | 11  | 10 | _ |

|----|------------|-----|-----|-----|------|------|------|----|------------|-----|-----|-----|------------|-----|----|---|

|    |            |     | C = | = 0 |      |      |      |    |            |     | C = | = 1 |            |     |    |   |

|    | <b>T</b> : | = 0 |     |     | T =  | = 1  |      |    | <b>T</b> : | = 0 |     |     | <b>T</b> : | = 1 |    | Q |

| 2  | 4          | 6   | 8   | 10  | (12) | (14) | (16) | 18 | 20         | 19  | 21  | 22  | 23         | 25  | 24 | 0 |

| 3  | 5          | 7   | 9   | 11  | 13   | 15   | 17   | 18 | 20         | 19  | 21  | 22  | 23         | 25  | 24 | 1 |

Figure 3.4-1 Graphs of State Triples for Two-State MD-Latch.

| D       | 1  | 1  | 1 | 0 | 0  | 0 | 1 | 1 | 1  | 1 | 0 | 0  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  |

|---------|----|----|---|---|----|---|---|---|----|---|---|----|---|----|----|----|----|----|----|----|----|----|----|----|----|----|

| S       | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 1 | 1  | 1 | 1 | 1  | 1 | 1  | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 0  | 0  |

| Т       | 1  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  | 0 | 0 | 0  | 0 | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| С       | 1  | 1  | 0 | 0 | 1  | 0 | 0 | 0 | 1  | 0 | 0 | 1  | 0 | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  |

| Q       | 0  | 1  | 1 | 1 | 0  | 0 | 0 | 0 | 1  | 1 | 1 | 0  | 0 | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  |

| State   | 24 | 21 | 9 | 3 | 18 | 2 | 8 | 6 | 19 | 7 | 5 | 20 | 4 | 12 | 23 | 13 | 11 | 22 | 10 | 12 | 14 | 25 | 15 | 17 | 24 | 16 |

| Triples |    | F  |   |   | А  |   |   |   | E  |   |   | В  |   |    | G  |    |    | С  |    |    |    | Н  |    |    | D  |    |

Table 3.4-2 A Minimum-Length (26) Checking Experiment for MD-Latch.

#### 3.5 Two-State Two-Port Latch

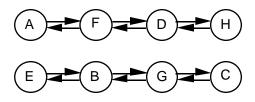

The equation for a Two-Port latch is  $Q = C_1D_1 + C_2D_2 + \overline{C_1C_2q}$ . C1 and C2 should not be both active at the same time. The Two-Port latch loads the data input corresponding to the active control input. The flow table is shown in Table 3.5-1.

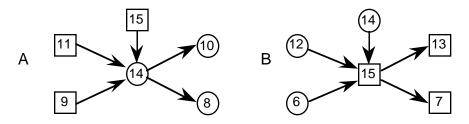

The last four columns are marked as don't cares because the operation of the latch is not defined when both control lines are active. Graphs of the triples are shown in Fig. 3.5-1. Since

## Table 3.5-1 Flow Table for Two-State Two-Port Latch.

$D_1D_2$

states 2 and 7 appear twice as distinguishing states of triples, and there are 16 total states, the lower bound on the test length is 19. Appendix B shows that the length must be at least 23. The details of combining the triples to derive minimum-length sequences also appear in Appendix B. One such sequence is shown in Table 3.5-2.

Figure 3.5-1 Graphs of State Triples for Two-State Two-Port Latch.

| Table 3.5-2 A Minimum | Length (23) ( | Checking Exp | eriment for 7 | <b>Fwo-Port Latch.</b> |

|-----------------------|---------------|--------------|---------------|------------------------|

|-----------------------|---------------|--------------|---------------|------------------------|

| D1              | 1  | 0  | 0 | 0 | 0  | 0 | 0 | 0  | 0 | 1 | 1  | 1 | 1  | 1 | 1 | 1  | 1 | 0 | 0  | 0 | 1 | 1  | 1 |

|-----------------|----|----|---|---|----|---|---|----|---|---|----|---|----|---|---|----|---|---|----|---|---|----|---|

| C <sub>1</sub>  | 1  | 1  | 0 | 0 | 0  | 0 | 0 | 0  | 0 | 0 | 1  | 0 | 0  | 0 | 0 | 0  | 0 | 0 | 1  | 0 | 0 | 1  | 0 |

| $D_2$           | 0  | 0  | 0 | 1 | 1  | 1 | 0 | 0  | 0 | 0 | 0  | 0 | 0  | 0 | 1 | 1  | 1 | 1 | 1  | 1 | 1 | 1  | 1 |

| $C\overline{2}$ | 0  | 0  | 0 | 0 | 1  | 0 | 0 | 1  | 0 | 0 | 0  | 0 | 1  | 0 | 0 | 1  | 0 | 0 | 0  | 0 | 0 | 0  | 0 |

| Q               | 1  | 0  | 0 | 0 | 1  | 1 | 1 | 0  | 0 | 0 | 1  | 1 | 0  | 0 | 0 | 1  | 1 | 1 | 0  | 0 | 0 | 1  | 1 |

| State           | 13 | 10 | 2 | 4 | 15 | 5 | 3 | 14 | 2 | 8 | 13 | 9 | 16 | 8 | 6 | 17 | 7 | 5 | 12 | 4 | 6 | 11 | 7 |

| Triples         |    | А  |   |   | F  |   |   | Ε  |   |   | D  |   |    |   |   |    |   |   |    |   |   |    |   |

|                 |    |    |   |   |    |   |   |    |   |   |    |   | Η  |   |   | G  |   |   | В  |   |   | С  |   |

#### 3.6 Two-State Load Enable Latch

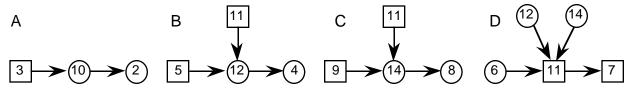

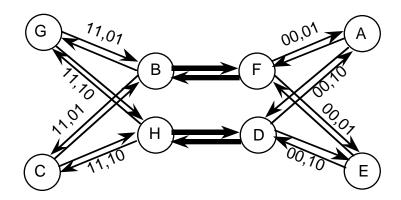

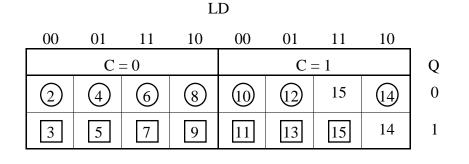

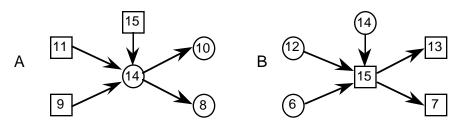

The equation for the Load Enable latch is Q = CLD + (LC)q. When L = 0, the clock has no effect on the latch, and the latch retains the stored value. When L = 1, it behaves like a D-latch. The flow table for the Load Enable latch is given in Table 3.6-1. Graphs of the triples are shown in Fig. 3.6-1. Since there are 14 stable total states, a checking experiment must have at least 15 patterns. One such sequence is shown in Table 3.6-2. The details are in Appendix C.

#### Table 3.6-1 Flow Table for Two-State Load Enable Latch.

LD 00 01 10 00 01 10 11 11 C = 0C = 1Q (14) 0 (8) (10)(12) 15 (2)(4)(6) 5 7 13 15 14 1 3 9 11

Figure 3.6-1 Graphs of State Triples of Two-State Load Enable Latch.

#### Table 3.6-2 A Minimum-Length (15) Checking Experiment for Load Enable Latch.

| L       | 1  | 1  | 0  | 0 | 1 | 1 | 0 | 0  | 1  | 0  | 0 | 1 | 1 | 0 | 0  |

|---------|----|----|----|---|---|---|---|----|----|----|---|---|---|---|----|

| D       | 1  | 0  | 0  | 0 | 0 | 1 | 1 | 1  | 1  | 1  | 1 | 1 | 0 | 0 | 0  |

| С       | 1  | 1  | 1  | 0 | 0 | 0 | 0 | 1  | 1  | 1  | 0 | 0 | 0 | 0 | 1  |

| Q       | 1  | 0  | 0  | 0 | 0 | 0 | 0 | 0  | 1  | 1  | 1 | 1 | 1 | 1 | 1  |

| State   | 15 | 14 | 10 | 2 | 8 | 6 | 4 | 12 | 15 | 13 | 5 | 7 | 9 | 3 | 11 |

| Triples |    | A  |    |   |   |   |   |    | В  |    |   |   |   |   |    |

#### 3.7 Two-State D-Enable Latch

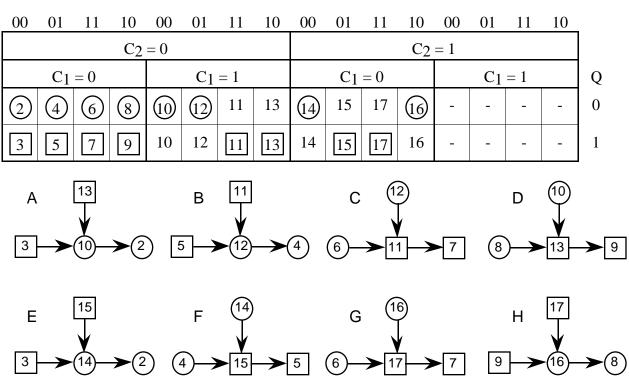

The equation for the D-Enable latch is  $Q = CDE + \overline{C}q$ . A D-Enable latch operates as a D-latch when E = 1. When E = 0, the D-Enable latch will load 0. The flow table for the D-Enable latch is shown in Table 3.7-1. The graphs of the state triples are shown in Fig 3.7-1.

#### Table 3.7-1 Flow Table for Two-State D-Enable Latch.

|        |     |     | _  | _  |      |     |      |   |

|--------|-----|-----|----|----|------|-----|------|---|

| <br>00 | 01  | 11  | 10 | 00 | 01   | 11  | 10   |   |

|        | C = | = 0 |    |    | C :  | = 1 |      | Q |

| 2      | 4   | 6   | 8  | 10 | (12) | 11  | (14) | 0 |

| 3      | 5   | 7   | 9  | 10 | 12   | 11  | 14   | 1 |

DE

Looking at the flow table, all the distinguishing states occur when C = 0, and all the unstable states occur when C = 1. Therefore, the D-Enable latch is a single-input control state machine, and C is the control input. There are 12 total states, one unstable state in the first row, and three in the second. Therefore, the length of a checking experiment must be at least 15. Appendix D shows that the length must be at least 16. One possible minimum-length sequence is shown in Table 3.7-2. Details of deriving a checking experiment are given in Appendix D.

Figure 3.7-1 Graphs of State Triples for Two-State D-Enable Latch.

| D       | 1  | 0  | 0 | 1 | 1  | 1  | 1 | 1 | 1  | 1 | 1 | 0 | 0 | 0 | 0  | 0 |

|---------|----|----|---|---|----|----|---|---|----|---|---|---|---|---|----|---|

| E       | 1  | 1  | 1 | 1 | 1  | 0  | 0 | 1 | 1  | 1 | 0 | 0 | 1 | 0 | 0  | 0 |

| С       | 1  | 1  | 0 | 0 | 1  | 1  | 0 | 0 | 1  | 0 | 0 | 0 | 0 | 0 | 1  | 0 |

| Q       | 1  | 0  | 0 | 0 | 1  | 0  | 0 | 0 | 1  | 1 | 1 | 1 | 1 | 1 | 0  | 0 |

| State   | 11 | 12 | 4 | 6 | 11 | 14 | 8 | 6 | 11 | 7 | 9 | 3 | 5 | 3 | 10 | 2 |

| Triples |    | В  |   |   |    | С  |   |   | D  |   |   |   |   |   | A  |   |

Table 3.7-2 A Minimum-Length (16) Checking Experiment for Two-State D-Enable Latch.

#### 3.8 Two-State XOR Input Latch

The equation for the XOR input latch is  $Q = C(D \oplus S) + \overline{C}q$ . The data loaded into the latch is  $D \oplus S$ . The flow table is given in Table 3.8-1. Since there are 12 stable states in the flow table, a checking experiment must have at least 13 patterns. Graphs of the state triples are shown in Fig. 3.8-1.

Table 3.8-1 Flow Table for Two-State XOR Latch.

Figure 3.8-1 Graphs of State Triples for Two-State XOR latch.

Starting with any triple, there are two possible sequences. For example, starting with A, the two sequences are ACBD and ADBC. Since there are four triples, and any of them can be picked as the starting point, there are 8 sequences. Note that a sequence that connects the triples not only demonstrates all the unstable states, but also visits all the stable states. The transition from one triple to the other forms a link among all distinguishing inputs. The sequences formed by connecting the triples are all minimum-length checking experiments. One of the minimum-length checking experiments is given in Table 3.8-2.

| D       | 0  | 0  | 0 | 0 | 0  | 0 | 1 | 1  | 1 | 1 | 1  | 1 | 0 |

|---------|----|----|---|---|----|---|---|----|---|---|----|---|---|

| S       | 1  | 0  | 0 | 1 | 1  | 1 | 1 | 1  | 1 | 0 | 0  | 0 | 0 |

| С       | 1  | 1  | 0 | 0 | 1  | 0 | 0 | 1  | 0 | 0 | 1  | 0 | 0 |

| Q       | 1  | 0  | 0 | 0 | 1  | 1 | 1 | 0  | 0 | 0 | 1  | 1 | 1 |

| States  | 11 | 10 | 2 | 4 | 11 | 5 | 7 | 12 | 6 | 8 | 13 | 9 | 3 |

| Triples |    | А  |   |   | С  |   |   | В  |   |   | D  |   |   |

Table 3.8-2 A Minimum-Length (13) Checking Experiment for XOR Input Latch.

#### 3.9 Two-State BILBO Latch

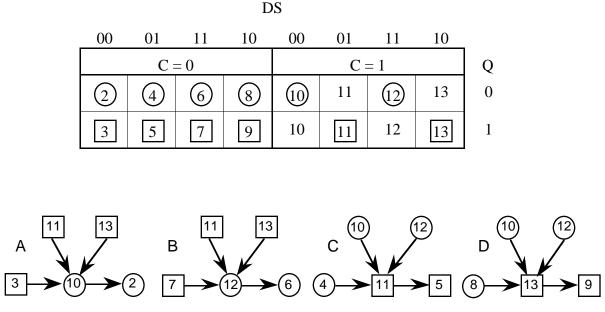

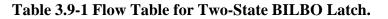

The equation for a BILBO latch is  $Q = C(B_1D \oplus \overline{B_2S}) + \overline{Cq}$ . Based on the setting of B<sub>1</sub> and B<sub>2</sub>, the latch can be configured to load D (when B<sub>1</sub>B<sub>2</sub> = 11), reset the latch (when B<sub>1</sub>B<sub>2</sub> = 01), load S (when B<sub>1</sub>B<sub>2</sub> = 00), and load S  $\oplus$  D (when B<sub>1</sub>B<sub>2</sub> = 10). The flow table for the BILBO latch is given in Table 3.9-1.

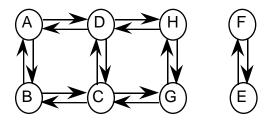

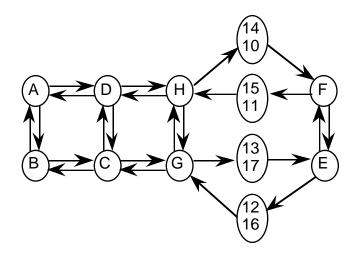

Looking at the flow table, all the distinguishing states occur when C = 0, and all the unstable states occur when C = 1. Therefore, the BILBO latch is a single-input control state machine, and C is the control input. There are 48 total states, and four more unstable states in the second row than in the first. Therefore, the length of a checking experiment must be at least 55. Appendix E shows that the length must be at least 58. One possible minimum-length sequence is shown in Table 3.9-2. Details of deriving a checking experiment are given in Appendix E.

Figure 3.9-1 Graphs of State Triples for Two-State BILBO Latch.

Table 3.9-2 A Minimum-Length (58) Checking Experiments for Two-State BILBO Latch.

| D                                                      | 0           | 0                     | 0                | 0                          | 0                                         | 0                          | 0                           | 0                                                                                     | 0                | 0                     | 1                                | 1                                                                                                                   | 1                            | 1                     | 1                           | 1                                                                                                                                     | 1                           | 0                           | 0                                                                                     | 0                                | 0                           | 0                                                                          | 0                           | 0                                | 0                                                                                                                                                             | 0                     | 1                     | 1 1                                                                                   |

|--------------------------------------------------------|-------------|-----------------------|------------------|----------------------------|-------------------------------------------|----------------------------|-----------------------------|---------------------------------------------------------------------------------------|------------------|-----------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|---------------------------------------------------------------------------------------|----------------------------------|-----------------------------|----------------------------------------------------------------------------|-----------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|---------------------------------------------------------------------------------------|

| S                                                      | 0           | 0                     | 0                | 0                          | 0                                         | 0                          | 1                           | 1                                                                                     | 1                | 0                     | 0                                | 0                                                                                                                   | 0                            | 0                     | 0                           | 0                                                                                                                                     | 0                           | 0                           | 0                                                                                     | 0                                | 0                           | 0                                                                          | 0                           | 1                                | 1                                                                                                                                                             | 1                     | 1                     | 1 1                                                                                   |

| B2                                                     | 0           | 0                     | 0                | 0                          | 0                                         | 0                          | 0                           | 0                                                                                     | 0                | 0                     | 0                                | 0                                                                                                                   | 0                            | 0                     | 1                           | 1                                                                                                                                     | 1                           | 1                           | 1                                                                                     | 1                                | 1                           | 1                                                                          | 1                           | 1                                | 1                                                                                                                                                             | 1                     | 1                     | 1 1                                                                                   |

| $B_1$                                                  | 0           | 1                     | 1                | 0                          | 0                                         | 0                          | 0                           | 0                                                                                     | 0                | 0                     | 0                                | 1                                                                                                                   | 1                            | 1                     | 1                           | 1                                                                                                                                     | 1                           | 1                           | 1                                                                                     | 1                                | 0                           | 0                                                                          | 0                           | 0                                | 0                                                                                                                                                             | 0                     | 0                     | 0 0                                                                                   |

| Ċ                                                      | 1           | 1                     | 0                | 0                          | 1                                         | 0                          | 0                           | 1                                                                                     | 0                | 0                     | 0                                | 0                                                                                                                   | 1                            | 0                     | 0                           | 1                                                                                                                                     | 0                           | 0                           | 1                                                                                     | 0                                | 0                           | 1                                                                          | 0                           | 0                                | 1                                                                                                                                                             | 0                     | 0                     | 1 0                                                                                   |

| 0                                                      | 1           | 0                     | 0                | 0                          | 1                                         | 1                          | 1                           | 0                                                                                     | 0                | 0                     | 0                                | 1                                                                                                                   | 0                            | 0                     | 0                           | 1                                                                                                                                     | 1                           | 1                           | 0                                                                                     | 0                                | 0                           | 1                                                                          | 1                           | 1                                | 0                                                                                                                                                             | 0                     | 0                     | 1 1                                                                                   |

| State                                                  | 35          | 38                    | 10               | 2                          | 35                                        | 3                          | 5                           | 34                                                                                    | 4                | 2                     | 35                               | 17                                                                                                                  | 44                           | 16                    | 32                          | 45                                                                                                                                    | 33                          | 27                          | 50                                                                                    | 26                               | 18                          | 39                                                                         | 19                          | 21                               | 46                                                                                                                                                            | 20                    | 22                    | 41 23                                                                                 |

| Triples                                                |             | Е                     |                  |                            | ۸                                         |                            |                             | В                                                                                     |                  |                       |                                  |                                                                                                                     | Н                            |                       |                             | R                                                                                                                                     |                             |                             | Ν                                                                                     |                                  |                             | T                                                                          |                             |                                  | V                                                                                                                                                             |                       |                       | T                                                                                     |

| 111pics                                                |             | E                     |                  |                            | A                                         |                            |                             | D                                                                                     |                  |                       |                                  |                                                                                                                     | Π                            |                       |                             | Γ                                                                                                                                     |                             |                             | IN                                                                                    |                                  |                             | J                                                                          |                             |                                  | Ν                                                                                                                                                             |                       |                       | L                                                                                     |

| D                                                      | 1           | <u>Е</u>              | 1                | 1                          | A<br>1                                    | 1                          | 1                           | D                                                                                     | 1                | 1                     | 1                                | 1                                                                                                                   | <u>п</u>                     | 1                     | 1                           | 1                                                                                                                                     | 1                           | 0                           | $\frac{1}{0}$                                                                         | 0                                | 1                           | 1                                                                          | 1                           | 1                                | 1                                                                                                                                                             | 0                     | 0                     | $\begin{array}{c c} \mathbf{L} \\ 0 & 0 \end{array}$                                  |

|                                                        | 1<br>1      | L<br>1<br>1           | 1<br>1           | 1<br>0                     | A<br>1<br>0                               | 1<br>0                     | 1<br>0                      | 1<br>0                                                                                | 1<br>0           | 1<br>0                | 1                                | 1<br>1                                                                                                              | п<br>1<br>1                  | 1<br>1                | 1<br>1                      | 1<br>1                                                                                                                                | 1<br>1                      | 0                           | 0<br>1                                                                                | 0                                | 1<br>1                      | 1<br>1                                                                     | 1<br>1                      | 1                                | <u>к</u><br>1<br>0                                                                                                                                            | 0<br>0                | 0<br>1                | L<br>0 0<br>1 1                                                                       |

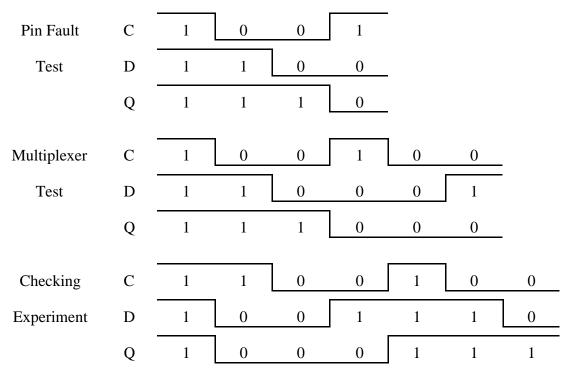

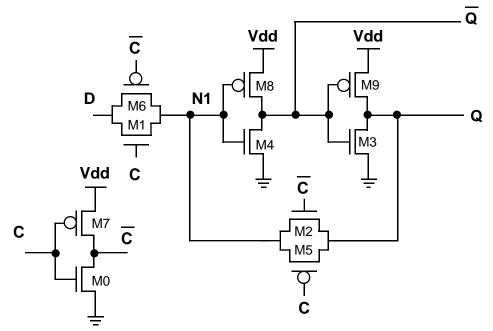

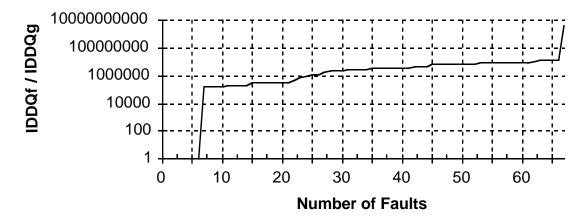

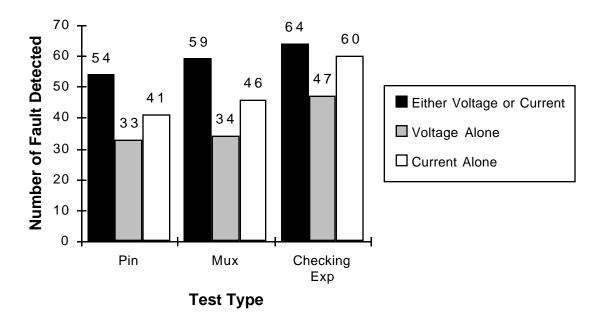

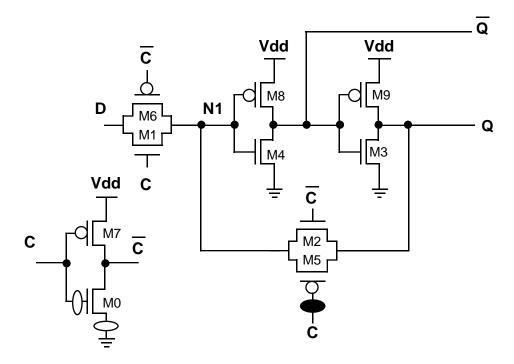

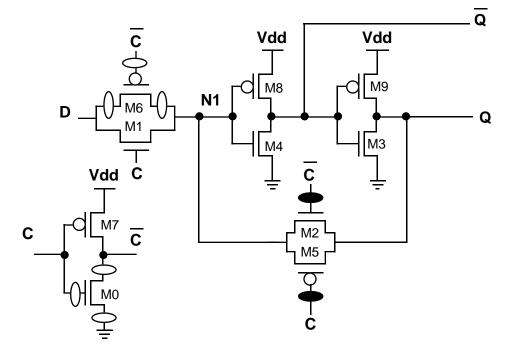

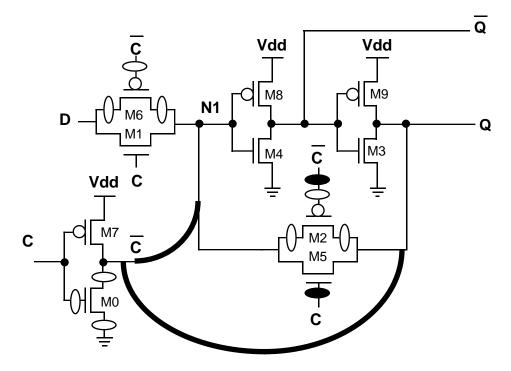

| D                                                      | 1<br>1<br>0 | 1<br>1<br>0           | 1<br>1<br>0      | 1<br>0<br>0                | A<br>1<br>0<br>0                          | 1<br>0<br>0                | 1<br>0<br>1                 | 1<br>0<br>1                                                                           | 1<br>0<br>1      | 1<br>0<br>1           | 1<br>0<br>1                      | 1<br>1<br>1                                                                                                         | 1<br>1<br>0                  | 1<br>1<br>0           | 1<br>1<br>1                 | 1<br>1<br>1                                                                                                                           | 1<br>1<br>1                 | 0<br>1<br>1                 | 0<br>1<br>1                                                                           | 0<br>1<br>1                      | 1<br>1<br>1                 | 1<br>1<br>1                                                                | 1<br>1<br>1                 | 1<br>1<br>0                      | 1<br>0<br>0                                                                                                                                                   | 0<br>0<br>0           | 0<br>1<br>0           | L       0     0       1     1       0     0                                           |