### ARCHITECTURAL AND IMPLEMENTATION TRADEOFFS FOR MULTIPLE-CONTEXT PROCESSORS

A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> By James P. Laudon September 1994

### ARCHITECTURAL AND IMPLEMENTATION TRADEOFFS FOR MULTIPLE-CONTEXT PROCESSORS

### James P. Laudon

**Technical Report: CSL-TR-94-634**

September 1994

Computer Systems Laboratory Departments of Electrical Engineering and Computer Science Stanford University Stanford California, 94305-4055

### Abstract

Tolerating memory latency is essential to achieving high performance in scalable sharedmemory multiprocessors. In addition, tolerating instruction (pipeline dependency) latency is essential to maximize the performance of individual processors. Multiple-context processors have been proposed as a universal mechanism to mitigate the negative effects of latency. These processors tolerate latency by switching to a concurrent thread of execution whenever one of the threads blocks due to a high-latency operation. Multiple context processors built so far, however, either have a high context-switch cost which disallows tolerance of short latencies (e.g., due to pipeline dependencies), or alternatively they require excessive concurrency from the software.

We propose a multiple-context architecture that combines full single-thread support with cycle-by-cycle context interleaving to provide lower switch costs and the ability to tolerate short latencies. We compare the performance of our proposal with that of earlier approaches, showing that our approach offers substantially better performance for parallel applications. We also explore using our approach for uniprocessor workstations — an important environment for commodity microprocessors. We show that our approach also offers much better performance for multiprogrammed uniprocessor workloads.

Finally, we explore the implementation issues for both our proposed and existing multiplecontext architectures. One of the larger costs for a multiple-context processor arises in providing a cache capable of handling multiple outstanding requests, and we propose a lockup-free cache which provides high performance at a reasonable cost. We also show that amount of processor state that needs to be replicated to support multiple contexts is modest and the extra complexity required to control the multiple contexts under both our proposed and existing approaches is manageable. The performance benefits and reasonable implementation cost of our approach make it a promising candidate for addition to future microprocessors. Key Words and Phrases: multithreading, multiple-context processors, tolerating latency, lockupfree caches, microprocessor implementation, shared-memory multiprocessors. © Copyright 1994 by James P. Laudon All Rights Reserved

## Acknowledgments

This work has greatly benefited from all the people I had the pleasure of working with at Stanford. First, my sincerest thanks go to my advisor, Anoop Gupta. Anoop was the fearless leader of the DASH project and once we had finished building the DASH prototype, helped to steer me towards an indepth study of multiple-context processors. Anoop was also never short of good advice along the course of my explorations and impressed upon me the need to study a topic in enough detail to insure you understand all its subtleties. I would also like to thank my co-advisor, Mark Horowitz. Mark provided invaluable advice on processor implementation issues and had a knack for asking the hard questions that led to new insights. I also thank John Hennessy for his advice and support and Giovanni De Micheli for serving as my orals committee chairman.

I also thank the friends and colleagues that made my time at Stanford both enjoyable and enlightening. In particular, I would like to thank the other members of the DASH team: Dan Lenoski, Luis Stevens, Dave Nakahira, Truman Joe, Wolf Weber, and Kourosh Gharachorloo, for making the building of DASH such an exciting and learning experience. I thank Mike Smith for providing the twine scheduler and masm assembler and for being so willing to fix the problems I uncovered. Steve Goldschmidt and Helen Davis provided Tango-Lite, a tool integral to my simulation studies. Grant McFarland was kind enough to design the multiple-context register file as a class project. Thanks also to Margaret Rowland and Darlene Hadding for making the job of jumping the administrative hoops so easy and to Charles Orgish and Laura Schrager for keeping the machines running smoothly. Finally, I would like to thank the trailer crew: J. P. Singh, Todd Mowry, and Andrew Erlichson, for their friendship, interesting (and sometimes seemingly unending) conversations, and general high jinks.

I thank Jim Smith for giving me that initial push that started me on the road to my Ph.D. I also thank my parents for all the love, support, and encouragement they've given me over the years. Most importantly, I thank my wife, Karen, who helped me explore the bay area and allowed me to keep things in perspective when the hours at Stanford got too long.

This work was supported by DARPA under contract N00039-91-C-0138. I also gratefully acknowledge support by IBM through the CIS Fellow-Mentor-Advisor program.

# Contents

### Acknowledgments

| 1 | Intro | oduction                                      | 1  |

|---|-------|-----------------------------------------------|----|

|   | 1.1   | The Latency Problem                           | 3  |

|   | 1.2   | The Multiple-Context Solution                 | 4  |

|   | 1.3   | This Thesis                                   | 5  |

|   | 1.4   | Contributions                                 | 7  |

| 2 | A N   | ew Multiple-Context Processor                 | 8  |

|   | 2.1   | Fine-grained Multiple-Context Processors      | 8  |

|   | 2.2   | Blocked Multiple-Context Processors           | 0  |

|   | 2.3   | Interleaved Proposal                          | 2  |

|   |       | 2.3.1 Performance Advantages                  | 2  |

|   |       | 2.3.2 Implementation Requirements             | 6  |

|   | 2.4   | Related Work                                  | 8  |

|   | 2.5   | Summary                                       | 9  |

| 3 | Mult  | tiple Contexts: Utility for Multiprocessors 2 | 20 |

|   | 3.1   | Evaluation Methodology                        | 1  |

|   |       | 3.1.1 Base Architecture                       | 1  |

|   |       | 3.1.2 Simulation Environment                  | 4  |

|   |       | 3.1.3 Applications Suite                      | 7  |

|   |       | 3.1.4 Simulation Configurations               | 9  |

|   | 3.2   | Effectiveness of Multiple-Contexts            | 0  |

|   |       | 3.2.1 Application Classification              | 1  |

iv

|   |      | 3.2.2    | Comparison of Interleaved and Blocked Schemes | 34       |

|---|------|----------|-----------------------------------------------|----------|

|   |      | 3.2.3    | Summary                                       | 39       |

|   | 3.3  | Variati  | ional Analyses                                | 40       |

|   |      | 3.3.1    | Synchronization Latency Tolerance Mechanisms  | 40       |

|   |      | 3.3.2    | Instruction Latency Tolerance Mechanisms      | 41       |

|   |      | 3.3.3    | Effects of Memory Latency                     | 42       |

|   |      | 3.3.4    | Effects of Differing Cache Organizations      | 43       |

|   | 3.4  | Combi    | ining with Other Latency Tolerance Mechanisms | 43       |

|   |      | 3.4.1    | Multiple Contexts and Release Consistency     | 44       |

|   |      | 3.4.2    | Multiple Contexts and Nonblocking Loads       | 45       |

|   | 3.5  | Shared   | l Resource Impact                             | 48       |

|   |      | 3.5.1    | Branch Prediction                             | 48       |

|   |      | 3.5.2    | Translation Look-aside Buffer                 | 49       |

|   |      | 3.5.3    | Data Cache                                    | 50       |

|   | 3.6  | Summ     | ary                                           | 54       |

| 4 | Mul  | tiple C  | ontexts: Utility for Uniprocessors            | 55       |

| 4 | 4.1  | -        | dology                                        | 56       |

|   | 4.1  |          | iveness of Multiple Contexts                  | 50<br>60 |

|   | 4.2  |          | 1 Resource Impact                             | 64       |

|   | 4.3  | 4.3.1    | Branch Prediction                             | 64       |

|   |      | 4.3.1    | Translation Look-aside Buffers                | 65       |

|   |      | 4.3.2    |                                               |          |

|   | 4.4  |          | Caches                                        | 67<br>68 |

|   | 4.4  | Summ     | ary                                           | 08       |

| 5 | Locl | cup-free | e Cache Design                                | 74       |

|   | 5.1  | Previo   | us Work                                       | 75       |

|   |      | 5.1.1    | Transaction Buffer Request Tracking           | 75       |

|   |      | 5.1.2    | In-cache Request Tracking                     | 78       |

|   |      | 5.1.3    | Discussion                                    | 79       |

|   | 5.2  | Locku    | p-free Cache Design                           | 79       |

|   |      | 5.2.1    | Lockup-free Requirements                      | 83       |

|   |      | 5.2.2    | Lockup-free Cache Proposal                    | 88       |

|   |      | 5.2.3    | Buffer Deadlock                               | 90       |

|   |      |          |                                               |          |

| A | Deta | ils of t       | he Tango-Lite Based Simulator    | 138        |

|---|------|----------------|----------------------------------|------------|

| 8 | Con  | clusions       | 3                                | 135        |

|   | 7.5  | Summ           | ary                              | 133        |

|   | 7.4  |                | Replication                      | 132        |

|   |      | 7.3.2          | Context Interleaving             | 132        |

|   |      | 7.3.1          | Next Context Selection           | 131        |

|   | 7.3  | Contex         | tt Control                       | 131        |

|   | 7.2  | Contex         | tt Availability Control          | 128        |

|   |      | 7.1.3          | Context Availability Change      | 128        |

|   |      | 7.1.2          | Exception and Interrupt Handling | 127        |

|   |      | 7.1.1          | PC Unit                          | 124        |

|   | 7.1  | Instruc        | tion Issue                       | 124        |

| 7 | Inte | rleaved        | Scheme Implementation            | 123        |

|   | 6.3  | Summ           | ary                              | 121        |

|   |      | 6.2.3          | Context Switch Mechanics         | 117        |

|   |      | 6.2.2          | Next Context Selection           | 117        |

|   |      | 6.2.1          | Context Switch Detection         | 116        |

|   | 6.2  |                | t Schedule and Control           | 115        |

|   |      | 6.1.4          | Summary                          | 115        |

|   |      | 6.1.3          | Processor Status Word            | 114        |

|   |      | 6.1.2          | Register File                    | 112        |

|   |      | 6.1.1          | Program Counter                  | 108        |

|   | 6.1  | State F        | Replication                      | 108        |

| 6 | Bloc | ked Sc         | heme Implementation              | 108        |

|   | 5.4  | Summ           | ary                              | 100        |

|   | 5.4  |                | ary                              | 105        |

|   |      | 5.3.2          | Adaptive Stalling Performance    | 103        |

|   |      | 5.3.1<br>5.3.2 | Multiple Outstanding Writes      | 100<br>103 |

|   | 5.3  |                | mance Issues                     | 100        |

|   |      | 5.2.4          | Multiple-Context Deadlock        | 91         |

|   |      |                |                                  |            |

| B          | SPL                   | ASH Application Descriptions                        | 142 |  |  |

|------------|-----------------------|-----------------------------------------------------|-----|--|--|

|            | <b>B</b> .1           | Barnes-Hut                                          | 142 |  |  |

|            | B.2                   | Cholesky                                            | 143 |  |  |

|            | B.3                   | LocusRoute                                          | 143 |  |  |

|            | B.4                   | MP3D                                                | 144 |  |  |

|            | B.5                   | Ocean                                               | 144 |  |  |

|            | B.6                   | PTHOR                                               | 145 |  |  |

|            | B.7                   | Water                                               | 145 |  |  |

| С          | Coh                   | erent Cache Design                                  | 147 |  |  |

|            | C.1                   | Coherence Between Processing Nodes                  | 147 |  |  |

|            | C.2                   | Coherence Within the Cache Hierarchy                | 148 |  |  |

|            |                       | C.2.1 Maintaining Coherence for Each Cache Line     | 150 |  |  |

|            |                       | C.2.2 Handling Coherence Races Within the Hierarchy | 152 |  |  |

|            | C.3                   | Summary                                             | 157 |  |  |

| D          | Buff                  | er Deadlock in Multilevel Cache Hierarchies         | 158 |  |  |

|            | D.1                   | Deadlock Prevention                                 | 160 |  |  |

|            | D.2                   | Deadlock Avoidance                                  | 162 |  |  |

|            | D.3                   | Deadlock Detection and Removal                      | 163 |  |  |

|            | D.4                   | Summary                                             | 163 |  |  |

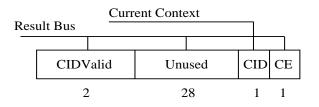

| E          | Processor Status Word |                                                     |     |  |  |

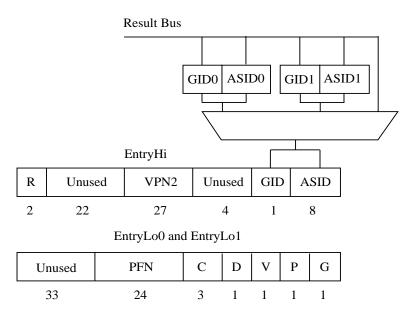

|            | E.1                   | EntryHi and EntryLo                                 | 165 |  |  |

|            | E.2                   | Status                                              | 169 |  |  |

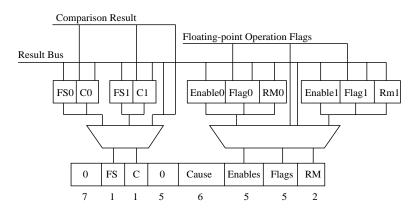

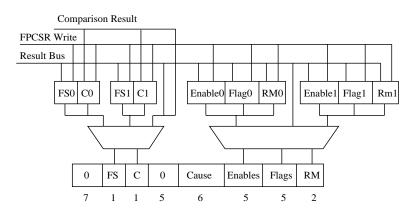

|            | E.3                   | Floating-point Control/Status                       | 170 |  |  |

|            | E.4                   | LL Bit and LL Addr                                  | 172 |  |  |

|            | E.5                   | DEC 21064 PSW                                       | 173 |  |  |

|            | E.6                   | Summary                                             | 174 |  |  |

| <b>D</b> ! | hliam                 | raphy                                               | 175 |  |  |

# List of Tables

| 3.1  | Branch target buffer parameters.                                                      | 23 |

|------|---------------------------------------------------------------------------------------|----|

| 3.2  | Long-latency operations.                                                              | 24 |

| 3.3  | Context switch costs.                                                                 | 25 |

| 3.4  | Base TLB parameters.                                                                  | 26 |

| 3.5  | Base data cache parameters.                                                           | 26 |

| 3.6  | Default memory latencies.                                                             | 27 |

| 3.7  | SPLASH suite summary.                                                                 | 27 |

| 3.8  | Application data sets.                                                                | 28 |

| 3.9  | Application characteristics important for determining multiple-context effectiveness. | 33 |

| 3.10 | Total number of reads per application (in millions).                                  | 36 |

| 3.11 | Summary of application speedups due to multiple contexts                              | 39 |

| 3.12 | Performance of different synchronization tolerance policies for the interleaved       |    |

|      | multiple context processor.                                                           | 40 |

| 3.13 | Backoff values (in processor cycles) employed for the tuned switch spinning policy.   | 41 |

| 3.14 | Speedup due to tolerating longer instruction latency.                                 | 42 |

| 3.15 | Effects of memory latency.                                                            | 42 |

| 3.16 | Multiple-context speedup for differing cache sizes (all caches direct-mapped).        | 43 |

| 3.17 | Multiple-context speedup for differing cache associativities (all caches 64 KB)       | 44 |

| 3.18 | Speedup due to release consistency for the single-context processor                   | 45 |

| 3.19 | Combining release consistency with multiple contexts                                  | 45 |

| 3.20 | Speedup of switch-on-use over switch-on-load                                          | 48 |

| 3.21 | Effect of multiple contexts on the BTB.                                               | 49 |

| 3.22 | Effect of multiple contexts on the data TLB miss rate (%).                            | 50 |

| 4.1  | Uniprocessor memory latencies.                                                        | 57 |

| 4.2  | Operating system costs.                                                           | 58  |

|------|-----------------------------------------------------------------------------------|-----|

| 4.3  | Uniprocessor workloads                                                            | 59  |

| 4.4  | Characteristics of measured portion of uniprocessor applications                  | 59  |

| 4.5  | Increase in application throughput with multiple contexts                         | 64  |

| 4.6  | Effect of multiple contexts on the BTB.                                           | 66  |

| 4.7  | Effect of multiple contexts on the data TLB.                                      | 67  |

| 5.1  | MSHR state entries.                                                               | 75  |

| 5.2  | Cache states used to support the intra-hierarchy coherence protocol               | 81  |

| 5.3  | Coherence messages.                                                               | 81  |

| 5.4  | General cache coherence protocol.                                                 | 82  |

| 5.5  | Lockup-free cache coherence protocol (uppermost writeback cache).                 | 89  |

| 5.6  | Speedup due to supporting multiple outstanding writes for the single-context pro- |     |

|      | cessor                                                                            | 101 |

| 5.7  | Speedup due to supporting multiple outstanding writes for the multiple-context    |     |

|      | processor.                                                                        | 101 |

| 5.8  | Percent of total time stalled due to adaptive stalling                            | 103 |

| 5.9  | Percent of total time stalled due to cache contention                             | 105 |

| 5.10 | Speedup due to wide-ending.                                                       | 105 |

| 6.1  | Timing information for the replicated register file.                              | 113 |

| 6.2  | Statistics for the replicated and apportioned four-context register file          | 114 |

| 8.1  | Summary of speedups with eight contexts per processor for the SPLASH appli-       |     |

|      | cations                                                                           | 136 |

| 8.2  | Summary of throughput increase with four contexts per processor                   | 136 |

| C.1  | Cache states used to support the intra-hierarchy coherence protocol               | 151 |

| C.2  | Coherence messages.                                                               | 152 |

| C.3  | Cache coherence protocol key.                                                     | 153 |

| C.4  | Cache coherence protocol — uppermost writeback cache                              | 154 |

| C.5  | Cache coherence protocol — writeback caches except uppermost                      | 155 |

| C.6  | Cache coherence protocol — writethrough caches                                    | 156 |

| E.1  | MIPS R4000 processor status word registers.                                       | 166 |

| E.2 | MIPS R4000 process-specific portion of the processor status word | 166 |

|-----|------------------------------------------------------------------|-----|

| E.3 | Modes for each TLB entry.                                        | 168 |

# **List of Figures**

| 1.1  | General structure of a scalable multiprocessor.                                 | 1  |

|------|---------------------------------------------------------------------------------|----|

| 2.1  | Example illustrating the lower context switch cost of interleaved scheme        | 13 |

| 2.2  | Example illustrating instruction latency tolerance by the interleaved scheme    | 14 |

| 2.3  | Comparison of the blocked and interleaved multiple-context schemes for a set of |    |

|      | four threads.                                                                   | 15 |

| 3.1  | Base multiprocessor architecture.                                               | 22 |

| 3.2  | Processor pipeline.                                                             | 23 |

| 3.3  | SPLASH application speedups with a perfect memory system                        | 30 |

| 3.4  | Speedups with four or eight contexts per processor for both the blocked and     |    |

|      | interleaved schemes                                                             | 31 |

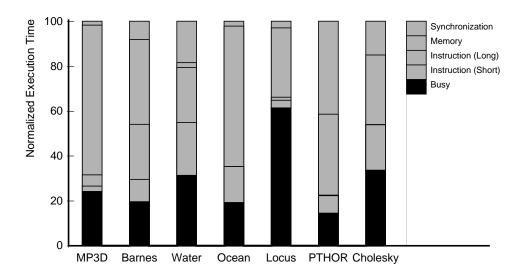

| 3.5  | Breakdown of SPLASH execution time for the single-context processor             | 32 |

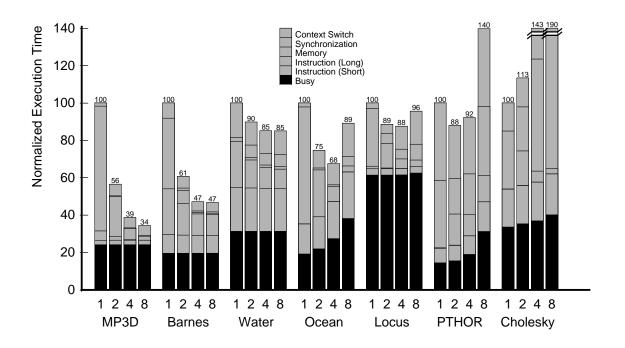

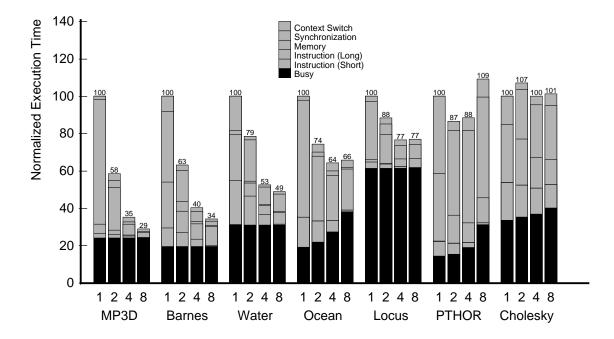

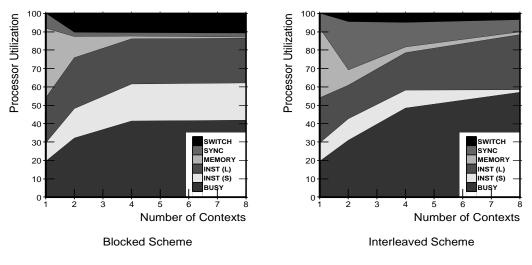

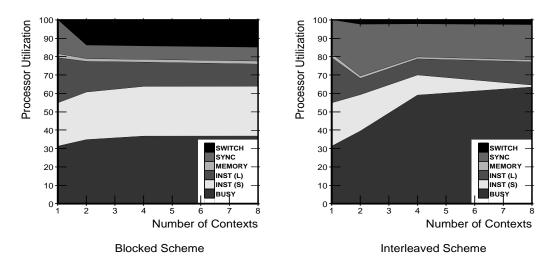

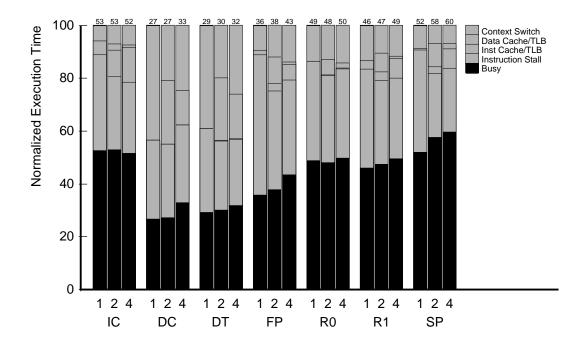

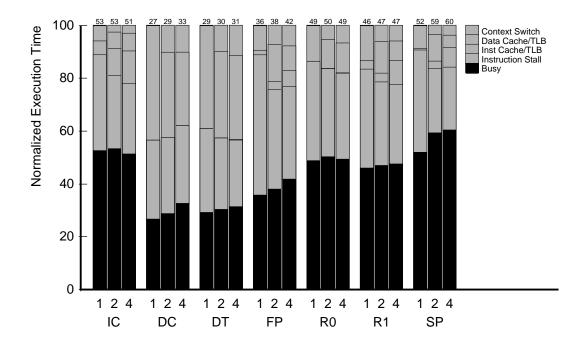

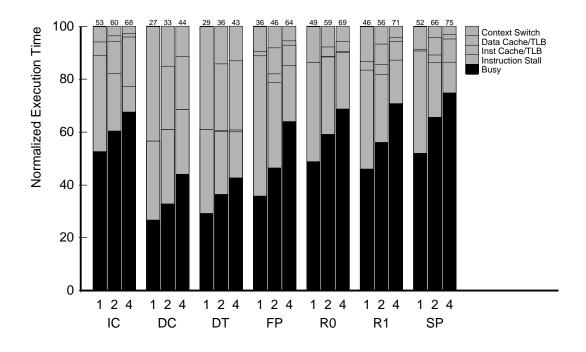

| 3.6  | Application execution time breakdown for the blocked scheme                     | 35 |

| 3.7  | Application execution time breakdown for the interleaved scheme                 | 35 |

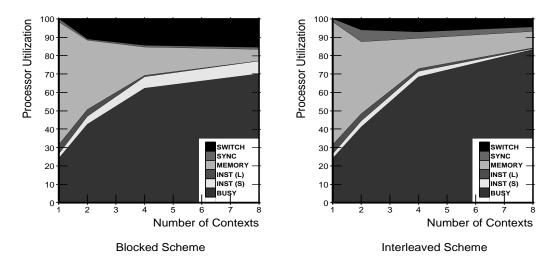

| 3.8  | Processor utilization for MP3D.                                                 | 37 |

| 3.9  | Processor utilization for Barnes.                                               | 38 |

| 3.10 | Processor utilization for Water.                                                | 39 |

| 3.11 | Blocked scheme with nonblocking loads.                                          | 47 |

| 3.12 | Interleaved scheme with nonblocking loads.                                      | 47 |

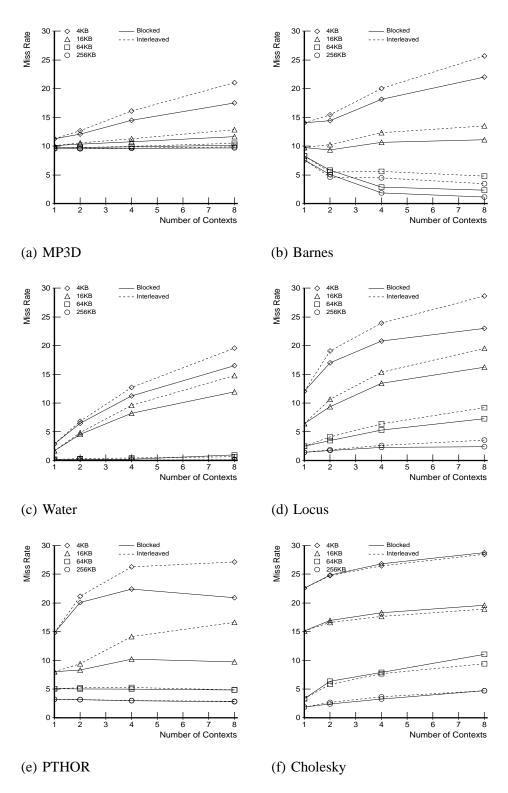

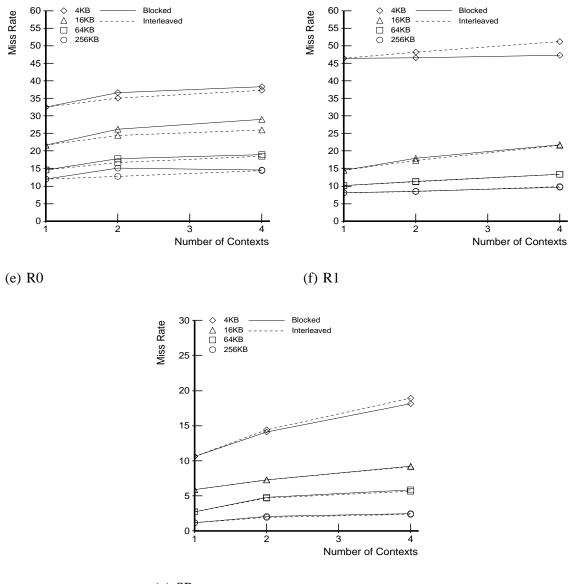

| 3.13 | Miss rates for varying cache sizes.                                             | 51 |

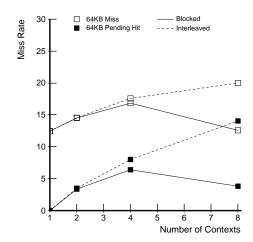

| 3.14 | Ocean miss rates for a 64 KByte data cache.                                     | 52 |

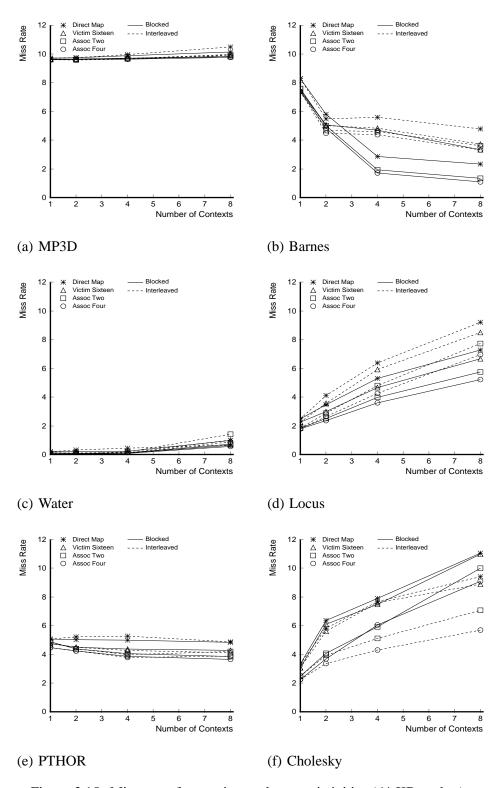

| 3.15 | Miss rates for varying cache associativities (64 KB caches)                     | 53 |

| 4.1  | Base uniprocessor architecture.                                                 | 57 |

| 4.2  | Blocked scheme processor utilization — switch on primary cache miss             | 62 |

| 4.3  | Blocked scheme processor utilization — switch on secondary cache miss              | 63  |

|------|------------------------------------------------------------------------------------|-----|

| 4.4  | Interleaved scheme processor utilization.                                          | 64  |

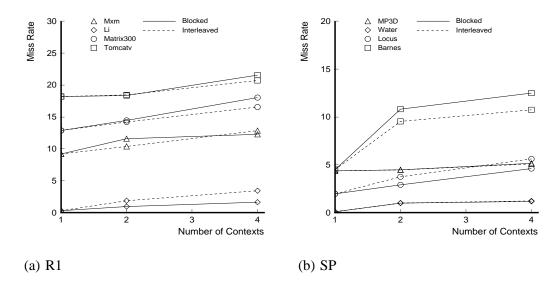

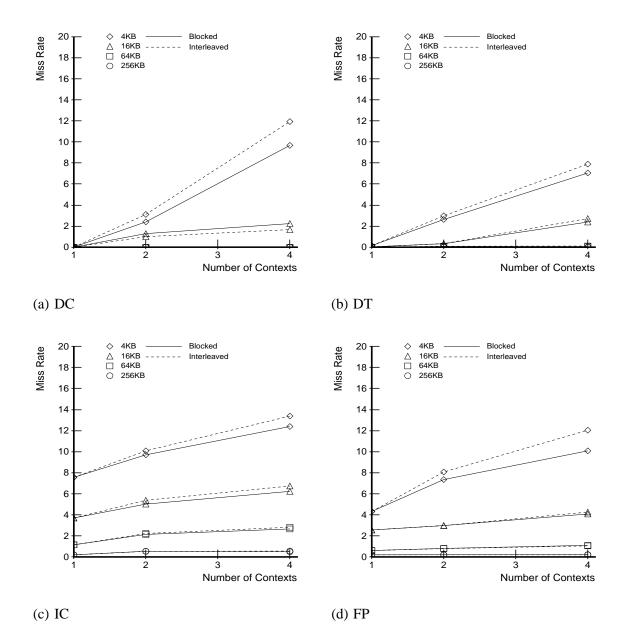

| 4.5  | Data cache read miss rates for varying cache sizes                                 | 69  |

| 4.5  | Data cache read miss rates for varying cache sizes (continued)                     | 70  |

| 4.6  | Data cache read miss rates by application for the 64 KByte cache                   | 71  |

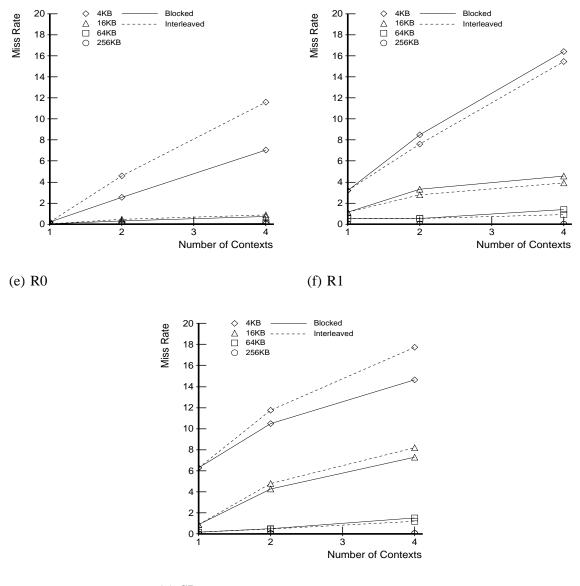

| 4.7  | Instruction cache miss rates for varying cache sizes                               | 72  |

| 4.7  | Instruction cache miss rates for varying cache sizes (continued)                   | 73  |

| 5.1  | Format of each line in the DASH Remote Access Cache.                               | 78  |

| 5.2  | Data cache hierarchy.                                                              | 80  |

| 5.3  | Lockup-free cache supporting relaxed memory consistency using a pending-write      |     |

|      | buffer                                                                             | 86  |

| 5.4  | Buffer deadlock example.                                                           | 91  |

| 5.5  | Instruction-data thrashing scenario.                                               | 94  |

| 5.6  | Invalidation thrashing scenario.                                                   | 95  |

| 5.7  | Replacement thrashing scenario                                                     | 95  |

| 5.8  | Adaptive stalling handling replacement thrashing.                                  | 96  |

| 5.9  | Adaptive stalling handling invalidation thrashing                                  | 97  |

| 5.10 | Adaptive stalling handling instruction-data thrashing                              | 97  |

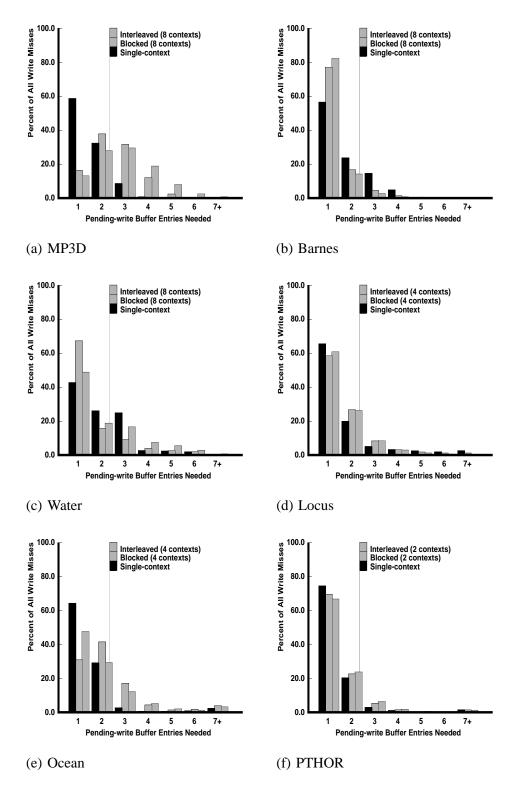

| 5.11 | Histogram of number of outstanding write misses encountered by each write miss     |     |

|      | (includes the miss itself).                                                        | 102 |

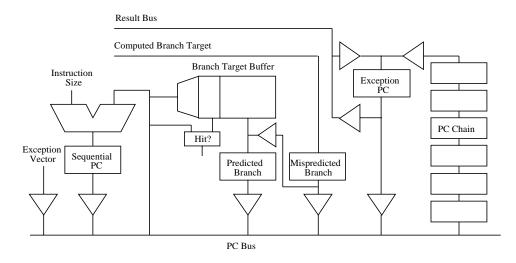

| 6.1  | Single-context processor PC unit.                                                  | 109 |

| 6.2  | Branch target generation and prediction verification for the base single-context   |     |

|      | processor.                                                                         | 110 |

| 6.3  | Two-context processor PC unit.                                                     | 111 |

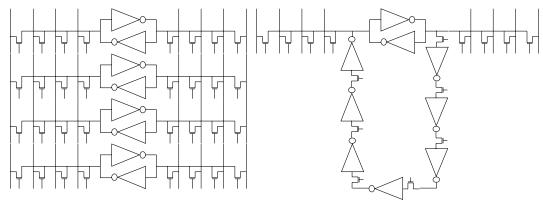

| 6.4  | Cells for both the replicated and apportioned register files                       | 113 |

| 6.5  | Timeline for a context switch.                                                     | 118 |

| 6.6  | Timeline for a fast explicit context switch with a replicated register file        | 120 |

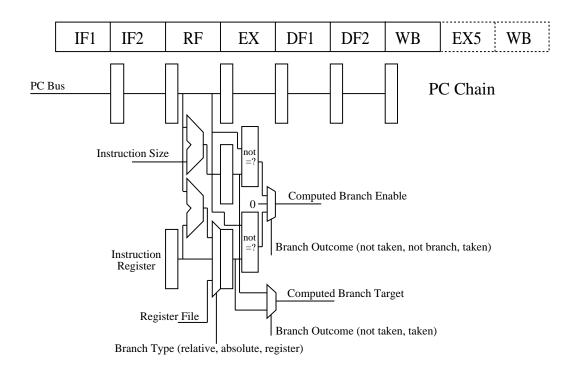

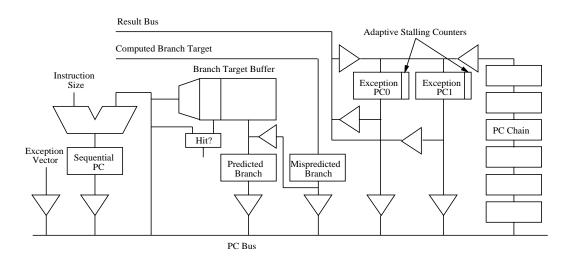

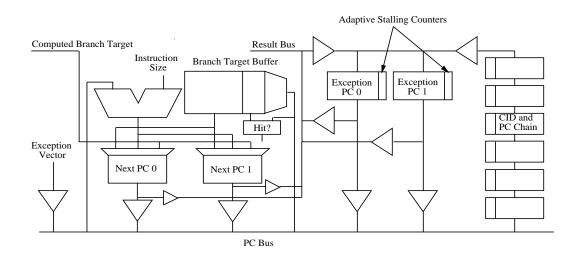

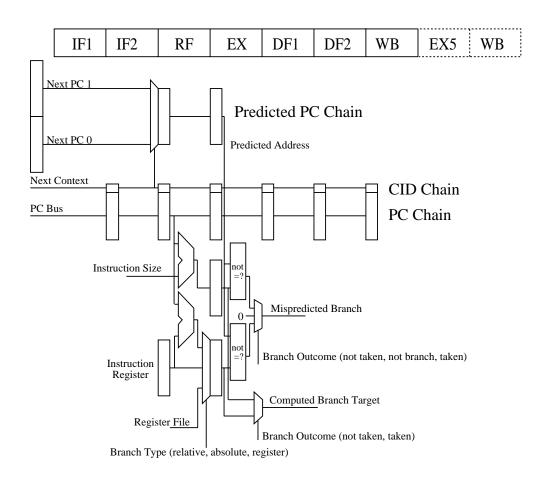

| 7.1  | Two-context processor PC unit.                                                     | 124 |

| 7.2  | Branch target generation and prediction verification for the interleaved multiple- |     |

|      | context processor.                                                                 | 126 |

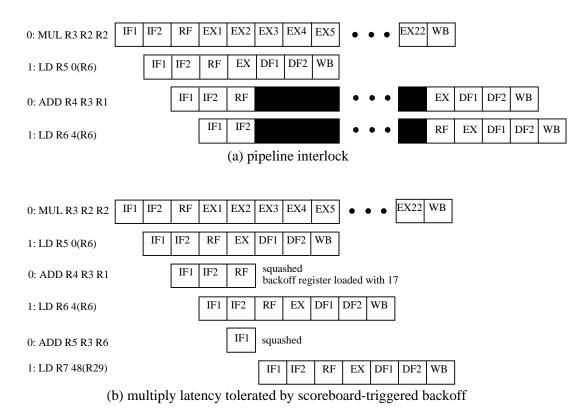

| 7.3  | Instruction latency toleration using dynamic context backoff detection             | 130 |

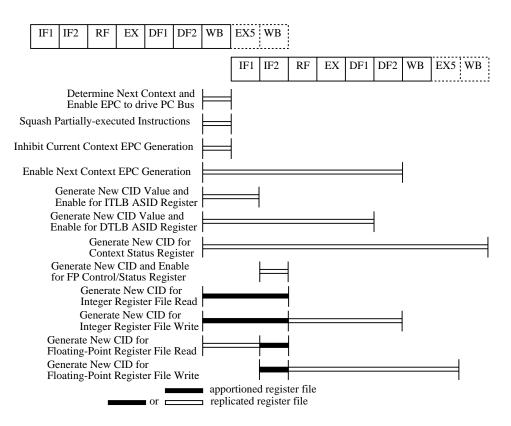

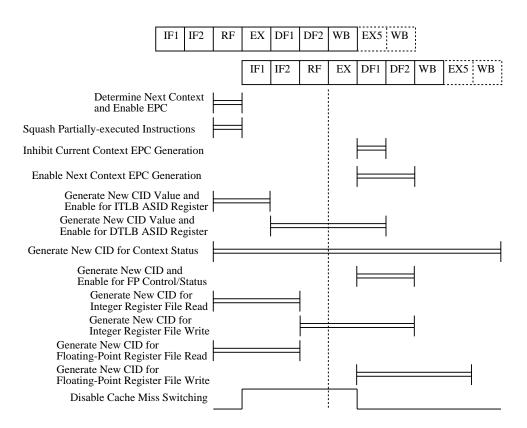

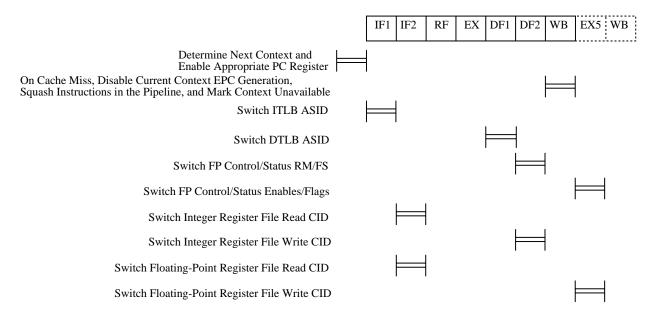

| 7.4 | Timeline for control of the interleaved multiple-context processor pipeline      | 132 |

|-----|----------------------------------------------------------------------------------|-----|

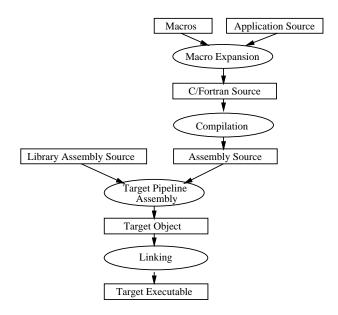

| A.1 | Target "executable" compilation path.                                            | 139 |

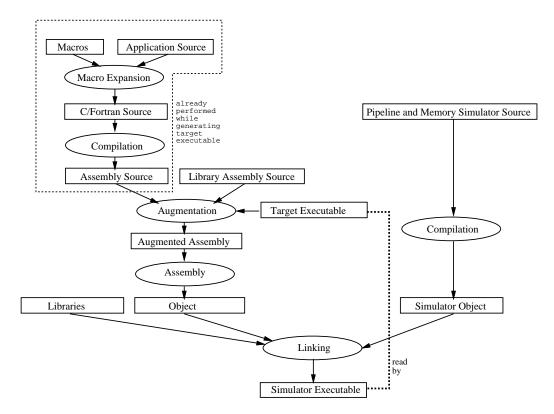

| A.2 | Tango-Lite compilation path.                                                     | 140 |

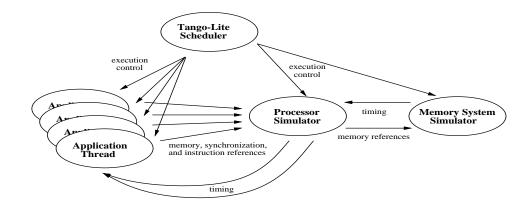

| A.3 | Tango-Lite execution model.                                                      | 141 |

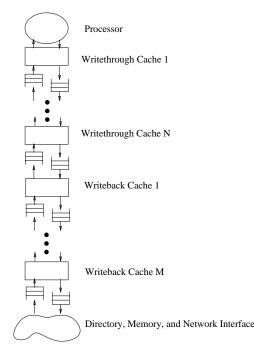

| C.1 | General cache hierarchy.                                                         | 149 |

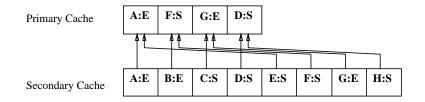

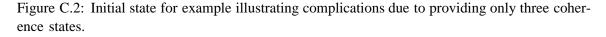

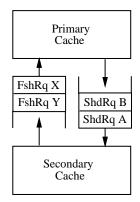

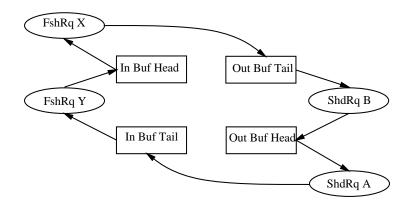

| C.2 | Initial state for example illustrating complications due to providing only three |     |

|     | coherence states                                                                 | 150 |

| D.1 | Buffer deadlock example.                                                         | 158 |

| D.2 | Resource graph for buffer deadlock example.                                      | 159 |

| D.3 | Permitted message transitions between buffers                                    | 160 |

| D.4 | Permitted message transitions between buffers for cache hierarchy with a single  |     |

|     | level of writeback caches.                                                       | 161 |

| D.5 | Example for deadlock avoidance solution.                                         | 162 |

| E.1 | EntryHi and EntryLo registers.                                                   | 167 |

| E.2 | EntryHi and EntryLo registers, modified for two contexts                         | 168 |

| E.3 | Status register.                                                                 | 169 |

| E.4 | Context status register (for two contexts)                                       | 170 |

| E.5 | Floating-point control/status register.                                          | 171 |

| E.6 | Floating-point control/status register, modified for two contexts                | 171 |

| E.7 | Interleaved floating-point control/status register.                              | 172 |

### Chapter 1

## Introduction

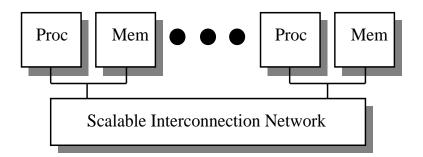

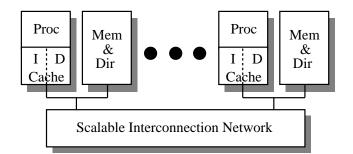

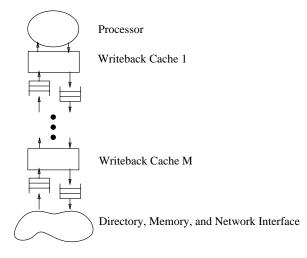

The increasing computational requirements of applications has resulted in considerable interest in the design of shared-memory multiprocessors which can scale to large numbers of processors [CGB91, KCA91, BFKR92, Hag92, LLJ<sup>+</sup>93]. Most of these *scalable* shared-memory multiprocessors have a similar basic structure, as shown in Figure 1.1. Memory is distributed with each processing node and the nodes are connected via a low-latency, high-bandwidth network. Cache coherence is maintained through the use of a directory-based coherence protocol [Tan76, CF78, CKA91, Len92, Web93], where the directory is distributed along with the memory and keeps information on which caches are sharing each memory location. The distributed nature of memory on these machines results in low-cost accesses to cache and local memory; however, cache misses which require remote memory accesses are fairly expensive.

Figure 1.1: General structure of a scalable multiprocessor.

Since these multiprocessors harness together large numbers of high-performance processors, their peak performance is quite impressive. In practice, however, many applications realize only a small fraction of the peak performance. One of the key obstacles limiting application performance is the long latency of remote memory operations [GHG+91, CB92]. By exploiting techniques to avoid or tolerate these long-latency memory operations, application performance can be significantly improved.

There are several ways to avoid memory latency. These include the caching of shared data, which allows the processor to keep a copy of frequently referenced data close by, thereby exploiting temporal and spatial locality in the data stream. The application can also be restructured to further take advantage of cache locality (e.g. by blocking the data accesses for the cache [LRW91]) and memory locality (e.g. allocating data on the local memory of the processor most likely to use it). While all of these methods improve the amount of computation a processor performs before requiring a long-latency memory access, often applications still end up spending a large portion of their time waiting on memory references [GHG<sup>+</sup>91]. To deal with this remaining latency, several latency tolerating schemes have been proposed, including relaxed memory consistency models [DSB86, SD87, AH90, GLL<sup>+</sup>90, Goo91], prefetching [CKP91, CB92, MLG92] and multiple-context processors [Smi81, HF88, WG89b, ALKK90, ACC<sup>+</sup>90, BR92, LGH92].

Relaxed memory consistency loosens the ordering constraints between specific memory operations to allow buffering and pipelining of memory references. Prefetching relies on being able to predict the future use of a data item. Data references whose access can be predicted in advance are then brought into the cache via nonblocking memory operation, with the goal that by the time the data is actually needed, it will reside in the cache. Multiple-context processors tolerate latency by overlapping the long-latency operations of one thread of computation with the execution of other thread(s) and are an interesting and flexible method for tolerating many forms of latency. However, while prefetching and relaxed consistency models are being incorporated into the latest microprocessor designs [Dig92a, JMY92, Hei93], multiple contexts has so far largely been ignored.

In this thesis, we focus on the multiple context solution. We examine the reasons behind its lack of acceptance by microprocessor designers. We then propose a multiple-context architecture capable of addressing these concerns. We look in detail at the performance and implementation complexity of both our proposed architecture and the current multiple-context approaches, showing that our proposed architecture makes it possible to build a multiple-context processor that provides good performance across a range of systems at a reasonable implementation cost.

### **1.1 The Latency Problem**

In addition to the large memory latencies possible in a scalable shared-memory multiprocessor, application performance on these machines suffers from the latency of inter-process synchronization, and instructions which take multiple cycles to produce their result. In this thesis, we will refer to these three types of latency as: *memory*, *synchronization*, and *instruction* latency, respectively.

For most applications that have been studied on large-scale, shared-memory multiprocessors, memory latency dominates synchronization and instruction latency in determining an application's performance, even after providing coherent caches and structuring the applications to take advantage of the cache and memory hierarchy [GHG<sup>+</sup>91, KCA91, LGH92]. The importance of memory latency in determining parallel application performance is based on two conspiring factors. First, because different processes are cooperating on the same problem, data communication between the processes adds to the cache miss rate. This communication component of the cache miss rate is often much larger than uniprocessor cache miss effects, and can dominate the cache miss behavior [WG89a]. Second, the latency for cache misses is larger than in a uniprocessor due to the physical distribution of memory. Increased miss rates due to communication and the long memory latency have a multiplicative effect, resulting in a large amount of time being lost in the memory system.

Synchronization and instruction latency play a secondary, but important, role in determining multiprocessor utilization [KCA91, LGH92]. Synchronization latency includes any time one process spends waiting on another process, such as time spent in barriers to synchronize all processes and time spent acquiring and releasing locks protecting application critical sections. This latency varies widely by application and is very difficult to remove architecturally since it represents a control dependency between the processes. Finally, instruction latency arises due to pipelining of the processor, which causes some instructions to take multiple cycles to produce their result. Compilers schedule instructions to overlap much of this latency with execution of independent instructions, however, even aggressive compiler scheduling cannot tolerate all instruction latency.

The first step to addressing these three forms of latency is to reduce or avoid as much of the latency as possible. Latency reduction techniques include coherent caching and blocking transformations to lower memory latency, hardware and software primitives for fast synchronization, and fast functional units and pipeline bypassing for reduced instruction latency. Unfortunately, even

after aggressively applying these and other techniques, a processor can still spend a significant portion of its time idle [GHG<sup>+</sup>91, LGH92] and some form of latency tolerance, such as multiple contexts, must be employed to improve performance further.

### **1.2 The Multiple-Context Solution**

Multiple-context processors share a single processor between several threads of computation, overlapping the latency encountered by one context with useful work by another context.<sup>1</sup> In order for multiple contexts to work well, the cost to switch between contexts needs to be much smaller than the long-latency operation to be tolerated.

The earliest multiple-context processors, such as the Denelcor HEP [Smi78] switched contexts each cycle, making the cost to switch contexts zero. This low switch cost allowed all three forms of latency to be tolerated. Unfortunately, each context in these early designs was limited to a single instruction being active in the pipeline. This constraint prevented pipeline dependencies from arising, allowing the processor design to be simplified, however, it placed two onerous burdens on applications. First, a large number of threads were necessary to fully utilize the processor — enough to both fill the pipeline and hide the memory latency. Second, the performance of a single thread was extremely poor, as each thread could issue a new instruction every pipeline-depth cycles at best. Therefore, any serial portion of an application could greatly impact the overall application performance. The limitations of these early designs were quite severe and most recent designs have instead focused on another technique for building multiple-context processors.

Multiple-context processors of this second type, exemplified by Weber and Gupta [WG89b] and the MIT APRIL [ALKK90], share the processor between a number of contexts; however, a single context utilizes all of the processor resources until it reaches a long-latency operation, such as a cache miss, at which point the processor switches to another context. Because blocks of instructions are executed between context switches, this second scheme has been referred to as *blocked* [FP91, KCA91]. The original HEP-style scheme has since been labeled *fine-grained* [KCA91].

Blocked multiple-context processors address the poor single-thread performance and need for large number of contexts of the fine-grained schemes, but they do so at the expense of increasing the context switch cost. The decision to switch contexts depends on determining

<sup>&</sup>lt;sup>1</sup>In this thesis, we use the words *context* and *thread* interchangeably.

whether a cache miss occurred and this determination is made late in the pipeline. Without extensive modifications to the processor, the cost to switch contexts will be close to the depth of the pipeline, as the partially-executed instructions from the switching context will need to be flushed from the pipeline.

This high context switch cost prevents blocked multiple-context processors from being able to tolerate very short latencies, such as those caused by pipeline dependencies and primary cache misses where the miss is serviced by a secondary cache. Trading-off the ability to tolerate these smaller latencies for good single-thread performance makes sense for a multiprocessor, as multiprocessor performance is mainly determined by the effects of long-latency memory operations. However, the processor performance impact of multiple contexts should not be examined only for multiprocessor systems, as most multiprocessors are built using standard off-the-shelf microprocessors [Hag92, Thi92, LLJ<sup>+</sup>93, Cra93, GW94], in order to take advantage of their high performance and commodity costs. These off-the-shelf microprocessors are still primary sold for use in uniprocessors, making it important that multiple contexts are also able to address their latencies. Being able to tolerate shorter latencies is much more important for uniprocessors, where memory does not need to be distributed, making all memory access local, and not having to deal with communication traffic allows effective cache hierarchies to be built, reducing the frequency that even this nearby memory needs to be accessed. If commodity microprocessors are to ever incorporate multiple contexts, the switch cost must be lowered to allow uniprocessor latencies to be tolerated.

### **1.3** This Thesis

In Chapter 2, we examine previous multiple-context proposals in detail to determine if a multiplecontext processor with a lower switch cost can be built. We then propose a new *interleaved* multiple-context processor which combines the cycle-by-cycle switching of the fine-grained schemes with the data caching and full single-thread support of the blocked scheme to achieve a low context switch cost and good single thread performance. We present some examples illustrating the potential performance advantages of the interleaved scheme over the blocked scheme, and then briefly discuss the implementation requirements of both approaches.

To quantify the performance advantages of the interleaved scheme, Chapter 3 presents a simulation study which explores the use of interleaved multiple-context processors in a sharedmemory multiprocessor similar to the Stanford DASH [LLJ+93]. The interleaved scheme is shown to provide significant performance gains over the blocked scheme in this environment. Chapter 3 also verifies that the performance advantages of the interleaved scheme hold over a number of multiprocessor architectural variations, such as when multiple contexts are combined with release consistency and nonblocking loads, and as memory latency and cache size and associativity are varied.

To evaluate the ability of the interleaved multiple-context processor in tolerating the smaller latencies of uniprocessors, we examine the effectiveness of multiple contexts on a multiprogrammed, high-performance uniprocessor in Chapter 4. We show that the blocked scheme does little to improve application throughput, whereas the interleaved scheme is able to show large increases in throughput due to its fast context switch and ability to tolerate instruction latency. Chapter 4 also shows that a multiprogrammed workload places larger demands on resources shared between the contexts, such as the caches and translation buffers, than was encountered for the multiprocessor applications. Despite the larger cache and TLB interference, the interleaved multiple-context processor is still quite effective in improving uniprocessor throughput.

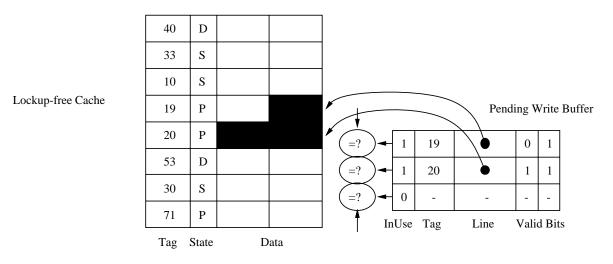

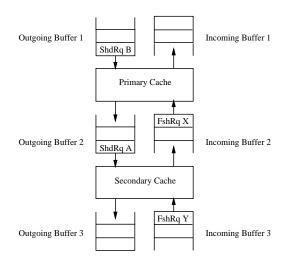

Chapters 3 and 4 show that the interleaved scheme provides a significant performance advantage over the blocked scheme. To examine the other side of the performance/cost tradeoff, Chapters 5–7 examine the implementation costs for both schemes. Since the ability of the cache to support multiple outstanding requests is central to any multiple-context design, we first examine the design of the lockup-free cache in Chapter 5. We propose a lockup-free cache that keeps track of outstanding memory operations directly in the cache via a pending state. This pending state allows compatible requests to be merged and prevents conflicting requests to the same cache line from being issued, thereby simplifying the design of the lockup-free cache. The chapter also explores deadlock issues for the lockup-free cache and then finishes with a detailed performance analysis of the proposed lockup-free design.

We then examine the remaining issues involved in implementing both the blocked and interleaved schemes in Chapters 6 and 7, respectively. The costs beyond the lockup-free cache can be broken into two major components: state replication and context scheduling logic. We show that the amount of replicated state is small for both schemes. We also show that the context scheduling logic for the blocked scheme is simpler than the interleaved scheme, however, the scheduling logic for both schemes is relatively straightforward. Finally, Chapter 8 presents conclusions and future directions.

### **1.4 Contributions**

The main contributions of this dissertation are:

- Development of the interleaved multiple-context architecture, which combines the low context switch cost and instruction latency tolerance of the fine-grained scheme with the coherent caches and good single-thread performance of the blocked scheme, allowing the interleaved multiple-context processor to tolerate much shorter latencies than the blocked scheme.

- A detailed performance study of the proposed and existing multiple-context architectures on a modern, deeply-pipelined processor, using both multiprocessing and multiprogramming workloads, which shows the proposed interleaved scheme to have significant performance advantages for both workloads.

- Proposal of a novel lockup-free cache design which allows only a single outstanding request

per cache line, simplifying the cache implementation at a negligible cost in performance.

A detailed performance study points out the importance of keeping occupancy of memory

operations low and the negligible effect of collisions due to multiple requests to the same

pending cache line.

- Detailed examination of the implementation issues for the proposed multiple-context architecture, showing that the amount of state which needs to be replicated is small. In addition, our implementation study shows that while the interleaved processor is more complex than a comparable multiple-context processor using the blocked scheme, this extra complexity is not overwhelming.

### Chapter 2

# **A New Multiple-Context Processor**

Existing multiple-context designs do not provide both a low context switch cost and full support for singlethreaded operation. Fine-grained processors have a very low switch cost, but poor single-context performance. On the other hand, blocked processors fully support the single context, but the cost of context switching is much higher than the fine-grained schemes.

This chapter starts by examining the previous multiple-context designs in more detail in Sections 2.1 and 2.2. In Section 2.3 we observe that the cycle-by-cycle switching of the fine-grained scheme can be combined with the coherent caches and full single-context support of the blocked scheme. This new multiple-context design, which we call *interleaved*, satisfies the twin goals of low switch cost and full single-context support. Several examples are presented to illustrate the differences between the new, interleaved multiple-context processor and the existing blocked scheme. We conclude Section 2.3 by presenting an overview of the implementation requirements of both the blocked and interleaved schemes. Related work is discussed in Section 2.4, and Section 2.5 summarizes the chapter.

### 2.1 Fine-grained Multiple-Context Processors

Multiple-context processors date back to the early 1960's, where they were used in the Control Data Corporation 6600 to time-share a CPU and memory interconnect between a number of peripheral processors [Tho64]. The earliest multiple-context processor proposals concentrated on the fine-grained architectures, with the seminal representative being the Denelcor HEP [Smi78, Smi81] built in the late 1970's. HEP consisted of a small number of processors interconnected to a number of memory modules via a packet-switched network. Fine-grained multithreading was

used by the processors to attack the problems of both pipeline stalls and memory latency. To address pipeline stalls, a context was prevented from issuing an instruction more than every eight cycles, which corresponded to the pipeline depth. Since an instruction could never encounter a pipeline dependency, no hardware or compiler resources had to be devoted to resolving pipeline hazards.<sup>1</sup> In addition, HEP provided the ability to tolerate the latency of a memory request by removing an instruction stream from the issue queue while memory was being accessed. Since HEP did not support data caches, large numbers of threads were required to hide both the pipeline and memory latency. For this reason, each HEP processor supported up to 128 active contexts.

HEP continues to evolve, and has been through two more incarnations. The Horizon [KS88, TS88] succeeded HEP. The processing elements were superscalar, capable of issuing three operations per cycle. The major architectural advancement of the Horizon was the addition of a lookahead field to each instruction, which encoded instruction dependencies, allowing multiple instructions to simultaneously use the pipeline. Lookahead provided limited compiler-resolved pipeline interlocks. Due to the size of the lookahead field, a maximum of eight instructions from the same context could be simultaneously executing. Unfortunately, like HEP, Horizon did not support caches. While instruction lookahead decreased the number of contexts needed for full pipeline utilization, a single context could still not fully utilize the pipeline. This is because the average response time of memory was expected to be around 50-80 cycles, and a lookahead of eight instructions is not nearly large enough to allow a pipeline this deep to be filled.

Horizon was a paper design. The Tera [ACC<sup>+</sup>90, AAC<sup>+</sup>91] computer is based on much of the Horizon design, and is currently being built by the Tera Computer Company. It enhances Horizon by improving the support for thread management and synchronization and by requiring lookahead only for memory operations. Memory lookahead helps to reduce the number of contexts needed to tolerate Tera's expected 70 cycle memory latency. Unfortunately, Tera ensures that register dependencies are respected by reverting to HEP's policy of limiting each context to a single instruction in the pipeline (although, unlike HEP, once an instruction has caused its memory reference to be issued, the next instruction can be issued if the lookahead for all previous instructions is satisfied). Since Tera is expected to have a pipeline of between 11 and 13 stages, at least this many contexts will be needed to fill the pipeline.

Kaminsky and Davidson also proposed another early fine-grained multiple-context processor [KD79]. The primary goal of their multiple-context proposal was not to hide memory or

<sup>&</sup>lt;sup>1</sup>An exception to this is the divide unit, which could not sustain an issue rate of one divide per cycle.

pipeline latency, but rather to effectively utilize chip and pin resources. This is essentially another way of looking at the same problem, since increasing the utilization of chip and pin resources occurs by overlapping time that would be spent idle by one context with the active time of another context. The main focus of the paper is on a design methodology for utilizing chip resources efficiently when developing a multiple-context processor. Interestingly enough, as a case study, they look into the use of virtual registers, an idea that has been reexamined recently [ND91].

A few more recent architectures have been based on the fine-grained scheme, including MASA [HF88], DART [SB91], and the Stellar SPMP [SMM88]. However, most recent multiplecontext designs have avoided the fine-grained scheme because of its inability to efficiently handle code with limited parallelism. As mentioned in Chapter 1, to overcome this limitation of finegrained multiple-context processors, blocked multiple-context processors were proposed.

### 2.2 Blocked Multiple-Context Processors

The blocked multiple-context processor provides hardware for a small number of resident threads, but only executes a single thread at any given time. Long-latency operations are masked by switching to another thread. Several early blocked multiple-context processors were proposed for hiding specific long-latency operations or allowing costly resources to be shared. The Xerox Alto personal computer provided multiple microcode-level registers sets for sharing the CPU between the instruction set interpreter and the I/O devices [TML<sup>+</sup>82]. To prevent the I/O from interrupting atomic series of microcode operations, a field was added to the microcode to specify points at which context switching was allowed. Another early example was the Message-Driven processor [DCC<sup>+</sup>87], which provided two hardware contexts, one for normal processor execution and the other for handling high-priority messages.

The first published exploration of multiple-context processors in a shared-memory multiprocessor environment was performed by Weber and Gupta [WG89b]. They performed trace-driven simulation of three parallel applications, with their processor switching contexts at each primary cache miss. Even with a relatively fast memory (20–30 processor cycles), they found performance benefits for blocked multiple-context processors with a small number of contexts (two or four) per processor.

More recently, the Alewife multiprocessor being built at MIT [KCA91, ACD<sup>+</sup>91] is designed with a blocked multiple-context processor, APRIL [ALKK90]. APRIL supports four contexts in hardware and is based on a modified SPARC [Cyp90] processor. APRIL performs context switching through a fast processor trap, switching contexts in 11 processor cycles. APRIL context switches whenever a memory request cannot be satisfied by the cache or local memory. In addition, APRIL provides the ability to force a context switch on a failed synchronization attempt. Using these two events as switch criteria, APRIL has the ability to tolerate the latency of both memory requests and synchronization.

While blocked multiple-context processors address the poor single-thread performance and need for large number of contexts of the fine-grained schemes, they do so at the expense of increasing the context switch cost. The high switch cost of the blocked multiple-context processor limits the types of latency which can be tolerated, and places an upper bound on the potential performance of the multiple-context processor. Assuming all memory latency is hidden by context switching, this upper bound is given in Equation 2.1.<sup>2</sup> The average runlength (the number of cycles between context switches) is broken into its components  $R_A$ , cycles active, and  $R_S$ , cycles stalled due to pipeline dependencies (which cannot be tolerated due to the high switch cost). *C* is the cost of a context switch. With memory latency completely tolerated, on average each context executes for  $R_A + R_S$  cycles, followed by *C*cycles for the switch to the next context. Of these  $R_A + R_S + C$ cycles, only  $R_A$  cycles are actually performing useful work. This upper bound can be fairly restrictive. For example, an application with a 20 instruction average runlength ( $R_A = 20$ ), a CPI of 1.5 with a perfect memory system ( $R_S = 10$ ), and a 10 cycle context switch cost will limit processor utilization to 50%.

$$Maximum Blocked \ Processor \ Utilization = \frac{R_A}{R_A + R_S + C}$$

(2.1)

In attempt to reduce this switch cost, a few blocked architectures have been proposed which replicate the pipeline registers [ND91, Omo91]. With this pipeline register replication, the contextswitch cost could be a low as a single cycle (at least one cycle is needed to broadcast the switch decision to the entire chip for use by the TLB, pipeline forwarding logic, etc.) Unfortunately, pipeline register replication comes at a substantial implementation and performance cost. Replicating the pipeline registers results in a substantial increase in pipeline size, as latches which hold pipeline state are a significant fraction of the total pipeline area. In addition, the outputs of these replicated latches need to be multiplexed before being sent to the combinational portion of the pipeline. When these multiplexor delays are combined with the higher fanout and longer wire delays resulting from the area increase, it is difficult to imagine that the cycle time of the processor will not be significantly impacted. Instead of trying to reduce the switch cost

<sup>&</sup>lt;sup>2</sup>A simplified version of this upper bound, not accounting for pipeline dependencies, is developed in both [SBCvE90] and [Aga92].

of the blocked scheme by brute force, a better approach can be developed by reexamining the fine-grained scheme.

### 2.3 Interleaved Proposal

If one looks closely at the two major problems with fine-grained processors, the need for large numbers of active contexts and the poor single-thread performance, it becomes apparent that the limitations of the fine-grained scheme are not due to the cycle-by-cycle context switching. Instead, two decisions incorporated into most fine-grained processors are the culprits. The first is the decision to not support data caching, which makes every memory reference a long-latency operation. The second is the decision to prevent a context from having more than one instruction in the pipeline, thereby increasing the minimum latency of each instruction to the pipeline depth.

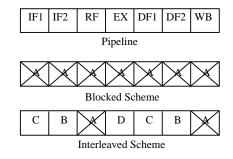

By adding both caching and full single-thread support to the fine-grained scheme, it becomes possible to design a multiple-context processor which interleaves contexts on a cycle-by-cycle basis, yet effectively supports a single context. This *interleaved* multiple-context processor works as follows. Issuing of instructions is switched each cycle between available contexts in a roundrobin fashion. Contexts become unavailable when they encounter a long-latency operation, and are made available when the long-latency operation completes. When a context becomes unavailable (an operation analogous to the context switch of the blocked scheme), the only instructions in the pipeline which are squashed are those of the context becoming unavailable. In addition, the cycle-by-cycle interleaving spaces out instructions from the same context, decreasing the probability that two dependent instructions from the same stream result in a pipeline stall.

### 2.3.1 Performance Advantages

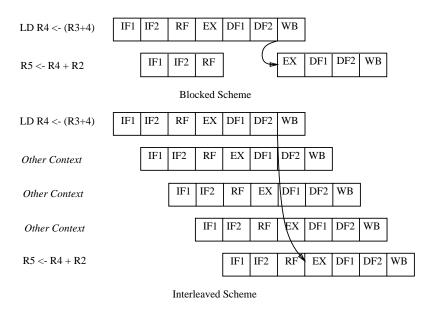

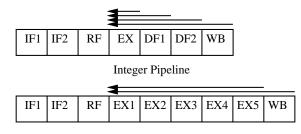

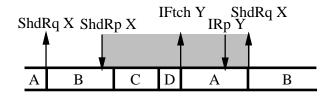

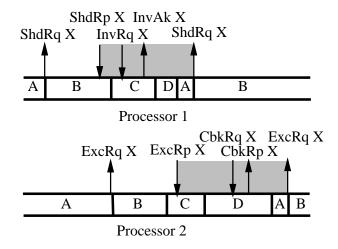

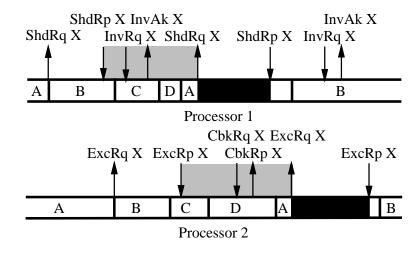

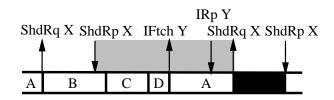

The interleaved scheme achieves its lower switch cost by squashing only the instructions in the pipeline from the context encountering the long-latency operation. To illustrate this lower context switch cost, let us examine a context switch induced by a cache miss for both the blocked and interleaved schemes. We will assume that each processor has four active contexts (labeled A - D), and that context A encounters the cache miss. Figure 2.1 shows the overhead to tolerate the latency of the cache miss for the pipeline we will be using in our simulations. The exact details of each pipeline stage will be discussed later; the important impact of the pipelining is that the cache access occurs late in the pipeline, and therefore the context switch determination cannot be made until the WB stage. As mentioned earlier, the blocked scheme will need to squash

all instructions in the pipeline (including the instruction which caused the cache miss) before it can start the next context and therefore a context switch costs seven cycles on the pipeline shown.<sup>3</sup> However, for the interleaved scheme, instructions from all four active contexts are being interleaved. Since only the instructions from context A need to be squashed, the overhead to handle the cache miss of context A is reduced to two cycles. Of course, the context switch cost of the interleaved scheme will depend on the number of contexts being interleaved, but even with a small number of contexts will be much lower than that of the blocked scheme.

Figure 2.1: Example illustrating the lower context switch cost of interleaved scheme.

The interleaved scheme also benefits from the cycle-by-cycle context switching tolerating short instruction latencies. Like the pipeline of a single-context processor, the interleaved processor stalls when an instruction needs a result from a previous instruction which has not yet been computed. However, because there are no dependencies between instructions from different contexts, if sufficient instructions from other contexts are interleaved between dependent instructions from the same context, the instruction latency dependency can be hidden. An example of this instruction latency tolerance is shown in Figure 2.2. Context A executes two instructions: a LOAD into R4 (with the load result available for forwarding at the end of DF2), and an ADD which uses the value of R4 as one of its operands. With the blocked scheme, these instructions will issue back-to-back, and as shown in Figure 2.2, the pipeline dependency is resolved by introducing a two cycle pipeline bubble. This bubble allows the result to be properly forwarded from the DF2 stage of the LOAD to the EX stage of the ADD. Assuming that four contexts are active, the cycle-by-cycle switching of the interleaved scheme provides enough delay between the two dependent instructions that the result of the LOAD is available before the EX stage of the ADD. Thus, the pipeline does not need to stall to insure that the result from the LOAD is ready for the ADD. As with the context switch cost, the number of cycles of any given pipeline

<sup>&</sup>lt;sup>3</sup>Alternately, the context switch cost can be viewed as the time needed by the next context to fill the pipeline.

dependency that can be tolerated by the interleaved scheme will depend on the exact context interleaving.

Figure 2.2: Example illustrating instruction latency tolerance by the interleaved scheme.

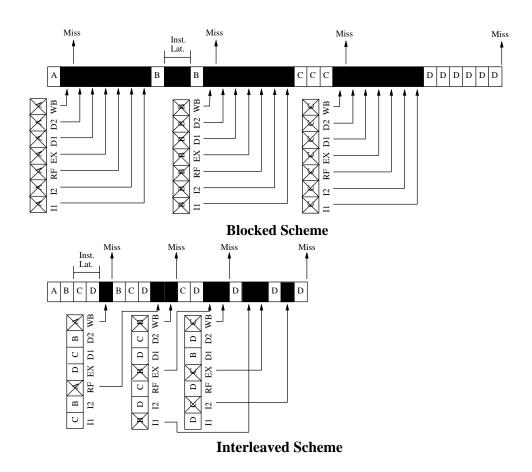

To further illustrate these two advantages of the interleaved scheme, we show the execution of four threads for both the blocked and interleaved schemes in Figure 2.3. The four threads are:

- A Issues two instructions, with the second causing a cache miss.

- **B** Issues one instruction, followed by a two cycle pipeline dependency, followed by two more instructions, the last of which cache misses.

- C Issues four instructions, with the fourth causing a cache miss.

- **D** Issues six instructions, with the last causing a cache miss.

The blocked scheme is shown on the upper timeline. Context A starts executing, issuing its two instructions, the second of which causes a cache miss. The pipeline must be flushed at this point before context B can execute, as shown below the timeline. Context B then executes one instruction, stalls due to the pipeline dependency, and then executes until it encounters its cache miss, at which point the pipeline is flushed and C starts executing, and so on. The interleaved scheme executing the same set of threads is shown on the lower timeline. The processor starts with all four contexts being interleaved. As we can see, this interleaving is enough to separate

the dependent instructions from Context B, completely hiding the instruction latency. The lower switch cost of the interleaved scheme is also illustrated in Figure 2.3; the switch cost associated with a cache miss is reduced from the seven cycles of the blocked scheme to two cycles for context A, three cycles for contexts B and C. Note that as contexts are made unavailable, the number of contexts being interleaved on the pipeline decreases, until we reach the point where only the single context D is being interleaved. As a result of the lower switch cost and pipeline dependency tolerance, the interleaved scheme was able to complete all four threads well before the blocked scheme.

Figure 2.3: Comparison of the blocked and interleaved multiple-context schemes for a set of four threads.

### 2.3.2 Implementation Requirements

Now that we have outlined the performance advantages of the interleaved scheme, we will briefly discuss the hardware requirements for the two schemes to get a feel for their complexity.

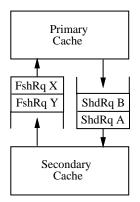

The first requirement of all multiple-context processors is that the cache be capable of handling multiple outstanding memory requests. These caches are called *lockup-free*, and are more expensive than standard blocking caches. We will explore the design of these caches in detail in Chapter 5. Beyond providing a lockup-free cache, the blocked and interleaved multiple-context schemes have differing requirements, and we briefly discuss these requirements here. Chapters 6 and 7 will explore these requirements in more detail.

#### **Blocked Scheme**

In order to reduce the context switch cost to a minimum, the blocked multiple-context processor needs to replicate all the process-specific state on the processor. This state includes the program counter, the register file, and any miscellaneous process-specific state from the processor status word. In addition to this state replication, the blocked multiple context processor must provide some mechanism for causing a context switch on long-latency operations.

Memory latency can be tolerated by providing hardware mechanisms to force a context switch on each data cache miss. When this hardware detects a cache miss, any partially executed instructions in the pipeline are marked to not update any processor state, and the next context immediately starts filling the pipeline. Eventually the processor will switch back to the original context, which will reissue its load or store instruction, and hopefully the data for this instruction will now be loaded into the cache.

Synchronization latency in a blocked multiple-context processor can be tolerated by providing an *explicit context switch* instruction. With an explicit context switch instruction as the basic mechanism, a number of synchronization latency tolerance policies can be implemented [ALKK90]. Note that since the blocked processor runs one context until that context encounters a long-latency operation, providing an explicit switch (or some form of watchdog timer [WG89b]) is essential to avoid deadlock between synchronizing processes which are loaded on the same processor.

The explicit switch instruction can also be used to tolerate instruction latency on a blocked multiple-context processor. The blocked scheme can tolerate instruction latency only if the cost of the instruction latency is larger than the cost of an explicit context switch instruction. By inserting an explicit switch instruction before an instruction which uses the result of a previous long-latency instruction, the latency of the previous instruction can be tolerated. Unfortunately, the blocked scheme does not have a mechanism for tolerating instruction latencies which are shorter than the cost of the explicit switch instruction.

### **Interleaved Scheme**

The interleaved scheme also requires each context to have its own copy of the program counter, register file, and any miscellaneous process-specific state from the processor status word. Unlike the blocked scheme, this state is replicated not to keep the switch cost down, but rather to allow the multiple contexts to be simultaneously active.

Issuing instructions from multiple active streams requires the interleaved multiple-context processor to have a more sophisticated instruction issue unit than the blocked processor. In addition, sharing the pipeline between multiple contexts requires the pipeline to be able to identify which context an instruction was issued from to properly implement result forwarding and to allow instructions from only one context to be squashed when that context needs to be made unavailable because of a long-latency operation.

Finally, the interleaved multiple-context processor must provide some mechanism for making contexts unavailable for the duration of long-latency operations. For memory operations, this can be accomplished by providing one *transaction buffer* per context which tracks the outstanding request of that context. When a cache miss occurs, this buffer is loaded with the address of the memory operation. Any instructions in the pipeline from the context encountering the miss are squashed and a signal is sent to the instruction issue unit to prevent further instructions from this context from being generated. When the reply to the cache miss returns, the transaction buffer is marked invalid, instruction issuing from this context is enabled again, and the context restarts by issuing a repeat of its memory request.

For the interleaved scheme, policies for synchronization latency tolerance can be built on top of a *backoff* instruction. The backoff instruction has the effect of making the context unavailable for the number of cycles specified by the instruction. Issuing this instruction is equivalent to the context encountering a cache miss of latency equal to the backoff value.

The interleaved scheme actually has two mechanisms which it can employ to tolerate instruction latency. As mentioned earlier, instruction latency can be tolerated by the cycle-by-cycle context interleaving. Since instruction latencies tend to be short, the cycle-by-cycle switching of the interleaved scheme should be very effective in tolerating most of this latency. Longer instruction latencies, that are likely to result in a stall even after interleaving, can be handled by the same backoff mechanism used to tolerate synchronization latency. This backoff can either be triggered automatically by a hardware scoreboard, in which case the backoff value will be exactly the amount needed to resolve the dependency, or it can be triggered by a backoff instruction.

### 2.4 Related Work

Recently, there has been an explosion of research into using an interleaved-like approach to increase the amount of instruction-level parallelism available to superscalar processors. This increase in research interest has been motivated by commercial microprocessors which are beginning to exploit instruction-level parallelism [Dig92b, JMY92]. This trend towards using more instruction-level parallelism to boost microprocessor performance is expected to continue. However, the amount of parallelism in a single stream is limited [Wal91, LW92]. As attempts are made to issue more and more instructions per cycle, the laws of diminishing returns take over, limiting performance improvements. To get around these diminishing returns, several researchers have proposed using multiple instruction streams.

Daddis and Torng [DT91] propose a dynamic superscalar architecture in which instructions from several contexts are used to fill a common instruction window. A group from the Media Research Laboratory of Matsushita have proposed an architecture aimed toward the processing element of a large-scale multiprocessor [HKN<sup>+</sup>92]. The processor consists of a number of independent instruction fetch and decode units which share several functional units. The architecture is superscalar in that multiple instructions from different threads can be issued in a single cycle; however, each thread can only issue a single instruction per cycle. Prasadh and Wu [PW91] and Keckler and Dally [KD92] both propose adding multiple contexts to a VLIW (very long instruction word) architecture. In both of these proposals, multiple threads, statically scheduled for a large number of functional units, are dynamically interleaved at runtime to improve functional unit utilization.

Unfortunately, most of the interleaved proposals for superscalar processors add multiple contexts to a processor with a very wide instruction issue in order to make the processor operate with reasonable efficiency at an expensive point in the design/complexity spectrum. Rather than making the processors extremely complex in order to get the last few percentage points of functional unit utilization, a more reasonable design would be to employ multiple simpler processors. Each processor would support more modest amounts of instruction-level parallelism, thereby making its design much simpler. Interleaved multiple contexts could then be added to these simpler processors to tolerate memory, synchronization, and instruction latency.

### 2.5 Summary

In this chapter we proposed an *interleaved* multiple-context processor that combines the cycleby-cycle switching of the fine-grained schemes with the coherent caches and full single-context support of the blocked scheme. This results in a processor with a much lower context switch cost than the blocked scheme, because the number of instructions in the pipeline that need to be squashed to tolerate a long-latency operation will often be much smaller. In addition, the cycle-by-cycle context switching helps to tolerate the latency of dependent instructions from the same context by separating them with instructions from other contexts.

We now need to quantify the performance advantages of the interleaved multiple-context processor. We have developed an event-driven simulation environment for comparing the blocked and interleaved schemes. In Chapter 3 we will examine the benefits of employing the two multiple-context schemes in a scalable shared-memory multiprocessor. Because it is important for multiple contexts to also be useful in a uniprocessor setting, Chapter 4 will explore the advantages of the interleaved scheme over the blocked scheme for a multiprogrammed, high-performance uniprocessor.

### Chapter 3

# Multiple Contexts: Utility for Multiprocessors

Chapter 2 qualitatively argued that a multiple-context processor built using the interleaved scheme should outperform one built using the blocked scheme. In this chapter this performance advantage is quantified for a shared-memory multiprocessor via simulation.

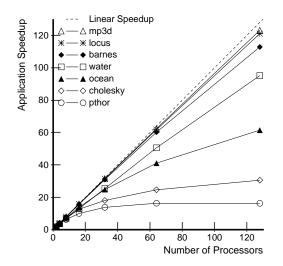

We start this chapter by describing our base architecture and simulation environment in Section 3.1. Event-driven simulation of the SPLASH [SWG92] application suite on a model of a shared-memory multiprocessor similar to the Stanford DASH [LLG<sup>+</sup>90] will be used to compare the blocked and interleaved schemes.

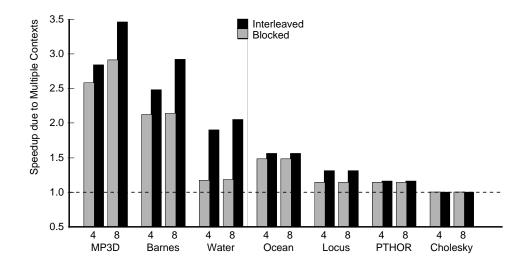

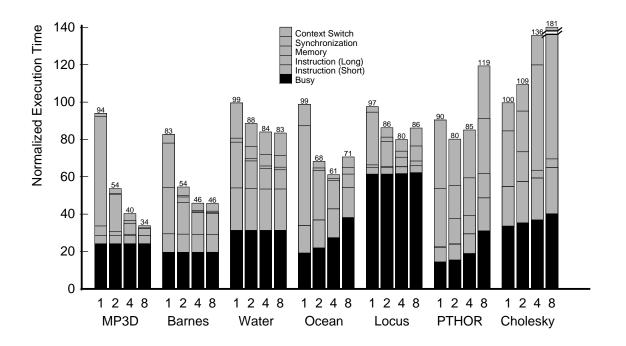

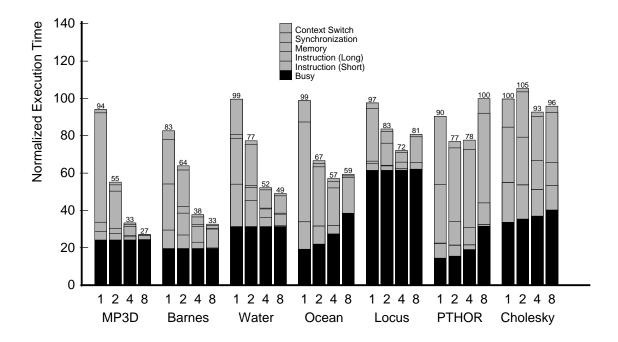

In Section 3.2, we present the results of the performance comparison between the two schemes. Multiple contexts prove to be extremely effective for three of the SPLASH applications (speeding them up by factors of 2.0 to nearly 3.5), show more modest gains for three of the applications (1.15 to 1.6 speedups), and do very little for the final application. The interleaved scheme does outperform the blocked scheme, especially for the three applications showing the largest gains from multiple contexts. For these three applications, the (geometric) mean speedup for eight contexts per processor is 2.75 for the interleaved scheme, compared to 1.94 for the blocked scheme. We end this section by exploring the characteristics of the individual SPLASH applications which determine both the general effectiveness of multiple contexts and the differences between the two schemes.

In order to ensure that our comparison of the blocked and interleaved schemes holds across a range of system assumptions, we then explore several variations to our base architecture and latency tolerance policies in Section 3.3, including varying memory latencies and cache sizes and associativities. The interleaved scheme retains its performance advantage over the blocked across all the variations.

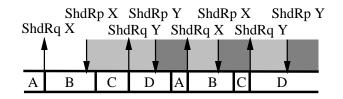

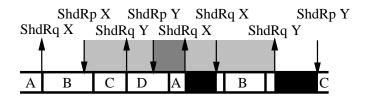

Section 3.4 examines the use of multiple contexts in combination with two alternative latency tolerance techniques: relaxed memory consistency models and nonblocking loads. Being able to combine well with these other latency tolerance schemes is important as the other schemes provide latency tolerance within a single thread and therefore work well when multiple contexts cannot be taken advantage of due to limited workload parallelism. Multiple contexts combines with both schemes without performance penalty. However, because multiple contexts can be used to tolerate the same latencies as relaxed memory consistency and nonblocking loads, only fairly modest performance gains are seen for combining the latency tolerance schemes over multiple contexts alone.

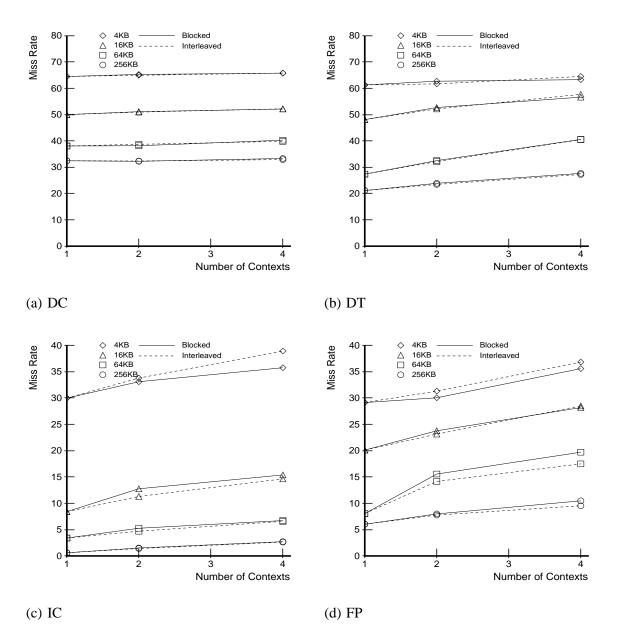

Interference in resources shared between the contexts, such as the caches and TLBs, is a frequently raised concern for multiple-context processors, and in Section 3.5, we show this the shared resource interference to be modest. In particular, cache interfence between the contexts is a frequently raised concern, and we show that, while multiple contexts generally increase the data cache miss rate, for larger caches this increase is small. Even with smaller caches where the miss rate does rise somewhat, much of the extra memory latency resulting from the increased misses can be tolerated by the multiple contexts.

# **3.1 Evaluation Methodology**

Before we present our simulation results we need to first describe our evaluation methodology. We start by presenting the base processor and system architecture. We then describe the simulation environment, and finally discuss the benchmark applications and simulation configurations used in the study.

#### **3.1.1 Base Architecture**

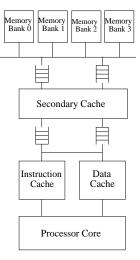

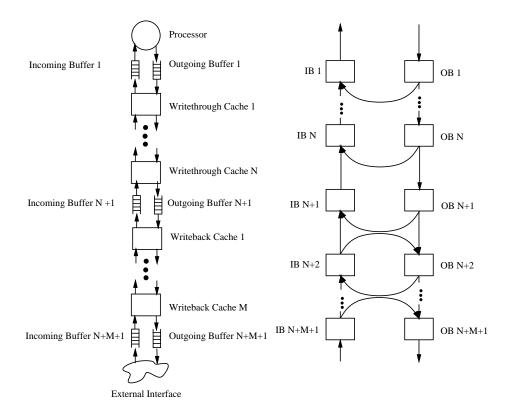

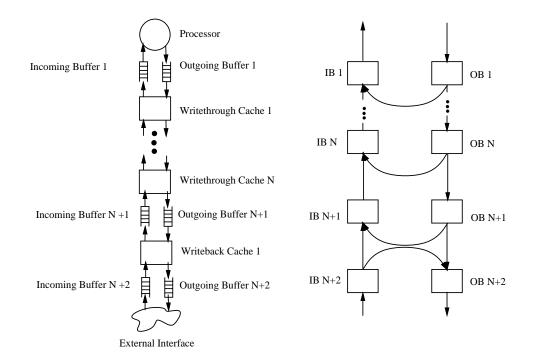

Figure 3.1 shows the base multiprocessor architecture selected for this study. This base architecture draws heavily upon the experience gained from building the DASH multiprocessor [LLG<sup>+</sup>92, LLJ<sup>+</sup>93]. The multiprocessor consists of a number of nodes connected together by a high-bandwidth, low-latency interconnect. Each node consists of a processor, cache, and a portion of the global memory. The caches are kept coherent using a distributed, directory-based protocol similar to that of DASH [LLG<sup>+</sup>90]. Our base architecture differs from DASH in two

Figure 3.1: Base multiprocessor architecture.

major respects. First, the DASH cluster of four processors is changed to contain a single, highperformance processor. This modification was made in order to remove the potential memory bandwidth bottleneck of the cluster bus. As a secondary consideration, removing the DASH clustering allowed the simulation model to be simpler, which in turn allowed larger problems to be simulated. Second, DASH employs a two-level data cache hierarchy. We have selected a single-level data cache hierarchy since our base architecture contains a fairly large (64 Kbyte) writeback primary cache, and therefore most misses will be due to communication, and multilevel hierarchies do not help with communication misses. In our variational analyses where we explore primary caches smaller than 64 Kbytes, we will back the primary cache with a large secondary cache.