### TOLERATING LATENCY THROUGH SOFTWARE-CONTROLLED DATA PREFETCHING

A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> By Todd C. Mowry May 1994

© Copyright 1994 by Todd C. Mowry All Rights Reserved

## Abstract

The large latency of memory accesses in modern computer systems is a key obstacle to achieving high processor utilization. Furthermore, the technology trends indicate that this gap between processor and memory speeds is likely to increase in the future. While increased latency affects all computer systems, the problem is magnified in large-scale shared-memory multiprocessors, where physical dimensions cause latency to be an inherent problem. To cope with the memory latency problem, the basic solution that nearly all computer systems rely on is their cache hierarchy. While caches are useful, they are not a panacea.

*Software-controlled prefetching* is a technique for tolerating memory latency by explicitly executing prefetch instructions to move data close to the processor before it is actually needed. This technique is attractive because it can hide both read and write latency within a single thread of execution while requiring relatively little hardware support. Software-controlled prefetching, however, presents two major challenges. First, some sophistication is required on the part of either the programmer, runtime system, or (preferably) the compiler to insert prefetches into the code. Second, care must be taken that the overheads of prefetching, which include additional instructions and increased memory queueing delays, do not outweigh the benefits.

This dissertation proposes and evaluates a new compiler algorithm for inserting prefetches into code. The proposed algorithm attempts to minimize overheads by only issuing prefetches for references that are predicted to suffer cache misses. The algorithm can prefetch both dense-matrix and sparse-matrix codes, thus covering a large fraction of scientific applications. It also works for both uniprocessor and large-scale shared-memory multiprocessor architectures. We have implemented our algorithm in the SUIF (Stanford University Intermediate Form) optimizing compiler. The results of our detailed architectural simulations demonstrate that the speed of some applications can be improved by as much as a factor of two, both on uniprocessor and multiprocessor systems. This dissertation also compares software-controlled prefetching with other latency-hiding techniques (e.g., locality optimizations, relaxed consistency models, and

multithreading), and investigates the architectural support necessary to make prefetching effective.

Key Words and Phrases: Data prefetching, tolerating latency, compiler optimization, computer architecture, shared-memory multiprocessors.

### Acknowledgments

Here is my top ten list of people I would like to acknowledge:

- 10. My fellow officemates in "the trailer", for devising new methods of opening doors while remaining seated, and ensuring that life as a graduate student was never a dull moment: Andrew Erlichson, J.P. Singh, Jim Laudon, Chris Holt, Mark Heinrich, Steve Woo, Dave Ofelt, Jeff Kuskin, and John Heinlein.

- **9.** My friends and mentors at MIPS, who made my Silicon Valley experience complete, and helped raise my standard of living above the starvation level: Earl Killian, Peter Davies, and Paul Ries.

- **8.** The DASH team, for answering all of my hardware questions, and for including me in their ski trip: Dan Lenoski, Jim Laudon, Kourosh Gharachorloo, Dave Nakahira, Truman Joe, and Wolf-Dietrich Weber.

- **7.** The simulator gurus who cheerfully and tirelessly supported their creations, thus making these quantitative results possible: Steve Goldschmidt for Tango, and Mike Smith for XSIM.

- 6. The SUIF team, for creating and supporting that wonderful porcine compiler: Steve Tjiang, Michael Wolf, Mike Smith, Jennifer Anderson, Rob French, Dror Maydan, Saman Amarasinghe, Todd Smith, and Bob Wilson.

- **5.** The faculty members who graciously served on my reading and orals committees: Albert Macovksi and Greg Kovacs.

- **4.** The fearless leader of our extended research family, for his wisdom and guidance throughout the years: John Hennessy.

- **3.** My "second" primary advisor, for teaching me what compilers are all about, and for giving me the luxury of having two sources of great advice: Monica Lam.

- **2.** My "primary" primary advisor, for the tremendous time, energy, and wisdom he invested in my graduate education, and for inspiring me to become an academic myself: Anoop Gupta.

- My spouse, who shared each step of the Stanford graduate experience with me, from our first day of class (when we met) through defending our dissertations (which we did within 24 hours of each other), and who was a very good sport during our "joint" academic job search: Karen Clay.

## Contents

| A | bstrac | ct                                                    | iii |

|---|--------|-------------------------------------------------------|-----|

| A | cknov  | vledgments                                            | v   |

| 1 | Int    | roduction                                             | 1   |

|   | 1.1    | Cache Performance on Scientific and Engineering Codes | 2   |

|   | 1.2    | Coping with Memory Latency                            | 4   |

|   |        | 1.2.1 Caches                                          | 4   |

|   |        | 1.2.2 Locality Optimizations                          | 5   |

|   |        | 1.2.3 Buffering and Pipelining References             | 6   |

|   |        | 1.2.4 Prefetching                                     | 7   |

|   |        | 1.2.5 Multithreading                                  | 9   |

|   |        | 1.2.6 Overall Approach                                | 11  |

|   | 1.3    | Research Goals                                        | 12  |

|   | 1.4    | Related Work                                          | 13  |

|   | 1.5    | Contributions                                         | 15  |

|   | 1.6    | Organization of Dissertation                          | 16  |

| 2 | Co     | re Compiler Algorithm for Prefetching                 | 18  |

|   | 2.1    | Key Concepts                                          | 19  |

|   | 2.2    | Overview of Algorithm                                 | 20  |

|   | 2.3    | Locality Analysis                                     | 21  |

|   |        | 2.3.1 An Example                                      | 23  |

|   |        | 2.3.2 Reuse Analysis                                  | 25  |

|   |        | 2.3.3 Localized Iteration Space                       | 31  |

|   |     | 2.3.4   | The Prefetch Predicate              | 40 |

|---|-----|---------|-------------------------------------|----|

|   | 2.4 | Schedu  | lling Prefetches                    | 42 |

|   |     | 2.4.1   | Loop Splitting                      | 42 |

|   |     | 2.4.2   | Software Pipelining                 | 45 |

|   | 2.5 | Putting | g It All Together                   | 46 |

|   |     | 2.5.1   | Example Revisited                   | 46 |

|   |     | 2.5.2   | Implementation Experience           | 50 |

| 3 | Dro | fotohin | g for Uniprocessors                 | 53 |

| 3 | 3.1 |         |                                     |    |

|   | 5.1 |         | mental Framework                    | 54 |

|   |     | 3.1.1   | Architectural Assumptions           | 54 |

|   |     | 3.1.2   | Applications                        | 55 |

|   |     | 3.1.3   | Compiler Parameters                 | 57 |

|   |     | 3.1.4   | Simulation Environment              | 58 |

|   | 3.2 |         | tion of Core Compiler Algorithm     | 58 |

|   |     | 3.2.1   | Locality Analysis                   | 60 |

|   |     | 3.2.2   | Loop Splitting                      | 64 |

|   |     | 3.2.3   | Software Pipelining                 | 66 |

|   |     | 3.2.4   | Summary                             | 67 |

|   | 3.3 | Sensiti | vity to Compile-Time Parameters     | 68 |

|   |     | 3.3.1   | Policy on Unknown Loop Bounds       | 68 |

|   |     | 3.3.2   | Effective Cache Size                | 69 |

|   |     | 3.3.3   | Prefetch Latency                    | 70 |

|   |     | 3.3.4   | Summary                             | 71 |

|   | 3.4 | Interac | tion with Locality Optimizations    | 71 |

|   |     | 3.4.1   | GMTRY: Cache Blocking               | 71 |

|   |     | 3.4.2   | VPENTA: Loop Interchange            | 72 |

|   |     | 3.4.3   | Summary                             | 73 |

|   | 3.5 | Prefetc | ching Indirect References           | 74 |

|   |     | 3.5.1   | Modifications to Compiler Algorithm | 74 |

|   |     | 3.5.2   | Experimental Results                | 77 |

|   | 3.6 | Chapte  | r Summary                           | 80 |

|   |     |         | -                                   |    |

| 4 | Pre | fetchin  | g for Multiprocessors                                    | 81  |

|---|-----|----------|----------------------------------------------------------|-----|

|   | 4.1 | Multip   | processor Issues and Modifications to Compiler Algorithm | 82  |

|   |     | 4.1.1    | Binding vs. Non-Binding Prefetches                       | 82  |

|   |     | 4.1.2    | Coherence Misses                                         | 84  |

|   |     | 4.1.3    | Exclusive-Mode Prefetching                               | 88  |

|   |     | 4.1.4    | Summary                                                  | 89  |

|   | 4.2 | Experi   | mental Framework                                         | 90  |

|   |     | 4.2.1    | Architectural Assumptions                                | 90  |

|   |     | 4.2.2    | Applications                                             | 91  |

|   |     | 4.2.3    | Simulation Environment                                   | 95  |

|   | 4.3 | Experi   | mental Results                                           | 96  |

|   |     | 4.3.1    | Locality Analysis                                        | 98  |

|   |     | 4.3.2    | Scheduling Algorithm                                     | 102 |

|   |     | 4.3.3    | Prefetching Indirect References                          | 105 |

|   |     | 4.3.4    | Exclusive-Mode Prefetching                               | 106 |

|   | 4.4 | Cache    | Size Variations                                          | 109 |

|   | 4.5 | Progra   | mmer-Inserted Prefetching                                | 112 |

|   |     | 4.5.1    | Cases Where the Compiler Succeeded                       | 112 |

|   |     | 4.5.2    | Cases Where the Compiler Failed                          | 115 |

|   |     | 4.5.3    | Summary                                                  | 118 |

|   | 4.6 | Chapte   | er Summary                                               | 119 |

| 5 | Arc | chitectu | ral Issues                                               | 121 |

|   | 5.1 | Basic    | Architectural Support for Prefetching                    | 121 |

|   |     | 5.1.1    | Instruction Set Architecture                             | 122 |

|   |     | 5.1.2    | Dropping Prefetches                                      | 126 |

|   |     | 5.1.3    | Performing the Prefetch Memory Access                    | 130 |

|   |     | 5.1.4    | Hardware Modifications to Support Prefetching            | 138 |

|   | 5.2 | Achiev   | ving Larger Gains through Prefetching                    | 145 |

|   |     | 5.2.1    | Improving Analysis                                       | 146 |

|   |     | 5.2.2    | Improving Effectiveness                                  | 160 |

|   |     | 5.2.3    | Reducing Overheads                                       | 172 |

|   | 5.3 | Altern   | ative Latency-Hiding Techniques                          | 177 |

| Bil | Bibliography |         |                                   |     |  |

|-----|--------------|---------|-----------------------------------|-----|--|

|     | 6.1          | Future  | Work                              | 192 |  |

| 6   | Con          | clusion | S                                 | 191 |  |

|     | 5.4          | Chapter | r Summary                         | 189 |  |

|     |              | 5.3.3   | Multithreading                    | 183 |  |

|     |              | 5.3.2   | Relaxed Memory Consistency Models | 181 |  |

|     |              | 5.3.1   | Hardware-Controlled Prefetching   | 177 |  |

# **List of Tables**

| 1.1 | Techniques for coping with memory latency.                                       | 11  |

|-----|----------------------------------------------------------------------------------|-----|

| 2.1 | Hit rates of affine array accesses.                                              | 20  |

| 2.2 | Prefetch predicates for the different types of locality                          | 40  |

| 2.3 | Loop splitting transformations for the various types of locality                 | 43  |

| 2.4 | Order in which the optimization passes occur in the SUIF compiler, including     |     |

|     | prefetching.                                                                     | 51  |

| 3.1 | Description of uniprocessor applications.                                        | 56  |

| 3.2 | General statistics for the uniprocessor applications. Primary data cache miss    |     |

|     | counts are for an 8 Kbyte direct-mapped cache.                                   | 57  |

| 3.3 | Memory performance improvement for the selective prefetching algorithm           | 59  |

| 3.4 | Memory performance improvement for the indiscriminate and selective prefetch-    |     |

|     | ing algorithms.                                                                  | 62  |

| 3.5 | Ratio of prefetches issued under the indiscriminate and selective algorithms     | 64  |

| 3.6 | Average instruction overhead per prefetch.                                       | 65  |

| 3.7 | Average instruction overhead per prefetch of indirect reference                  | 79  |

| 4.1 | Latency for various memory system operations in processor clock cycles (1 pclock |     |

|     | = 30 ns)                                                                         | 92  |

| 4.2 | Description of multiprocessor applications.                                      | 92  |

| 4.3 | General statistics for the multiprocessor applications                           | 93  |

| 4.4 | Reduction in memory stall times for the multiprocessor applications              | 99  |

| 4.5 | Statistics on exclusive-mode prefetching.                                        | 107 |

| 5.1 | Average processor stall on a primary prefetch fill $(l_f)$ and the fraction of prefetches            |     |

|-----|------------------------------------------------------------------------------------------------------|-----|

|     | that suffer primary cache conflicts $\left(\frac{p_d}{p_t}\right)$ for each uniprocessor application | 134 |

| 5.2 | Distribution of where data was found both by prefetch and by subsequent refer-                       |     |

|     | ence. " $X \Rightarrow Y$ " means prefetch found data at $X$ , subsequent reference found data       |     |

|     | at Y, where $X,Y = C_1$ (primary cache), $C_2$ (secondary cache), and M (memory).                    | 135 |

| 5.3 | Statistics on multithreading behavior.                                                               | 186 |

# **List of Figures**

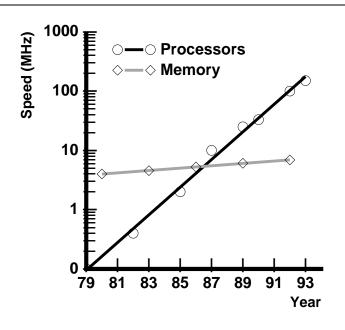

| 1.1  | Speed of commercial microprocessors and commodity DRAM over the past decade.        | 2  |

|------|-------------------------------------------------------------------------------------|----|

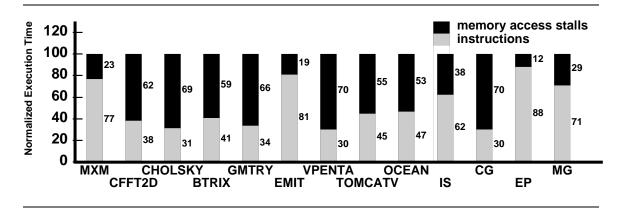

| 1.2  | Breakdown of execution of scientific and engineering codes on uniprocessor ar-      |    |

|      | chitecture                                                                          | 3  |

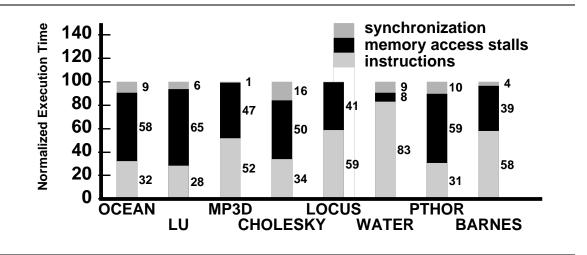

| 1.3  | Breakdown of execution of scientific and engineering codes on multiprocessor        |    |

|      | architecture                                                                        | 4  |

| 1.4  | Illustration of how prefetching improves performance                                | 7  |

| 1.5  | Illustration of how multithreading improves performance.                            | 10 |

| 2.1  | Data locality example.                                                              | 23 |

| 2.2  | Example of a more complicated access pattern that can be handled by reuse analysis. | 27 |

| 2.3  | Example of non-uniformly generated references.                                      | 29 |

| 2.4  | Example of uniformly generated references that do not have reuse                    | 29 |

| 2.5  | Example of references that access the same cache lines despite never accessing      |    |

|      | the same data items                                                                 | 30 |

| 2.6  | Example of how loop iteration counts and cache size affect locality                 | 32 |

| 2.7  | Algorithm for computing the localized iteration space. (Continued on next page.)    | 34 |

| 2.7  | Algorithm for computing the localized iteration space. (Continued from previous     |    |

|      | page.)                                                                              | 35 |

| 2.8  | Example of algorithm for estimating volume of data accessed by each loop            | 36 |

| 2.9  | Example of how symbolic values can be useful when computing volume of data          |    |

|      | accessed by each loop                                                               | 38 |

| 2.10 | Example of references with group reuse but not group locality.                      | 39 |

| 2.11 | Example of how prefetch predicates are constructed                                  | 41 |

| 2.12 | Generic schema for peeling a loop                                                   | 43 |

| 2.13 | Generic schema for unrolling a loop.                                                | 44 |

| 2.14 | Generic schema for strip-mining a loop.                                                                | 44 |

|------|--------------------------------------------------------------------------------------------------------|----|

| 2.15 | Algorithm for computing the shortest path through a loop body                                          | 46 |

| 2.16 | Example of how software pipelining is used to schedule prefetches the proper                           |    |

|      | amount of time in advance. For this example, assume that 5 iterations are enough                       |    |

|      | to hide memory latency                                                                                 | 47 |

| 2.17 | Example of selective prefetching algorithm. (Continued on next page.)                                  | 48 |

| 2.17 | Example of selective prefetching algorithm. (Continued from previous page.)                            | 49 |

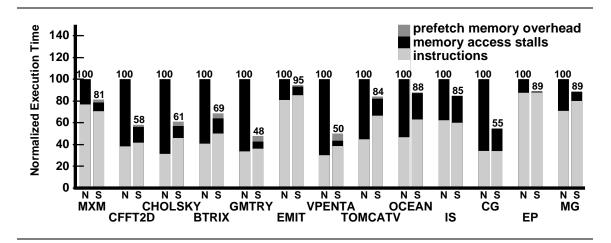

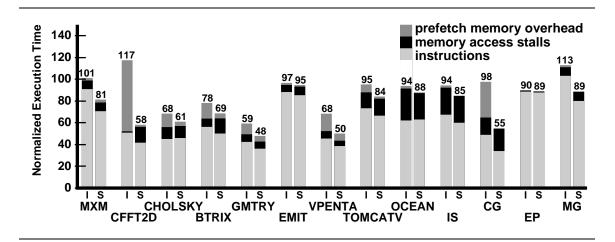

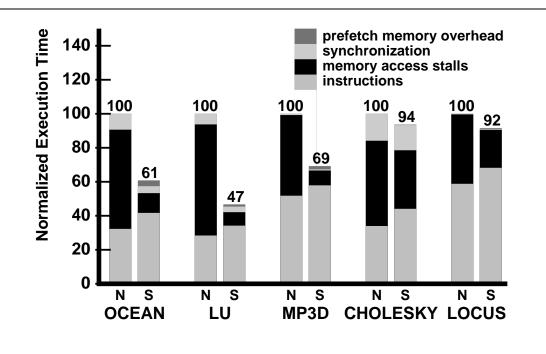

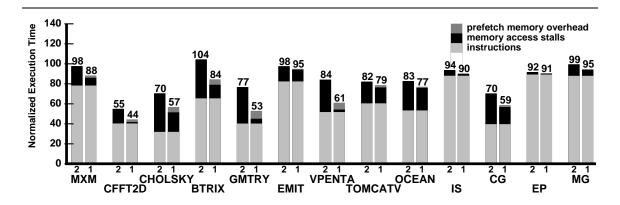

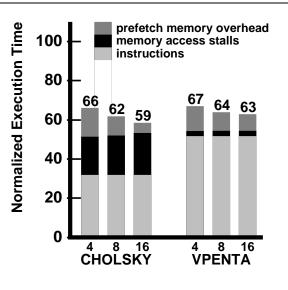

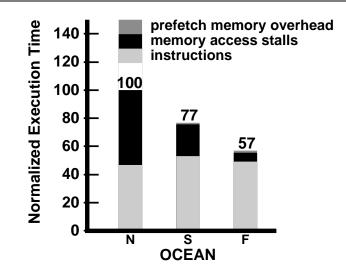

| 3.1  | Overall performance of the selective prefetching algorithm ( $N = no$ prefetching,                     |    |

|      | and $\mathbf{S}$ = selective prefetching).                                                             | 59 |

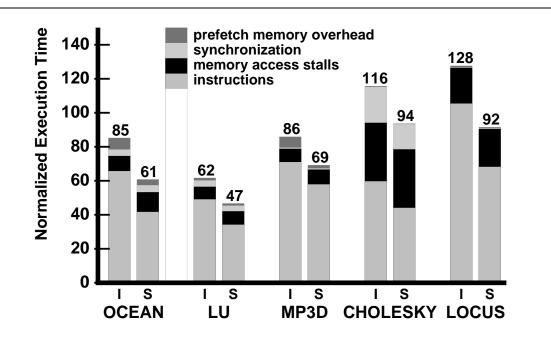

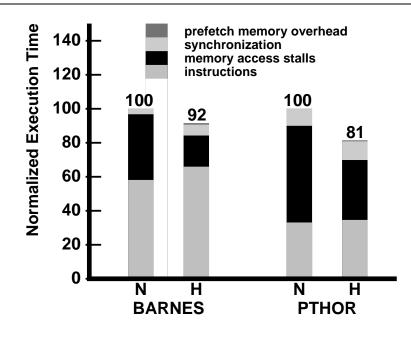

| 3.2  | Overall performance comparison between the indiscriminate and selective prefetch-                      |    |

|      | ing algorithms ( $\mathbf{I}$ = indiscriminate prefetching, and $\mathbf{S}$ = selective prefetching). | 61 |

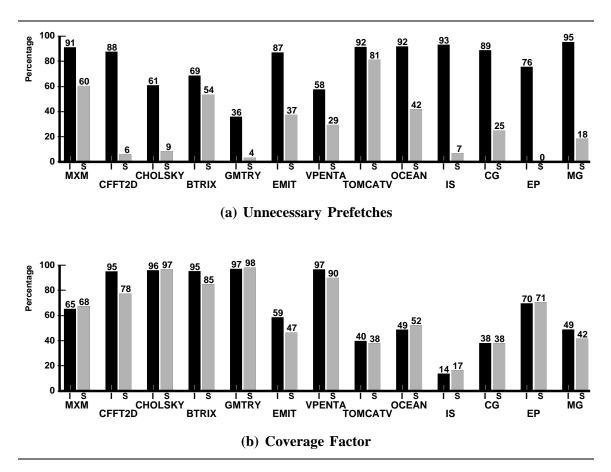

| 3.3  | Statistics for evaluating locality analysis for the uniprocessor applications ( $I =$                  |    |

|      | indiscriminate prefetching, and $\mathbf{S}$ = selective prefetching). Note that the unneces-          |    |

|      | sary prefetch percentages are computed with respect to the number of prefetches                        |    |

|      | issued, which changes between the two cases.                                                           | 63 |

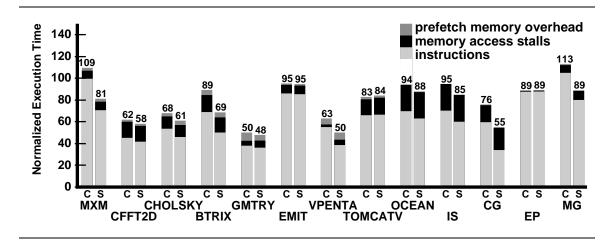

| 3.4  | Loop splitting effectiveness ( $N$ = no prefetching, $C$ = selective prefetching with                  |    |

|      | conditional statements, and $\mathbf{S}$ = selective prefetching with loop splitting)                  | 65 |

| 3.5  | Breakdown of the impact of prefetching on the original primary cache misses for                        |    |

|      | the uniprocessor applications.                                                                         | 67 |

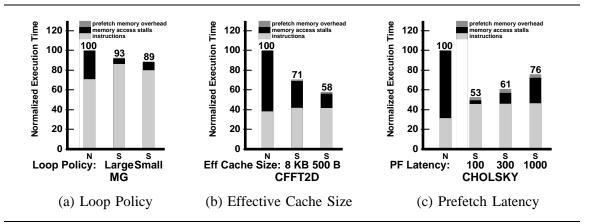

| 3.6  | Sensitivity of results to compile-time parameters ( $N = no$ prefetching, $S =$ selective              |    |

|      | prefetching variations).                                                                               | 69 |

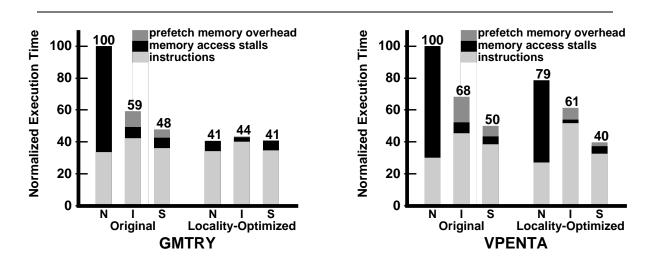

| 3.7  | Results with locality optimization ( $N$ = no prefetching, $I$ = indiscriminate prefetch-              |    |

|      | ing, and $S$ = selective prefetching)                                                                  | 72 |

| 3.8  | Example of an indirect array reference.                                                                | 74 |

| 3.9  | Example of how software pipelining is used to prefetch indirect references. For                        |    |

|      | this example, assume that 5 iterations are enough to hide memory latency                               | 76 |

| 3.10 | Example of how prefetching multiple levels of indirection may result in invalid                        |    |

|      | addresses and possibly a load exception. Assume that 5 iterations are sufficient                       |    |

|      | to hide memory latency.                                                                                | 77 |

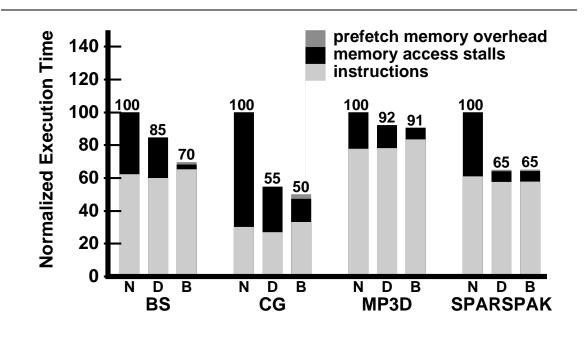

| 3.11 | Prefetching indirect references in the uniprocessor applications ( $N = no$ prefetch-                  |    |

|      | ing, $\mathbf{D}$ = dense-only prefetching, and $\mathbf{B}$ = both dense and indirect prefetching).   | 78 |

| 4.1  | Example of when a binding prefetch would be illegal.                                                   | 83 |

| 4.2  | Example of how coherence activity can cause cache misses                                                 | 85  |

|------|----------------------------------------------------------------------------------------------------------|-----|

| 4.3  | Example containing explicit synchronization.                                                             | 87  |

| 4.4  | Illustration of how exclusive-mode prefetching improves performance                                      | 89  |

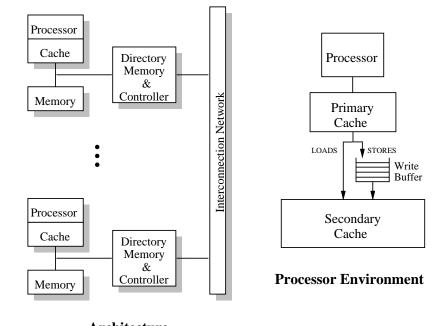

| 4.5  | Architecture and processor environment.                                                                  | 91  |

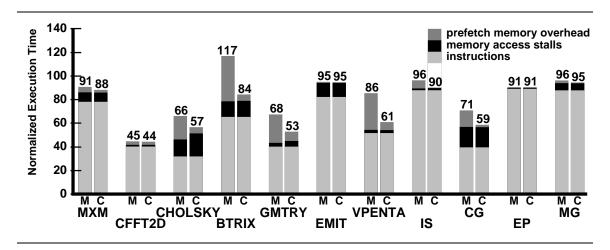

| 4.6  | Performance of multiprocessor applications without prefetching                                           | 97  |

| 4.7  | Overall performance of the selective prefetching algorithm for the multiprocessor                        |     |

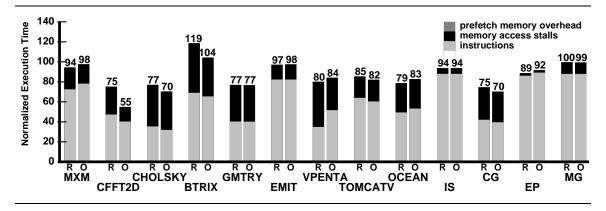

|      | applications (N = no prefetching, and S = selective prefetching)                                         | 98  |

| 4.8  | Overall performance comparison between the indiscriminate and selective prefetch-                        |     |

|      | ing algorithms for the multiprocessor applications ( $\mathbf{I}$ = indiscriminate prefetching,          |     |

|      | and $\mathbf{S}$ = selective prefetching)                                                                | 100 |

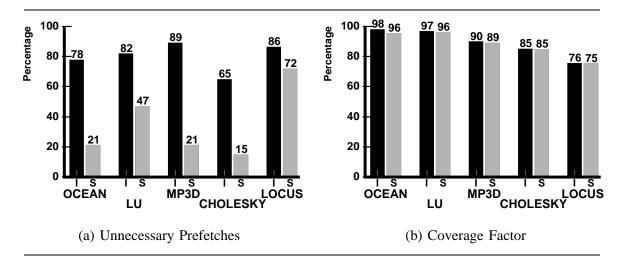

| 4.9  | Statistics for evaluating locality analysis for multiprocessor applications ( $I = in$ -                 |     |

|      | discriminate prefetching, and $\mathbf{S}$ = selective prefetching)                                      | 101 |

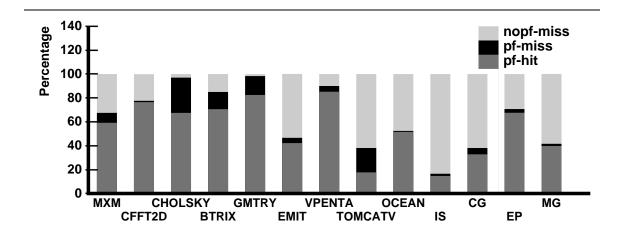

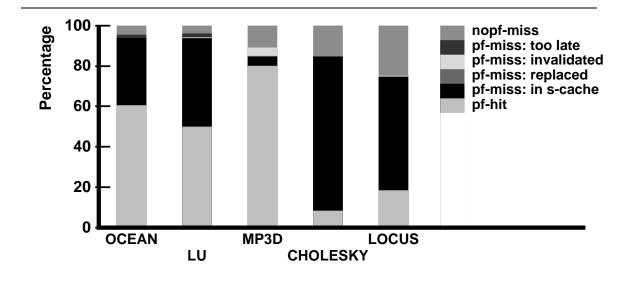

| 4.10 | Breakdown of the impact of prefetching on the original primary cache misses for                          |     |

|      | the multiprocessor applications.                                                                         | 103 |

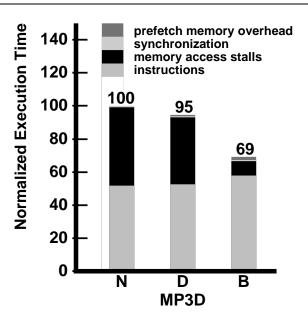

| 4.11 | Prefetching indirect references in the multiprocessor version of MP3D ( $N = no$                         |     |

|      | prefetching, $\mathbf{D}$ = dense-only prefetching, and $\mathbf{B}$ = both dense and indirect prefetch- |     |

|      | ing)                                                                                                     | 106 |

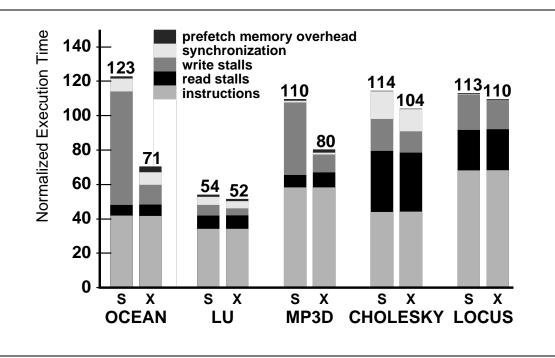

| 4.12 | Performance with and without exclusive-mode prefetching given sequential con-                            |     |

|      | sistency rather than release consistency ( $\mathbf{S}$ = shared-mode prefetching only, $\mathbf{X}$     |     |

|      | = exclusive-mode prefetching available). Performance is normalized to release                            |     |

|      | consistency without prefetching                                                                          | 108 |

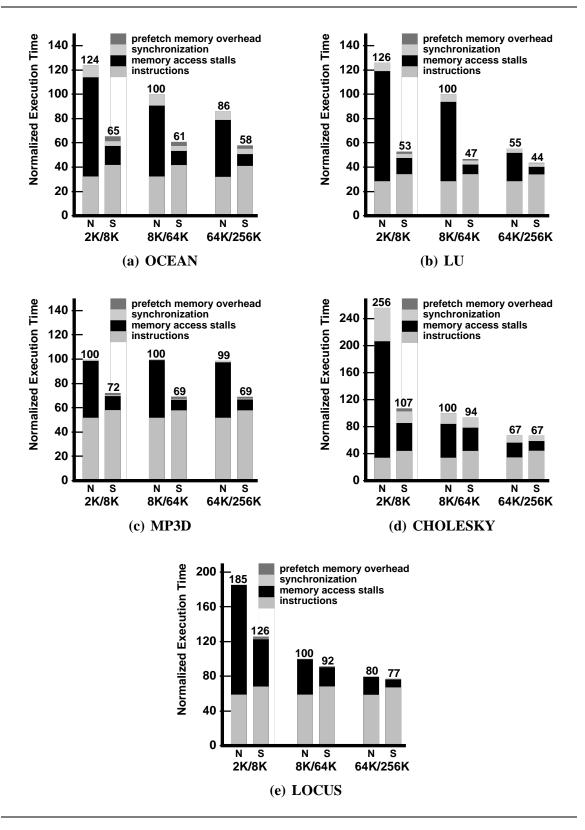

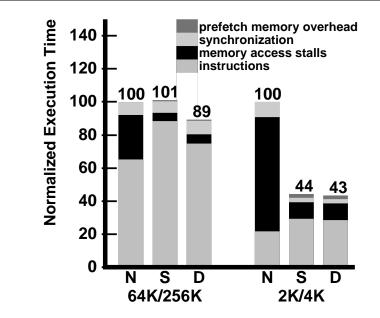

| 4.13 | Performance of multiprocessor applications with varying cache sizes ( $N = no$                           |     |

|      | prefetching, and $S$ = selective prefetching)                                                            | 110 |

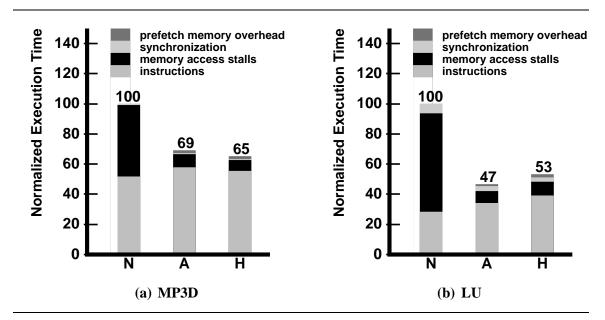

| 4.14 | Comparison of compiler-based and hand-inserted prefetching for the cases where                           |     |

|      | the compiler succeeded ( $\mathbf{N}$ = no prefetching, $\mathbf{A}$ = prefetches inserted automatically |     |

|      | by compiler, $\mathbf{H}$ = hand-inserted prefetching)                                                   | 114 |

| 4.15 | Cases where the compiler failed to improve prefetching ( $N = no$ prefetching, $H$                       |     |

|      | = hand-inserted prefetching).                                                                            | 117 |

| 5.1  | Format of prefetch instructions, using "base-plus-offset" addressing mode                                | 123 |

| 5.2  | Example of how prefetches can reuse load/store base registers (in this case $r7$ ).                      | 124 |

| 5.3  | Possible encoding of prefetch instruction.                                                               | 125 |

| 5.4  | Dropping vs. stalling on full prefetch issue buffer ( $\mathbf{D} = drop, \mathbf{S} = stall$ )          | 128 |

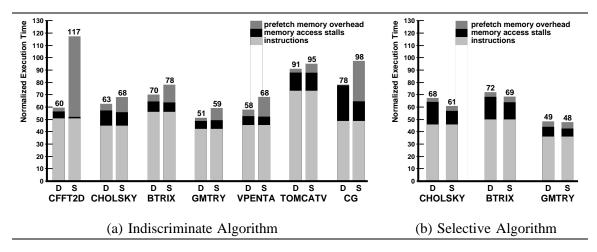

| 5.5  | Performance when prefetches do not check either caches before going to memory                           |        |

|------|---------------------------------------------------------------------------------------------------------|--------|

|      | $(\mathbf{M} = \text{go straight to memory, } \mathbf{C} = \text{check caches}).$                       | 130    |

| 5.6  | Performance when prefetching into the primary cache (1) versus prefetching only                         |        |

|      | into the secondary cache (2)                                                                            | 134    |

| 5.7  | Performance when prefetching into the secondary cache, both when compiled for                           |        |

|      | the primary cache size $(\mathbf{O})$ , and when recompiled for the secondary cache size $(\mathbf{R})$ | ).136  |

| 5.8  | Prefetch issue buffer in the uniprocessor architecture. Note that for prefetches,                       |        |

|      | the fetched data goes directly into the cache, rather than being held in an MSHR.                       |        |

|      | Therefore an MSHR is simply a resource for <i>controlling</i> an outstanding miss                       |        |

|      | under this model.                                                                                       | 141    |

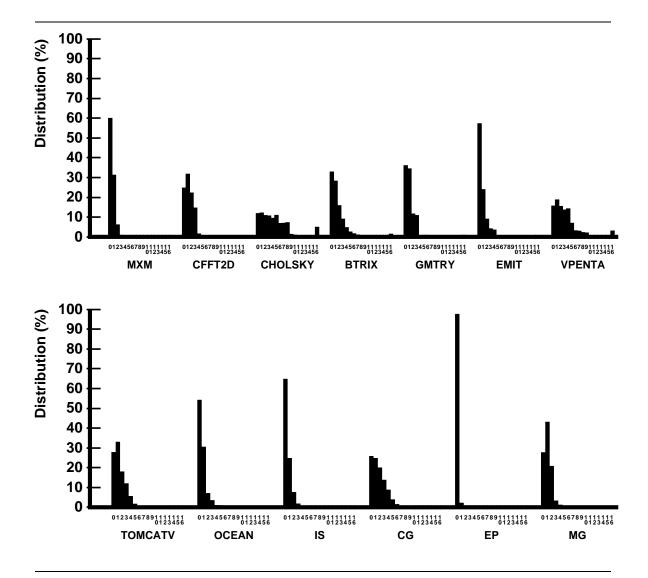

| 5.9  | Distribution of previously outstanding prefetch misses upon each prefetch miss for                      |        |

|      | the original uniprocessor architecture (which supports up to seventeen outstanding                      |        |

|      | misses).                                                                                                | 142    |

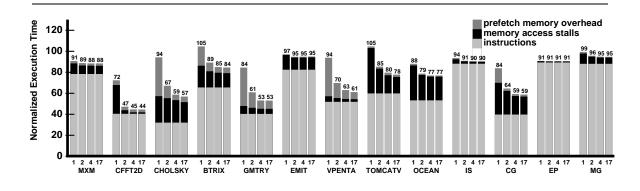

| 5.10 | Performance when the number of MSHRs is varied.                                                         | 143    |

| 5.11 | Performance when the size of the prefetch issue buffer size is varied between                           |        |

|      | four, eight, and sixteen entries, given four MSHRs.                                                     | 144    |

| 5.12 | Example of why intrinsic data reuse matters when scheduling prefetches even                             |        |

|      | when miss rates are precisely known.                                                                    | 149    |

| 5.13 | Results using feedback ( $N$ = no prefetching, $S$ = prefetching with static analysis                   |        |

|      | only, $\mathbf{F}$ = prefetching with feedback)                                                         | 151    |

| 5.14 | Example of adapting at runtime by checking problem size                                                 | 153    |

| 5.15 | Example of adapting at runtime by checking for data alignment conflicts                                 | 154    |

| 5.16 | Example of adapting at runtime by checking hardware miss counters                                       | 155    |

| 5.17 | Example of adapting at runtime to temporal locality along an outer loop by check-                       |        |

|      | ing hardware miss counters.                                                                             | 157    |

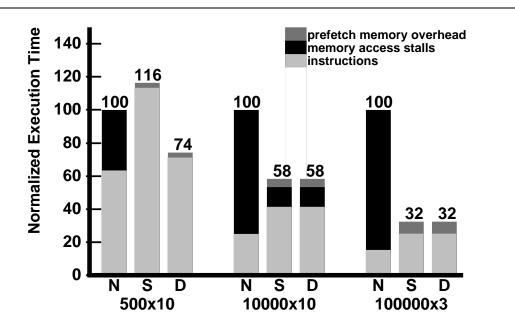

| 5.18 | Results with adaptive version of BCOPY ( $N = no$ prefetching, $S =$ statically                         |        |

|      | prefetch all the time, $\mathbf{D}$ = adapt prefetching dynamically). " <b>BxT</b> " means the          |        |

|      | same <b>B</b> -byte block is copied to the same destination <b>T</b> times. Performance is              |        |

|      | renormalized for each case.                                                                             | 158    |

| 5.19 | Results with adaptive version of LU ( $N$ = no prefetching, $S$ = statically prefetch                   |        |

|      | all the time, $\mathbf{D}$ = adapt prefetching dynamically). Performance is re-normalized               |        |

|      | for each cache size.                                                                                    | 159    |

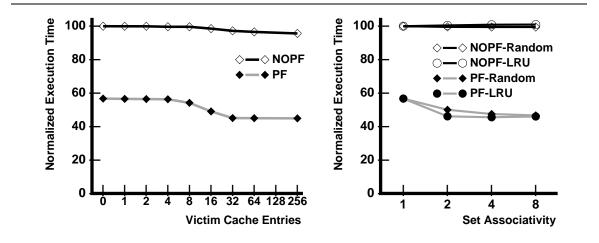

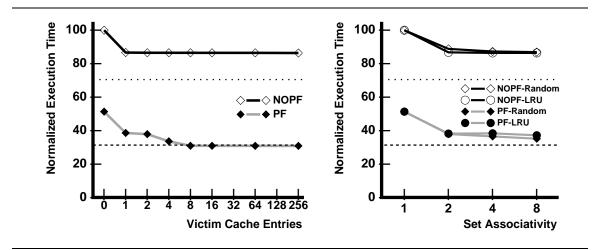

| 5.20 | Performance of CHOLSKY with victim caches and set-associative primary cache                             | s. 163 |

| 5.21 | Loop that suffers cache conflicts in CHOLSKY.                                          | 163 |

|------|----------------------------------------------------------------------------------------|-----|

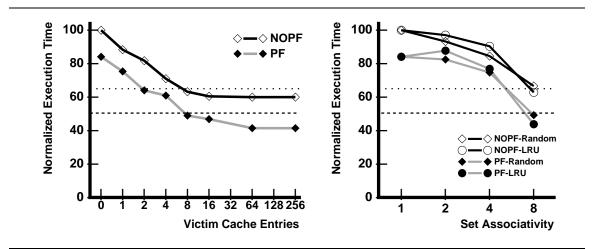

| 5.22 | Performance of the original TOMCATV code with victim caches and set-associative        |     |

|      | primary caches. The performance of TOMCATV on the original direct-mapped ar-           |     |

|      | chitecture after arrays are manually realigned is shown by the dotted (no prefetch-    |     |

|      | ing) and dashed (with prefetching) horizontal lines.                                   | 164 |

| 5.23 | Performance of the realigned version of TOMCATV with victim caches and set-            |     |

|      | associative primary caches. Note that performance is normalized to the speed of        |     |

|      | this realigned code.                                                                   | 164 |

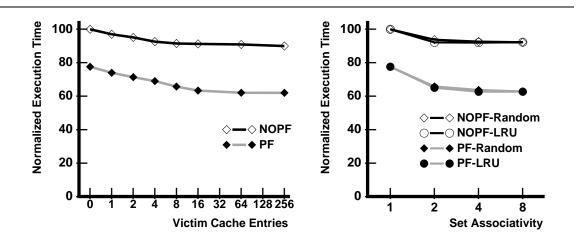

| 5.24 | Performance of the original MXM code with victim caches and set-associative            |     |

|      | primary caches. The performance of MXM on the original direct-mapped archi-            |     |

|      | tecture after arrays are manually realigned is shown by the dotted (no prefetching)    |     |

|      | and dashed (with prefetching) horizontal lines.                                        | 166 |

| 5.25 | Loop that suffers cache conflicts in MXM                                               | 166 |

| 5.26 | Performance of the original CFFT2D code with victim caches and set-associative         |     |

|      | primary caches. The performance of CFFT2D on the original direct-mapped archi-         |     |

|      | tecture after arrays are manually realigned is shown by the dotted (no prefetching)    |     |

|      | and dashed (with prefetching) horizontal lines.                                        | 167 |

| 5.27 | Loops that suffer cache conflicts in CFFT2D                                            | 167 |

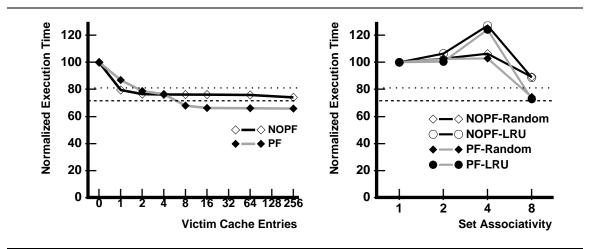

| 5.28 | Performance of the original VPENTA code with victim caches and set-associative         |     |

|      | primary caches. The performance of VPENTA on the original direct-mapped ar-            |     |

|      | chitecture after arrays are manually realigned is shown by the dotted (no prefetch-    |     |

|      | ing) and dashed (with prefetching) horizontal lines.                                   | 169 |

| 5.29 | Loop that suffers cache conflicts in VPENTA.                                           | 169 |

| 5.30 | Example where it is not clear whether to use uncached prefetches                       | 171 |

| 5.31 | Example of how instruction overhead can be eliminated by issuing large block           |     |

|      | prefetches outside the main loop                                                       | 176 |

| 5.32 | Example where imperfect branch prediction makes it difficult to look far enough        |     |

|      | ahead in the instruction stream.                                                       | 180 |

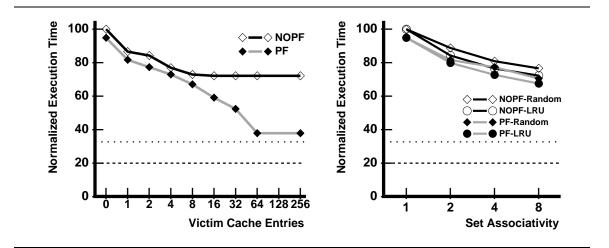

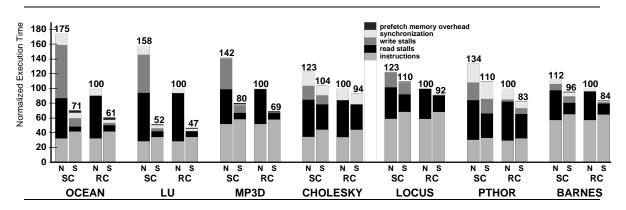

| 5.33 | Performance with sequential consistency (SC) versus release consistency (RC),          |     |

|      | normalized to RC without prefetching ( $N = no$ prefetching, $S =$ selective prefetch- |     |

|      | ing)                                                                                   | 182 |

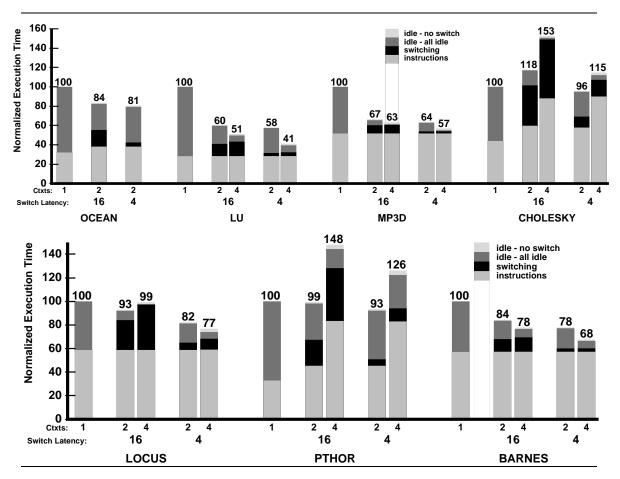

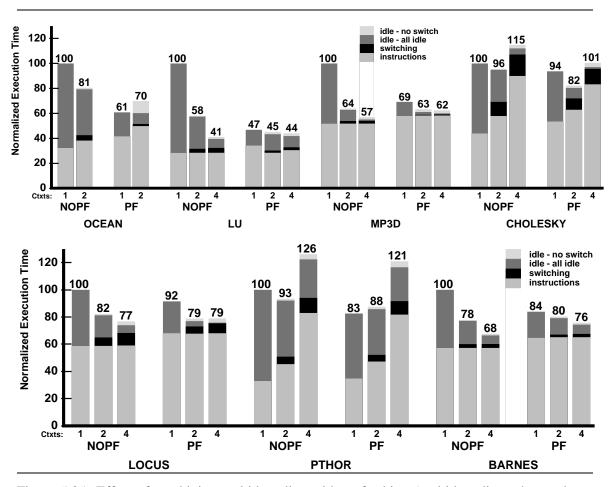

| 5.34 | Performance of multithreading with 1, 2 and 4 contexts and switch latencies of 4       |     |

|      | and 16 cycles.                                                                         | 185 |

|      |                                                                                        |     |

| 5.35 | Effect of combining multithreading with prefetching (multithreading schemes have |     |

|------|----------------------------------------------------------------------------------|-----|

|      | a 4-cycle switch latency).                                                       | 188 |

### Chapter 1

## Introduction

Microprocessor-based systems are increasingly becoming the workhorse for all scientific and engineering computation. With numerical processing capabilities that already rival older generations of supercomputers, the microprocessors used in these systems will continue to improve dramatically due to every-increasing clock rates and the exploitation of instruction-level parallelism. In contrast to the vector-based machines that have long dominated high-performance computing, these new scalar systems are considerably more cost-effective since they contain commercial microprocessors that are mass-produced for the large general-purpose computing market. In addition, these commodity microprocessors can be used to build large-scale multiprocessors capable of aggregate peak rates surpassing that of current vector machines.

Unfortunately, a high computation bandwidth is meaningless unless it is matched by a similarly powerful memory subsystem. Although microprocessor speeds have been increasing dramatically, the speed of memory has not kept pace. As illustrated in Figure 1.1, the speed of commercial microprocessors has been doubling roughly every three years, while the speed of commodity DRAM has improved by little more than 50% over the past decade. Part of the reason for this is that there is a direct tradeoff between capacity and speed, and the highest priority in improving DRAM has been increasing capacity. The result is that from the perspective of the processor, memory is getting slower at a dramatic rate. This will affect *all* computer systems, making it increasingly difficult to achieve high processor efficiencies. The latency problem is magnified in large-scale multiprocessors, where sheer physical dimensions result in large latencies to remote memory locations.

To deal with memory latency, most computer systems today rely on their cache hierarchy to reduce the effective memory access time. While the effectiveness of caches has been well

Figure 1.1: Speed of commercial microprocessors and commodity DRAM over the past decade.

established for general-purpose code, their effectiveness for scientific and engineering applications has not. One manifestation of this is that several of the scalar machines designed for scientific computation did not use caches [14, 16].

This thesis investigates a technique called *software-controlled prefetching* which mitigates the impact of long cache miss penalties, thereby helping to unlock the full potential of microprocessorbased systems. The remainder of this chapter provides further motivation for improving cache performance, discusses software-controlled prefetching in light of other techniques for coping with memory latency, presents our research goals, and summarizes related work. We conclude this chapter with a list of the major contributions of this thesis and an overview of the remaining chapters.

#### 1.1 Cache Performance on Scientific and Engineering Codes

To illustrate the need for improving the cache performance of microprocessor-based uniprocessor and multiprocessor systems, we present results in this subsection for a set of scientific and engineering applications. We begin with the uniprocessor architecture. For the sake of concreteness,

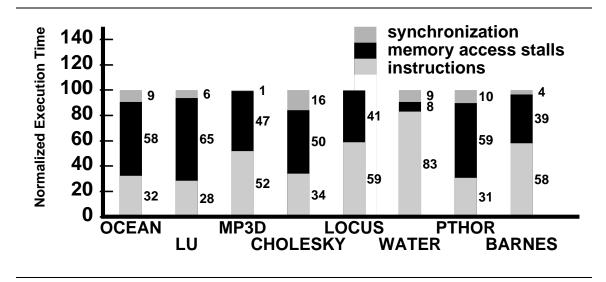

Figure 1.2: Breakdown of execution of scientific and engineering codes on uniprocessor architecture.

we pattern our memory subsystem after a typical MIPS R4000-based workstation. The architecture consists of a single-issue processor running at a 100 MHz internal clock. The processor has an on-chip primary data cache of 8 Kbytes, and a secondary cache of 256 Kbytes. Both caches are direct-mapped and use 32 byte lines. The penalty of a primary cache miss that hits in the secondary cache is 12 cycles, and the total penalty of a miss that goes all the way to main memory is 75 cycles. In this simple model, we assume that all instructions execute in a single cycle and that all instructions hit in the primary instruction cache. The performance of the benchmarks was simulated by instrumenting the MIPS object code using *pixie* [74] and piping the resulting trace into our detailed cache simulator.

Figure 1.2 breaks down the total program execution time into instruction execution and stalls due to memory accesses for 13 uniprocessor programs taken from the SPEC [77], SPLASH [72], and NAS Parallel [8] benchmark suites. Many of the programs spend a significant amount of time on memory accesses. In fact, 8 out of the 13 programs spend more than half of their time stalled for memory accesses.

We conducted a similar experiment to evaluate the impact of memory latency on large-scale shared-memory multiprocessors by simulating the entire SPLASH [72] parallel application suite on an architecture resembling the Stanford DASH multiprocessor [54]. The architecture we model includes 16 R3000 processors running at 33 MHz, two-level cache hierarchies (64 Kbytes/256 Kbytes), and a low-latency interconnection network. Miss latencies for loads range from 15 cycles to the secondary cache to over 130 cycles for "remote dirty" lines. Further details on this architecture and the parallel applications will be presented later in Chapter 4. Figure 1.3 shows the results. Execution time is now broken into three categories: time spent executing instructions,

Figure 1.3: Breakdown of execution of scientific and engineering codes on multiprocessor architecture.

time spent stalled for memory, and time spent stalled for synchronization (such as locks and barriers). Once again, memory stalls are significant, with 7 of the 8 applications spending more than 35% of their time stalled waiting for memory accesses to complete.

#### **1.2 Coping with Memory Latency**

To reclaim some of the lost performance potential illustrated in Figures 1.2 and 1.3, techniques for coping with memory latency are essential. These techniques fall broadly into two categories: those that *reduce* latency, and those that *tolerate* latency. Techniques for reducing latency include caching data and making the best use of those caches through locality optimizations. Techniques for tolerating latency include buffering and pipelining references, prefetching, and multithreading. We will briefly discuss each of these techniques in this subsection to show how prefetching fits into the overall approach to hiding latency, and to motivate why prefetching itself is worth studying.

#### 1.2.1 Caches

Caches are a critical first step toward coping with memory latency, but are not a panacea, as we saw already in Figures 1.2 and 1.3. Caches reduce latency from a memory access to a cache access whenever data items are found in the cache. The likelihood of finding data in the cache depends not only on the size and organization of the cache, but also on the inherent *locality of reference* within the application. Locality can occur in both time and space: *temporal locality* is the tendency for a recently-accessed item to be accessed again soon, and *spatial locality* is the tendency for items *near* a recently-accessed item to be accessed soon. Since most applications exhibit a reasonable amount of locality, caches are generally quite useful. As a result, most commercial RISC microprocessors provide support for cache hierarchies, including on-chip primary instruction and data caches. The benefits of caches in multiprocessors have also been recognized, where despite the complication of keeping shared writable data *coherent* [6], a number of multiprocessors with caches have been implemented [3, 41, 47, 55]. Therefore caches are an integral part of the memory latency solution, and the remaining techniques we discuss build upon caching as a foundation.

#### **1.2.2 Locality Optimizations**

Locality optimizations attempt to make caches more effective by restructuring computation to enhance data locality. One important example of a locality-improving transformation is *blocking* (also known as *tiling*) [1, 22, 23, 30, 60, 64, 87], which works as follows. Rather than operating on entire rows or columns of an array, blocked algorithms operate on submatrices or *blocks*, so that data loaded into the faster levels of the memory hierarchy are reused. Other useful transformations include unimodular loop transforms such as interchange, skewing and reversal [87]. Since these optimizations improve the code's data locality, they not only reduce the effective memory access time but also reduce the memory bandwidth requirement.

For multiprocessors, the concept of data locality can be extended to minimize not only accesses to main memory, but also communication between processors. This involves both the placement of data in processors' local memories (known as *data decomposition*) and the mapping of the computation onto the processors of the parallel machine (known as *computation decomposition*). The most popular approach to this complex optimization problem is for the programmer to explicitly specify the data decomposition through directives in the programming language [11, 38, 43, 67, 78, 82, 88], while the compiler is responsible for decomposing the computation. Another approach is for the compiler to determine both the data and computation decompositions [4, 5, 10, 12, 34, 35, 56].

While locality optimizations are quite useful when they work, their applicability is somewhat limited because not only must there be a better way to structure the code (which is not always the case), but it also must be *legal* to do so. Whenever dependence analysis [58] is inexact,

the compiler usually has to be conservative and assume that dependencies could be violated if the code was restructured. In practice, this means that these types of optimizations are not frequently applicable (as we will observe later in Section 3.4). Therefore to cope with whatever latency cannot be reduced through caching and locality optimizations, we consider techniques for *tolerating* memory latency.

#### **1.2.3 Buffering and Pipelining References**

One way to tolerate memory latency is to allow references to be *buffered* and *pipelined*. In current uniprocessor systems, this technique is typically applied only to writes in the form of *write buffers*. Write buffers exploit the fact that a processor does not have to wait for a write to complete as long as it properly observes the effect of the written data in the future. Therefore the processor can perform a write by simply issuing it to the write buffer, provided that future reads check the write buffer for matching addresses. The advantage of a write buffer is not only that the processor does not stall when executing a write, but also that multiple writes can be overlapped to exploit pipelining.

Buffering read accesses is more difficult because unlike writes, the processor typically cannot proceed until the read access completes, since it needs the data that is being read. With *non-blocking loads* and a *lockup-free cache* [45], it is possible to buffer and pipeline reads. A non-blocking load means that rather than stalling at the time the load is performed, the processor postpones stalling until the data is actually used. A lockup-free cache permits multiple outstanding cache misses. By combining the two, it would be possible to buffer multiple reads, and to pipeline their accesses. However, very few commercial microprocessors currently support non-blocking loads due to the complexity involved, and in practice the use of a load value typically occurs shortly after the load is performed. Therefore tolerating read latency through buffering and pipelining is not especially promising.

Buffering and pipelining accesses in a multiprocessor is complicated by the restrictions placed on the causality of accesses in different processors. In the strictest case, known as *sequential* or *strong* consistency [50], all accesses to shared data must appear as though the different processes were interleaved on a sequential machine. While conceptually intuitive and elegant, sequential consistency imposes severe restrictions on the outstanding accesses that a process may have, thus restricting the buffering and pipelining allowed. In contrast, *relaxed consistency models* [2, 18, 26, 27] permit accesses to be buffered and pipelined, provided that explicit synchronization events are identified and ordered properly. Once again, however, the main benefit of these relaxed Figure 1.4: Illustration of how prefetching improves performance.

consistency models is hiding write latency [26]. To address read latency effectively, we must look beyond buffering and pipelining.

#### 1.2.4 Prefetching

The two main techniques for tolerating read latency as well as write latency are *prefetching* and *multithreading*. The key to tolerating read latency is to split apart the *request* for data and the *use* of that data, while finding enough *parallelism* to keep the processor busy in between. The distinction between prefetching and multithreading is that prefetching finds the parallelism within a *single thread* of execution, while multithreading exploits parallelism across *multiple threads*. To hide the latency within a single thread, the request for the data (i.e. the prefetch request) must be moved back sufficiently far in advance of the use of the data in the execution stream. This effectively requires the ability to *predict* what data is needed ahead of time. In contrast, the multithreading approach splits read transactions by swapping out the currently executing thread when it suffers a cache miss, executing other concurrent threads for the duration of the miss to keep the processor busy, and finally resuming the initial thread once the memory access completes. Prefetching will be discussed in this section, while multithreading will be discussed in more detail in Section 1.2.5.

Figure 1.4 is a simple illustration of how prefetching improves performance. In the case

without prefetching (shown on the left), the processor stalls when it attempts to load two locations (A and B) that are not present in the cache. If prefetches for A and B can be issued far enough in advance in the instruction stream (as shown on the right), then the memory accesses for both locations will have completed before the loads are executed, and hence the processor will not stall. The key observation here is that prefetching not only allows memory accesses to be overlapped with computation, but it also allows memory accesses to be overlapped with other memory accesses (i.e. the accesses can be pipelined).

Prefetches on a scalar machine are analogous to vector memory accesses on a vector machine. In both cases, memory accesses are overlapped with computation and other accesses. Furthermore, similar to vector registers, prefetching allows caches in scalar machines to be managed by software. A major difference is that while vector machines can only operate on vectors in a pipelined manner, scalar machines can execute arbitrary sets of scalar operations well.

Prefetching can occur in many different forms. One common type of prefetching occurs whenever cache lines are longer than a single word. In these cases, additional words are brought into the cache on each cache miss. This is most useful when there is abundant spatial locality, such as when iterating across an array in a unit-stride manner. However, increasing the cache line size is not the most effective form of prefetching, since memory bandwidth is wasted whenever useless data is brought into the cache [64]. In addition, long cache lines can aggravate miss rates in shared-memory multiprocessors by causing unnecessary amounts of *false sharing* [19, 81]. As we have seen already in Figures 1.2 and 1.3, a significant amount of latency remains despite the prefetching benefit of multi-word cache lines.

Another form of prefetching could occur with *non-blocking loads* [66]. With a non-blocking load, rather than stalling when the load is executed, any stalls are postponed until the load result is actually needed. So one could imagine that if the loads could be moved far enough in advance of the uses of data, then prefetching could be implemented in this manner. However, there are two important limitations on how far loads can be moved ahead of their uses. First, there is the problem of running out of registers. If the compiler attempts to extend register lifetimes to hundreds of cycles, it will run out of registers very quickly. Second, there is the problem of maintaining program correctness. For example, a load cannot be moved ahead of a store unless it is certain that they are to different locations. Since memory disambiguation is a difficult problem for the compiler to solve (particularly in codes with indirect references), this is likely to be a serious limitation.

Some elaborate prefetching schemes that are strictly hardware-based have also been proposed.

We will discuss those schemes only briefly now, and will examine them in greater detail later in Section 5.3.1. Perhaps the most sophisticated of these techniques is the one proposed by Baer and Chen [7]. With this scheme, the processor maintains a history table to keep track of the types of reference patterns it is seeing. If it detects a pattern of constant-stride access behavior for a particular instruction, it will attempt to prefetch ahead for that reference in the future. This prefetching occurs through a "lookahead PC", which walks ahead of the actual PC using branch prediction. The lookahead PC is used to look up these future instructions in the history table to see whether they should be prefetched. Another scheme proposed by Lee [53] attempted to decode future instructions using a lookahead buffer to detect memory references. One advantage of strictly hardware-based schemes is that they do not incur any instruction overhead, unlike software-controlled prefetching (which we will discuss next). However, their disadvantages include the fact that they are limited to prefetching constant-stride accesses, they are limited by branch prediction (which is less than perfect), and they may entail a significant hardware cost.

Finally, with software-controlled prefetching, explicit prefetch instructions are executed by the processor to move data into the cache. The format of these instructions resembles a normal load instruction, but without a register specifier (since the data is only placed in the cache). Prefetch instructions also differ from normal load instructions in that they are non-blocking and they do not take memory exceptions. The non-blocking aspect allows them to be overlapped with computation, and the fact that they do not take exceptions is useful because it permits more speculative prefetching strategies (e.g., dereferencing pointers before it is certain that they point to legal addresses). The challenges of software-controlled prefetching include the fact that some sophistication is needed to insert the prefetches into the code, and also that the new prefetch instructions will involve some amount of execution overhead. The advantages of software-controlled prefetching are that only a small amount of hardware support is necessary, and a broader class of reference patterns can be covered than simply constant stride accesses (e.g., indirect references, such as in sparse-matrix code).

#### 1.2.5 Multithreading

Figure 1.5 illustrates how multithreading (also known as "multiple-context processing") can also be used to tolerate latency [3, 36, 44, 85]. In this figure, context #1 suffers a cache miss when it attempts to load location A. At this time, context #1 is swapped out and the processor begins to execute context #2. Hopefully by the time context #2 needs to be swapped out (which occurs

Figure 1.5: Illustration of how multithreading improves performance.

when it suffers a cache miss trying to load location B), the memory access for the original context has completed, and therefore context #1 is ready to run again.

Multithreading has two advantages over software-controlled prefetching. First, it can handle arbitrarily complicated access patterns, including situations where it is impossible to predict the addresses ahead of time (and therefore prefetching will not work). Second, since it does not require any software support, it can improve the speed of existing executables without recompilation.

However, multithreading has several disadvantages relative to software-controlled prefetching. First of all, to make a single application execute faster, additional concurrent threads of execution are needed. This concurrency may or may not exist. Particularly in a uniprocessor environment, it is unlikely that a programmer would go through the pain of parallelizing their application for the sake of multithreading. A second limitation is the overhead of switching between contexts. Such overhead occurs because: (i) data cache misses are detected late in the pipeline, and subsequent instructions that have entered the pipe must be flushed; and (ii) saving and restoring context state (e.g., the register file) may take additional time. These switching overheads can potentially offset much of the performance gain of multithreading. Finally, to minimize the context switching overhead, a significant amount of hardware is required (e.g., replicated register files). Therefore multithreading is clearly a more expensive solution than prefetching, both in terms of concurrency demands and hardware support.

| Technique      | Benefit       | Exploits         | Hardware Support              | Software Support  |

|----------------|---------------|------------------|-------------------------------|-------------------|

| Caching        | Reduces       | Locality of      | Caches <sup>1</sup>           | None              |

|                | Latency       | Reference        |                               |                   |

| Locality       | Reduces       | Reordering       |                               | Locality-         |

| Optimizations  | Latency       | Computation to   | Caches                        | Enhancing         |

|                |               | Enhance Locality |                               | Transformations   |

| Buffering and  | Tolerates     | Writes Can Occur | Lockup-free                   | None <sup>3</sup> |

| Pipelining     | Write Latency | Out-of-Order     | Caches <sup>2</sup>           |                   |

| Software-      | Tolerates     | Parallelism      | Lockup-free                   | Insert            |

| Controlled     | Read and      | within a         | Caches, Prefetch              | Prefetches        |

| Prefetching    | Write Latency | Single Thread    | Instruction                   |                   |

|                | Tolerates     | Parellelism      | Lockup-free                   |                   |

| Multithreading | Read and      | across           | Caches, Thread                | None              |

|                | Write Latency | Multiple Threads | Control Logic,                |                   |

|                |               |                  | Replicated State <sup>4</sup> |                   |

Table 1.1: Techniques for coping with memory latency.

#### **1.2.6 Overall Approach**

We now focus on how each of these techniques, particularly prefetching, fits into the "big picture" of coping with memory latency. As a quick summary, Table 1.1 presents the benefits and requirements of each technique. Given these techniques, we would like to apply them in the following order.

First, the latency should be *reduced* as much as possible, through caching and locality optimizations. Reducing latency is preferable over tolerating latency since it actually reduces the demand for main memory bandwidth, which can be crucial. Caches provide the foundation for all of these latency-hiding techniques, and locality optimizations are also attractive since they require no additional hardware support.

After reducing latency, we then want to *tolerate* any remaining latency, starting with the least expensive techniques before resorting to more costly techniques. The first step is buffering and pipelining accesses, which is an effective means of hiding write latency and requires only a lockup-free cache—a requirement common to all latency-tolerating techniques. To address read latency as well, the choices are either prefetching or multithreading. Software-controlled prefetching

<sup>&</sup>lt;sup>1</sup>Hardware to support coherency mechanism is also needed for multiprocessors.

<sup>&</sup>lt;sup>2</sup>Lockup-free caches permit both buffering and pipelining. For buffering alone, write buffers are sufficient.

<sup>&</sup>lt;sup>3</sup>Explicit synchronization must be identified for multiprocessors.

<sup>&</sup>lt;sup>4</sup>The replicated thread state may include replicated register files.

appears to be the more desirable solution since it requires significantly less hardware support than either hardware-controlled prefetching or multithreading, and perhaps more importantly it can speed up the performance of a *single* thread of execution, rather than requiring multiple concurrent threads as in the case of multithreading. If software-controlled prefetching cannot effectively hide read latency, the final step would be multithreading.

Thus the open question of just how effective software-controlled prefetching can be in practice is a key factor in deciding whether processor architectures should support prefetching, multithreading, or both. Addressing this open question is one of the goals of this dissertation, as we discuss further in the next section.

#### **1.3 Research Goals**

This section discusses the research goals of this dissertation. At the highest level, our goal is to evaluate and improve upon the latency-hiding benefits of software-controlled prefetching. We focus specifically on *compiler-inserted* prefetching, since this is obviously preferable to placing the burden of prefetch insertion on the programmer. Since we are interested in practical results rather than theoretical limits, we implement our prefetching algorithms in a state-of-the-art compiler to measure the actual performance of working codes with prefetching. The goals of the compiler algorithm itself are described below.

A key goal for any compiler-based prefetching algorithm is the ability to cover a wide range of programs (e.g., dense-matrix codes, sparse-matrix codes, irregular general-purpose codes, etc.). Ideally, any application suffering from memory latency could benefit from prefetching. However, covering all types of applications and access patterns is an overly-ambitious goal, and therefore we must limit our scope to make substantial headway. Our approach is to start with an important class of applications and handle them well, and then later build upon this core algorithm to cover other important cases. The access pattern we start with is array references where the array indices are *affine* (i.e. linear) functions of surrounding loop indices; such access patterns occur in many types of applications, particularly dense-matrix codes. These applications are interesting both because they tend to suffer from memory latency, due to the large size of the arrays and the often wide separation between reuses, and because the access patterns are regular and predictable, which gives prefetching a good chance of success [61]. Next we extend this algorithm to handle *indirect* array references, which are another important case and are common to sparse-matrix codes. Finally, we address multiprocessing, where memory latencies can be quite

large. By handling all of these cases, our compiler can cover a significant fraction of scientific and engineering codes.

The second key goal of a prefetching compiler algorithm is maximizing the performance improvement for the cases that are covered. Since prefetching involves a *cost* as well as a benefit, care must be taken to minimize these overheads while maximizing the latency-hiding benefits to achieve the best overall performance.

In addition to these compiler-oriented research goals, our goals in the architecture domain are to determine the proper architectural support for prefetching, and to comparatively evaluate prefetching with respect to other latency-hiding techniques, such as locality optimizations, relaxed consistency models, and multithreading.

#### **1.4 Related Work**

Several other researchers have also worked on software-controlled prefetching. This section summarizes their work and relates it to ours.

Porterfield [9, 64] was the first to explore software-controlled prefetching for uniprocessors. He proposed a compiler algorithm for inserting prefetches into dense-matrix codes. He implemented his algorithm as a preprocessing pass that inserted prefetching into the source code. His initial algorithm prefetched all array references in inner loops one iteration ahead. He recognized that this scheme was issuing too many unnecessary prefetches, and presented a more sophisticated scheme based on dependence vectors and overflow iterations (i.e. the predicted number of iterations where a loop will access more data than fit in the cache). Since the simulation occurred at a fairly abstract level, the prefetching overhead was estimated rather than measured. Overall performance numbers were not presented. Also, the more sophisticated scheme was not automated, since the overflow iterations were calculated by hand, and did not take cache line reuse into account. Despite leaving many important questions unanswered, Porterfield's work demonstrated that software-controlled prefetching was a promising technique that warranted further exploration.

Klaiber and Levy [42] extended Porterfield's work by recognizing the need to prefetch more than a single iteration ahead. They included several memory system parameters in their equation for how many iterations ahead to prefetch, and inserted prefetches by hand at the assembly-code level. The results were presented in terms of average memory access latency rather than overall performance. Also, in contrast with this dissertation, they proposed prefetching into a separate *fetchbuffer* rather than directly into the cache. However, as we will discuss in detail

later in Section 5.1.3, using a separate fetchbuffer has a number of important disadvantages, including the sacrifice of chip area that could otherwise be used for a normal cache, and the fact that it becomes very difficult to makes prefetches *non-binding*, which is a crucial property for multiprocessors.

Gornish, Granston and Veidenbaum [31, 32] presented an algorithm for determining the earliest time when it is safe to prefetch shared data in a multiprocessor with software-controlled cache coherency. Since the prefetches are binding, all control and data dependencies must be carefully considered. Their work is targeted for a block prefetch instruction, rather than the single-line prefetches considered in our study. The proposed schemes are evaluated using a large number of numerical subroutines. Although the speedups predicted from static analysis are quite high, over twofold, the speedups obtained using detailed simulations are limited to 10-20%. The complexity of the compiler algorithm presented in this work illustrates how difficult the compiler's job becomes when *binding* rather than *non-binding* prefetches are used. This is in sharp contrast with the simplicity of our non-binding prefetching algorithm, presented later in Section 4.1.

Chen *et al.* [13] investigated prefetching for non-numerical codes. They attempted to move address generation back as far as possible before loads to hide a small cache miss latency (10 cycles), and found mixed results. Generating addresses early is difficult in non-numerical code because control and data dependencies tend to be tight, and the access patterns can be very irregular. Although these codes are difficult to prefetch, they also tend to make better use of the cache than numerical codes and therefore typically suffer less from memory latency. Because of the difficulty of prefetching highly irregular access patterns and the relatively small expected gains, we chose not to focus on this class of applications during this dissertation.

Tullsen and Eggers [83] post-processed reference traces to evaluate the performance of an "oracle" prefetching scheme on a bus-based multiprocessor architecture with limited bandwidth. They observed that if an application is already bandwidth-limited, prefetching cannot improve performance. However, because of their post-processing trace methodology, they were not able to make proper use of *exclusive-mode* prefetches, which can potentially eliminate up to half of the memory bandwidth consumption. As we will show later in Section 4.3.4, exclusive-mode prefetching eliminates up to 27% of the memory requests in our applications, which would have translated directly into improved performance in their bus-bandwidth-limited architecture.

We now place this related work in the context of our own research. Porterfield's work on software-controlled prefetching for uniprocessors was done concurrently with our investigation of non-binding software-controlled prefetching for multiprocessors as part of the DASH project [54].

Our study, where we inserted prefetches by hand, was the first to consider *non-binding* prefetching for multiprocessors [61]. The compiler algorithm presented in this dissertation partially overlapped the work by Porterfield and by Klaiber and Levy, but has a number of key differences. First, our uniprocessor algorithm is more comprehensive in the types of locality it optimizes for, including temporal, spatial, and group locality. Second, unlike previous studies, we have implemented our algorithm in an optimizing compiler, and can therefore generate overall performance numbers for fully-functional codes. Finally, the scope of our complete algorithm is much broader since it also covers indirect references and multiprocessing.

#### **1.5** Contributions

The primary contributions of this dissertation are the following:

- The proposal of a new compiler algorithm for inserting prefetch instructions in scientific and engineering codes. This algorithm improves upon several previous proposals that focused on dense-matrix uniprocessor codes [31, 42, 64]. In addition, this algorithm handles indirect references, which frequently occur in sparse-matrix codes, and targets large-scale shared-memory multiprocessors as well as uniprocessors.

- A detailed evaluation of the prefetching algorithm based on a full compiler implementation. The prefetching algorithm is implemented in the SUIF (Stanford University Intermediate Form) compiler, which includes many of the standard optimizations and generates code competitive with the MIPS 2.10 compiler[80]. Using this compiler system, we have been able to generate fully functional and optimized code with prefetching. By simulating the code with a detailed architectural model, we can evaluate the effect of prefetching on overall system performance. It is important to focus on the overall performance, because simple characterizations such as the miss rates alone are often misleading. The results of this evaluation show that our algorithm is quite successful at hiding memory latency, improving the performance of some applications by as much as twofold.

- A study of the interaction of prefetching and other techniques for hiding latency, such as data locality optimizations, relaxed consistency models, and multithreading. We find that prefetching is complementary to both locality optimizations and relaxed consistency models, but the benefit of combining prefetching and multithreading is less clear.

• An investigation of the architectural support necessary for software-controlled prefetching, including proposals that may further increase the prefetching performance benefit. In addition to including prefetch instructions in the instruction set, we find that the main support necessary for prefetching is a lockup-free cache. Further enhancements to the architecture may include hardware miss counters to expedite the use of dynamic information, and associativity to reduce the cache conflict problems.

#### **1.6 Organization of Dissertation**

Chapter 2 describes our core prefetching algorithm, which handles affine array references and thus dense-matrix code. A key feature of this algorithm is minimizing prefetching overhead by only prefetching references that are predicted to suffer cache misses. This core algorithm is the basis for all of our experiments, and will be extended in later chapters.

Chapter 3 studies the performance benefits of prefetching for uniprocessor applications, beginning with a detailed evaluation of the algorithm described in Chapter 2. Next we evaluate the interaction between prefetching and locality optimizations, which are another important latencyhiding technique for dense-matrix codes. Finally, we extend our core compiler algorithm to handle indirect references (and hence sparse-matrix codes), and measure the resulting performance improvement of relevant applications.

Chapter 4 focuses on prefetching for large-scale shared-memory multiprocessors. These machines are interesting because of their large performance potential, and because they are particularly prone to suffering from memory latency. We begin by discussing how the prefetching compiler algorithm described in Chapters 2 and 3 is modified to address the issues unique to multiprocessing, and then evaluate its effect on the performance of the entire SPLASH [72] application suite. We also compare compiler-inserted prefetching with hand-inserted prefetching to see whether the compiler is living up to its potential, and to discover methods for further improvement.

Chapter 5 explores the architectural issues associated with prefetching, and is divided into three distinct sections. The first section examines the architectural support necessary for the basic prefetching model assumed in Chapters 3 and 4. The second part considers ways to enhance the architecture to further improve prefetching. The third section comparatively studies other latency-hiding techniques that require architectural support, namely hardware-controlled prefetching, relaxed consistency models, and multithreading. Finally, Chapter 6 contains a summary of the important results in this dissertation, and discusses their implications. It also discusses directions for future work in this area.

### Chapter 2

# Core Compiler Algorithm for Prefetching

In this chapter we present our compiler algorithm for prefetching dense-matrix codes. These applications are a top priority since they consume large numbers of cycles on supercomputers today, they have poor caching behavior, and yet they have regular enough access patterns that prefetching has a reasonable chance of success. Therefore we start by handling these affine array accesses (i.e. where the index functions are affine expressions of the surrounding loop variables), and later build upon this core algorithm in subsequent chapters to handle other important cases such as indirect references and multiprocessor codes.

This chapter is organized in five sections. The first section discusses some key concepts for compiler-based prefetching, including the need to avoid unnecessary overhead. In light of these goals, Section 2.2 provides an overview of our compiler algorithm, which includes both an analysis phase and a scheduling phase. Details of these two phases are presented in Sections 2.3 and 2.4, respectively. The analysis phase uses *locality analysis* to predict which references should be prefetched, and the scheduling phase first uses *loop splitting* to isolate those dynamic miss instances, and then uses *software-pipelining* to schedule prefetches the proper amount of time in advance. Finally, Section 2.5 makes our algorithm concrete by showing the output for some example code, and also discusses issues that arose when implementing the algorithm in the SUIF compiler, such as whether prefetch insertion should occur before or after scalar optimization. The success of this algorithm will be evaluated later in Chapter 3.

## 2.1 Key Concepts

In this section we discuss some important concepts that are useful when thinking about prefetching compiler algorithms.

First of all, prefetches are only *possible* if the memory addresses can be determined ahead of time. For example, if the address is dependent on data that is only available immediately before the memory reference, it may not be possible to compute the address far enough in advance. While this is an important concern with irregular computations, such as those containing pointers and linked lists, it is not an issue for the dense-matrix codes considered in this chapter, since the affine array addresses can always be computed ahead of time.

Given that prefetching is possible, a useful metric for determining success is the *coverage factor*, which is the fraction of original cache misses (i.e. without prefetching) that have been prefetched. Ideally, we would like to prefetch all cache misses, thus achieving a coverage factor of 100%.

However, it is not necessarily the case that "more is better" with prefetching, since prefetches issued for data already in the cache result in overhead without any benefit. Such prefetches are referred to as *unnecessary prefetches*, and should be avoided.

Finally, even if a prefetch is issued for data that is not already in the cache, it may not be *effective* at improving performance if the data is not found in the cache during the subsequent memory reference. This can happen for two reasons. Obviously if the prefetch is issued *too late*, there simply isn't enough time to hide the memory latency. But on the other hand, if the prefetch arrives in the cache *too early*, it may be displaced by other references before it has a chance to be referenced. Having discussed these high-level prefetching concepts, we now focus on the compiler algorithm itself.

Any compiler algorithm for inserting prefetches can be viewed as having two distinct phases. The first phase is an *analysis* phase, where the compiler is trying to answer the question: what exactly should be prefetched? The ideal answer to this question is precisely the set of dynamic references that suffer cache misses. By answering this question correctly, the compiler will maximize the coverage factor and minimize unnecessary prefetches. Once the compiler knows what it wants to prefetch, the second phase is to *schedule* those prefetches so that they are effective and so that they add a minimum amount of instruction overhead.

Minimizing overhead is important, because although the benefit of prefetching is hiding latency, prefetches can introduce two forms of overhead. First, there are additional instructions

| T         | Affine Access |

|-----------|---------------|

| Benchmark | Hit Rate (%)  |

| MXM       | 91.2          |

| CFFT2D    | 87.7          |

| CHOLSKY   | 60.9          |

| BTRIX     | 68.7          |

| GMTRY     | 36.0          |

| EMIT      | 87.1          |

| VPENTA    | 57.7          |

| TOMCATV   | 91.5          |

| OCEAN     | 91.9          |