# IMPLEMENTATION OF A THREE-STAGE BANYAN-BASED ARCHITECTURE WITH INPUT AND OUTPUT BUFFERS FOR LARGE FAST PACKET SWITCHES

Fabio M. Chiussi and Fouad A. Tobagi

**Technical Report No. CSL-TR-93-577**

**June 1993**

This work has been supported in part by NASA under grant NAGW-419, by NSF under grant NCR-9016032, by Pacific Bell and by the AT&T Foundation.

# Implementation of a Three-Stage Banyan-Based Architecture with Input and Output Buffers for Large Fast Packet Switches

Fabio M. Chiussi and Fouad A. Tobagi

Technical Report: CSL-TR-93-577

June 1993

Computer Systems Laboratory

Departments of Electrical Engineering and Computer Science

Stanford University

Stanford, CA 943054055

### Abstract

Fast packet switching, also referred to as Asynchronous Transfer Mode (ATM), has emerged as the most appropriate switching technique for future Broadband Integrated Services Digital Networks (B-ISDN). A three-stage banyan-based switch architecture with input and output buffers has been recently described [Chi93]. Such architecture, also referred to as the Memory/Space/Memory (MSM) switching fabric, is capable of meeting the challenges posed by a successful deployment of B-ISDN; namely, it is made nonblocking with low complexity, and is scalable to large sizes (>1000 input/output ports); it supports a wide diversity of traffic patterns, including highly-bursty traffic; it maintains packet sequence, is self-routing, and is simple to operate.

In this paper, we investigate implementation issues pertaining to the MSM, and demonstrate its feasibility at the sizes of interest, at both 155.52 Mb/s and 622.08 Mb/s ATM standard data rates. For this purpose, we have designed and simulated at the required speeds the critical circuit components of a 1024 x 1024 MSM using a BiCMOS sea-of-gates on a 0.8-µm technology, and studied how system synchronization can be achieved. We estimate that the largest achievable switch size using current VLSI technologies is 4096 x 4096 at the 155.52 Mb/s data rate, and 1024 x 1024 at the 622.08 Mb/s data rate. Finally, we compare the complexity of the MSM switch with that of other fast packer switching architectures, and show that, due to its low chip count and simpler synchronization requirements, the MSM may be built in larger sizes than other architectures.

**Kev Words and Phrases**: fast packet switching, broadband integrated services digital networks, asynchronous transfer mode, high-speed switching systems, banyan interconnection networks, VLSI design, BiCMOS, BiNMOS, Sea-of-Gates.

Copyright © 1993

by

Fabio M. Chiussi and Fouad A. Tobagi

## 1. Introduction

Fast packet switching, also referred to as Asynchronous Transfer Mode (ATM), has emerged as the most appropriate switching technique to handle the high data rates and the wide diversity of traffic requirements envisioned in Broadband Integrated Services Digital Networks (B-ISDN). The ATM standard specifies 53-byte fixed-size packets (referred to as cells) comprising 48 bytes of payload and 5 bytes of control information, and line speeds of 155.52 Mb/s and 622.08 Mb/s [CCI90].

ATM switches capable of meeting the challenges posed by a successful deployment of B-ISDN must be designed and implemented. Such switches should be nonblocking and capable of handling the highly-bursty traffic conditions that future anticipated applications will generate; they should maintain packets belonging to each call in their original order; they should be scalable to the large sizes expected when B-ISDN becomes widely deployed; accordingly, their complexity should be as low as possible; finally, they should be simple to operate; namely, their architecture should facilitate the determination of whether or not a call can be accepted, and the assignment of a route to a call [Chi93].

Several basic architectural designs of ATM switches have been proposed, and many among them fully prototyped [JSA91]. They typically fall into three categories; namely *shared-memory* [Kuw89,Koz9 1 ,Sho9 1], *shared-medium* [Suz89], and *space-division* [Hua84,Tur88,Tob91], each having its features and shortcomings [Tob90a]. Regardless of the particular architectural design used, however, given an implementation technology and its constraints, the size of a switch is bound to be limited. (For the prototypes so far realized, the largest-size switch has been 32 x 32 or 64 x 64 depending on the architecture used.) In order to build larger sizes, several switching modules (of the same or of different types) are combined in a multi-module configuration, which consists of a row of output switches, each handling a group of output lines (e.g., 32 or 64 lines), and

a routing network which routes packets from the input lines to the appropriate output switching module. As with the basic switch architectures, several multi-module switch architectures have been conceived [Suz89,Koz91,Sho91,Ban91,Eng89,Wan92].

A three-stage banyan-based architecture with input and output buffers, which meets the challenges of B-ISDN, has been recently described [Chi92,Chi93]. This architecture, also referred to as the Memory/Space/Memory (MSM) switching fabric, is made nonblocking with low complexity, and is scalable to large sizes; it supports a wide diversity of traffic patterns, including highly-bursty traffic; it maintains packet sequence, is self-routing, and is simple to operate. The MSM features a routing fabric that uses as a building block the banyan routing network (which is self-routing and amenable for VLSI implementation in sizes up to 64 x 64 on a single chip [Mar90, Tob91]); this routing fabric consists of multiple banyan routing networks placed in parallel, with input controllers that dispatch the packets to the banyans in such a way as to achieve efficient utilization of the banyans'. By providing a small amount of buffering in the input components, the number of banyans needed can be reduced to the minimum possible. Packet sequence is maintained by using first-come-first-served service discipline in dispatching packets. The arrangement of the banyans in parallel results in an architecture which allows input and output components to be shared by many lines, and the number of banyans to be increased to that needed to accommodate the traffic, thus increasing the overall size of the switch beyond the achievable size of the banyan networks.

In this paper, we discuss the implementation of the MSM. The MSM offers important advantages at the implementation level in terms of achievable sizes and data rates, owing to:

<sup>1</sup> It is important to note that the use of banyans in parallel with input and output buffers has originally been proposed in [New88b] in the context of unslotted switching systems, and then described in [Sar91] for a slotted switch; a complete characterization of this configuration in terms of its performance under various traffic conditions, including highly-bursty traffic, and a study of its scalability issues has been presented in [Chi93].

- i) a two-phase operation of the banyans (a routing phase and a data-transfer phase), which allows to use different clock rates in each phase to meet different circuit requirements, thus making it possible to sustain high internal data rates (622.08 Mb/s instead of only 155.52 Mb/s) with currently available technologies.

- ii) easier synchronization of the various components (banyans, input controllers, output buffers), which allows to build a large switching fabric (> 1000 input/output ports), and operate it at 622.08 Mb/s.

The objective of our implementation work on the MSM switching fabric is threefold.

- i) Study implementation issues in the MSM, and demonstrate the feasibility of the switch at both 155.52 Mb/s and 622.08 Mb/s ATM data rates. For this purpose, we have designed and simulated at the required speeds the critical circuit components of a 1024 x 1024 MSM using a BiCMOS (BiNMOS) sea-of-gates [ElG89] on a 0.8-μm technology [ElD89,ElD90], and studied how system synchronization can be achieved.

- ii) Estimate the largest achievable switch size using current VLSI technologies. Based on our implementation experience and on the analysis of existing realizations of circuitries performing functionalities similar to those needed in the MSM, we estimate that, by using full-custom design and state-of-the-art VLSI technologies, an MSM of size 8192 x 8192 is feasible at the 155.52 Mb/s data rate, and an MSM of size 1024 x 1024 is the largest feasible switch at 622.08 Mb/s.

- iii) Compare the complexity of the MSM switch with that of other architectures. Specifically, we show that, for a given size, the chip count of the MSM is significantly lower than that of multistage configurations of nonblocking modules. We also show that, due to its low chip count, simpler synchronization

requirements, and self-routing operation, the MSM may be built in larger sizes than other architectures.

This paper is organized as follows. In Section 2, we describe the architecture and operation of the Memory/Space/Memory switching fabric. In Section 3, we discuss its implementation issues, describe our design, and estimate the achievable switch size with current VLSI technologies; we then compare the complexity of the MSM with that of other architectures.

# 2. The Memory/Space/Memory Switching Fabric

### 2.1. Basic Configuration

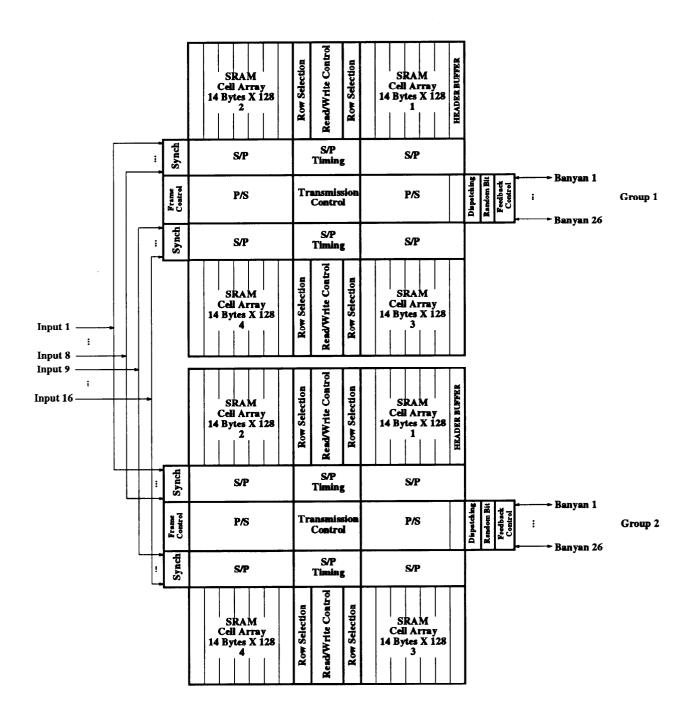

### a) Architecture

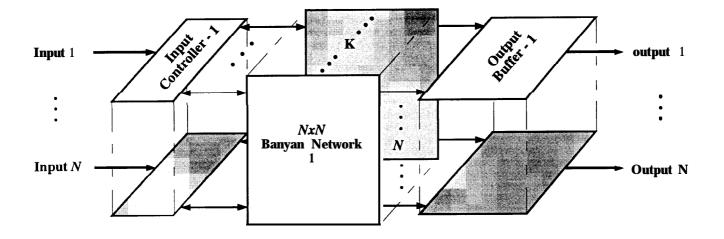

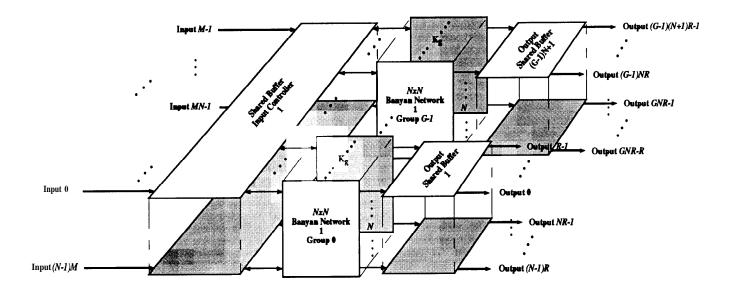

In its basic configuration, shown in Fig. 1, the Memory/Space/Memory (MSM) switching fabric consists of K banyans placed in parallel, along with input controllers with buffer capabilities, one for each of the **N** inputs, which dispatch the incoming packets to the banyans, and output buffers connected to the corresponding outputs of each banyan. In order to minimize the number of banyans necessary to achieve a desired packet loss rate, the input controllers must dispatch the packets to the banyans so as to maximize the utilization of the banyan networks. This can be achieved by dispatching the packets to the banyans in sequence (referred to **as sequential dispatching** in the following). The operation of the switch is assumed to be slotted. In every time slot, each input controller which has packet(s) available in its corresponding input buffer dispatches a packet to the first banyan in the sequence; packets are then routed by the banyan; successful packets proceed to the output buffers, and unsuccessful packets are dispatched to the second banyan. The operation proceeds similarly for all the banyans; packets that are still unsuccessful after the last banyan has been attempted are stored in the input buffers for further processing in the next slot. By organizing the input buffers as FIFO's, the sequence of the packets is maintained.

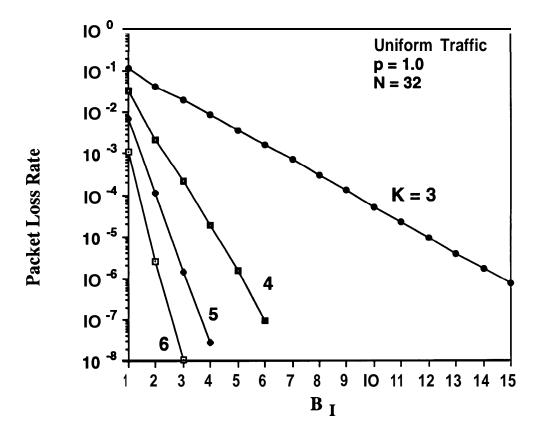

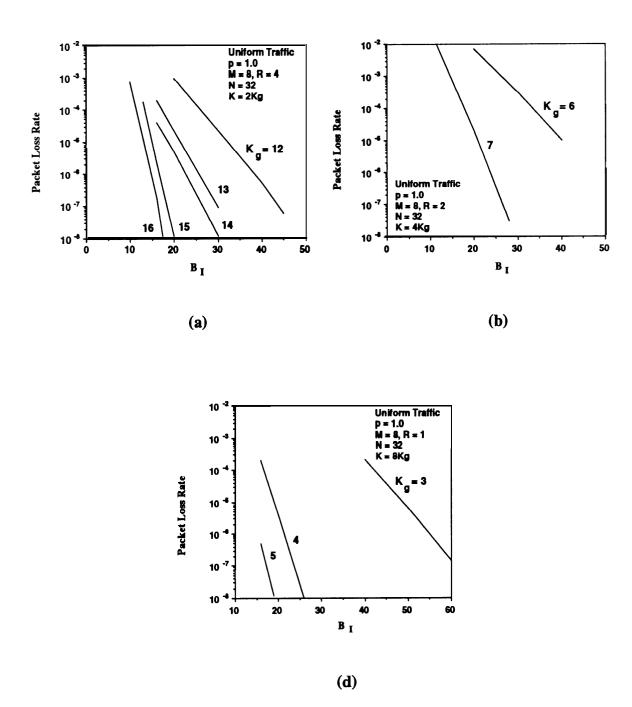

For given switch size and traffic characteristics, the number of packets lost in the input buffers is a function of the number of banyan networks K and the size (in packets) of the input buffers  $B_I$ . The packet loss rate in the MSM with sequential dispatching, under uniform traffic at full load, is shown in Fig. 2, for N = 32. A minimum of 3 banyans in parallel is necessary to achieve low packet loss rates ( $< 10^{-6}$ ) with small input buffer

Fig. 1. The MSM switching fabric: basic configuration.

sizes, under uniform traffic at full load. This minimum of 3 networks in parallel is easily anticipated, since the throughput of a single banyan network of size N = 32 at full load is 0.4, making the total capacity with three networks about 1.2. The 20% extra capacity available explains the relatively small buffer sizes needed. (More detailed simulation results are reported in [Chi93].)

### b) Switch Operation

We now describe in more detail the operation of the banyans. In our discussion, we consider the switch operation to be synchronous. All incoming lines have the same transmission capacity, packets have fixed size L (namely, we consider 53-byte ATM packets), and the time axis is slotted with slot size T equal to the transmission time of a packet on a line. In general, however, incoming packets from different input lines are not synchronized with each other, nor with the internal system clock. We begin here by assuming that packets on different input lines have been synchronized and aligned with the system slot boundaries. In Section 3.4 below, we discuss how this synchronization

Fig. 2. Packet loss rate in the input buffers of the MSM switching fabric with input buffers and sequential dispatching, under uniform traffic at full load, A4 = 1, N = 32 (obtained by simulation).

may be achieved within the controllers and the banyan networks, thus obviating the need for external aligners.

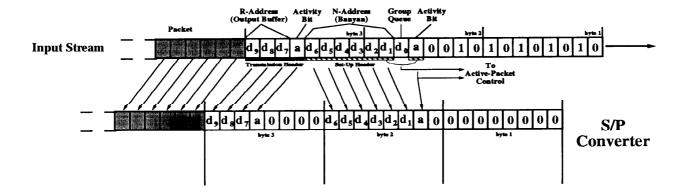

As in any ATM switch [JSA91], for each packet, prior to entering the MSM switching fabric, header-conversion circuits generate the local switching header used by the switching fabric, based on the information in the ATM header. The local header in the MSM comprises three fields:

Activity Bit a: it indicates whether the current slot contains a packet (a = 1), or not (a = 0).

- Priority Field P: this field is optional and is used only if multiple priority classes exist. It comprises  $\mathbf{q} = \log_{\mathbf{q}} \mathbf{Q}$  bits, where  $\mathbf{Q}$  is the number of external priority levels.

- Address Field D: This field contains the address of the output port  $d_1, d_2, \ldots, d_n$  (where  $n = \log_1 N$ , and  $d_1$  is the most significant bit); it is inferred from the virtual circuit information in the ATM header.

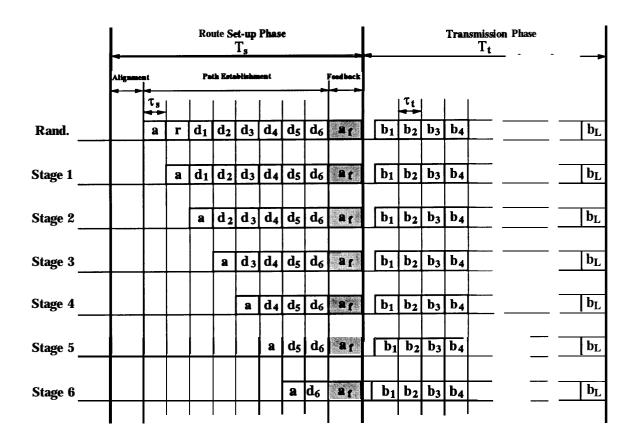

Once the local header is generated, packets are sent to the switching fabric, stored in the corresponding input buffers, and then dispatched to the banyans. To perform the dispatching algorithm, in every slot the operation of a banyan is divided in two phases:

1) **Route Set-up Phase.** During this phase, the local switching header portions of the packets (referred in the following simply as **headers**) are routed through the banyan, establishing the paths in the interconnection network. At any stage s in the banyan, the proper setting of a switching element is a function of two bits in each header present at its inputs, namely **a** and  $d_s$  (if external-priority service is in effect, then the setting is also a function of the priority fields in the headers). An active header (identified by  $\mathbf{a} = 1$ ) arriving at a switching element requests to be routed to the upper output if  $d_s = 0$ , and to the lower output if  $d_s = 1$ . Anytime there is a conflict between two active headers at a switching element (i.e.,  $d_s$ -bits are equal for the two headers), one of the two headers is routed properly, while the other is forced in the "wrong" direction and has its activity bit reset (clearly, this conflict resolution follows a similar idea to that used in the TBSF). The selection of the "winner" can be random, but more practical deterministic selection algorithms can be adopted with no effect on performance. A non-active header (identified by a = 0, i.e., either a misrouted header or an empty slot, is routed accordingly to the current state of the switching element (determined by the other header, if active, or by the state of the switching element in the previous slot).

Once the headers reach the outputs of the banyan network, the outcome of the route set-up phase (i.e., which headers have been properly routed by the network) is described by the activity bit of the headers: headers with  $\mathbf{a} = 1$  at the output of the network have been successfully routed; headers with  $\mathbf{a} = 0$  have been misrouted (or represent empty slots). The outcome of the route set-up phase is fed back to each controller at the input by having the switching elements in the last stage of the banyan network transmit backward the activity bit of each header, all the way to the input controllers, through the paths that have just been set-up.

2) **Packet Transmission Phase.** Each input controller examines the feedback signal and determines whether the header has been routed properly or not. If the header has been successful (feedback signal = 1), the controller transmits the packet (i.e., the ATM header and payload) to the output buffers.

With sequential dispatching, at the end of the route set-up phase, if an input controller determines that the header currently in process has been properly routed by a banyan, it transmits the corresponding packet to that banyan, and dispatches the next header in the input queue to the remaining banyans in the sequence. If a header has been unsuccessful in a banyan, it is simply dispatched to the following one. Packets which are unsuccessful after the last banyan has been attempted, remain in the input buffers and are processed in the following time slot. Up to **K** packets can be routed from each input to the outputs in a time slot.

The two-phase operation brings important benefits at the implementation level. They are discussed in detail in Section 3.

Fig. 3. The MSM switching fabric for large fast packet switches.

### 2.2. Large Size MSM Switching Modules

### a) Architecture

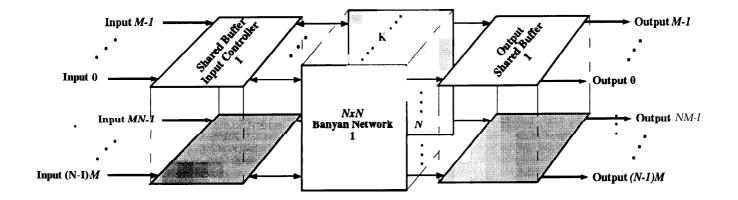

In order to increase the size of the MSM switch beyond the achievable size of the banyan network, we observe that, given their relatively simple functionality and small buffer requirements, the input components actually have the capacity to handle more traffic than that coming from one input line and to control a number of banyans larger than that needed to sustain the traffic from a single line; similarly, the output components have the capacity to handle more traffic than that destined to a single output line. Therefore input and output components can be shared by several (say M) inputs and outputs, respectively, making the total size of the switching fabric equal to  $M \cdot N$ . The resulting configuration is shown in Fig. 3. The switch operates as follows: in each input controller, packets arriving at its M input lines are first multiplexed into a shared buffer; packets are then sequentially dispatched to the banyans and routed to their requested output shared buffers; finally, in each output component, packets are switched to their requested output links selected among the M output ports served by the buffer. In this case, the first log, N bits of the address field D in the local switching header are used for routing the packets in

Fig. 4. Packet loss rate in the input buffers of a 256 x 256 MSM switch, M = 8, N = 32, under uniform traffic conditions, p = 1 (obtained by simulation).

the banyan networks, and the remaining  $\log$ , M bits in the address field specify the desired output port among the M ports served by the corresponding output buffer "switch".

Since the routing capacity offered by the banyans in parallel must be adequate to sustain the aggregate traffic from the M links entering each input controller, the required K to maintain a given packet loss rate in the input buffers increases with M. As a rule of thumb, for N = 32 and N = 64, 3 banyans for each of the input ports sharing an input controller are needed to achieve very low packet loss rates in the input buffers with relatively small sizes of the input shared buffers  $B_I$ , under uniform traffic at full load (again, this rule of thumb is easily anticipated, since the throughput of a banyan network with N = 32 and N = 64 at full load is 0.40 and 0.36, respectively, making the total capacity with three networks larger than 1, and the total capacity with M = M networks larger than M. For example, the packet loss rate in the input buffers of a 256  $\times$  256 switch with M = M and M = M and M = M under uniform traffic at full load, is depicted in Fig. 4. With M = M and M = M packet buffers are needed to achieve a packet loss probability equal to M = M. If more banyans are used, smaller buffer sizes suffice for the same packet loss rate.

In the MSM switching fabric, the number of input lines that can be fed to an input controller and the number of output lines that can be served by an output shared buffer are limited by four factors:

- i) the bandwidth requirements of input and output memories, respectively;

- ii) the functionality to be performed in the input controller and in the output buffer, respectively;

- iii) the buffer requirements  $B_I$  and  $B_O$ , respectively, necessary to guarantee a desired packet loss rate in the fabric; and

- iv) the number of dispatching operations to different banyans that can be completed within a slot duration.

Here, we briefly discuss the nature and extent of these limitations in the input and output components.

The memory bandwidth in the input components must be adequate to sustain a flow of M packets into the memory and K packets from the memory per slot; the memory bandwidth is therefore equal to (M + K)V, where V is the line speed. However, we have show in [Chi93] that it can be reduced to (2M + 1)V with no noticeable degradation in performance. The memory bandwidth in the output components is equal to (M + K)V.

In the input components, with sequential dispatching and related FIFO operation, the shared memory is a relatively simple sequentially-accessed memory. The memory control must be capable of synchronizing and multiplexing M incoming packets into the memory, of retrieving up to K packets from the memory per slot (again, it has been shown in [Chi93] that the maximum number of retrieved packets per slot can be limited to M + 1 with no observable performance degradation), and of delivering them to the corresponding banyans in which paths have been set up. The functionality of the input controllers has to

include the implementation of the sequential dispatching algorithm to orchestrate the operation of the banyan networks. Given the simplicity of the algorithm, however, this limiting factor is not as important as synchronization, bandwidth and memory access requirements.

In contrast, the output buffer is a shared-memory switch serving M ports, and therefore is a randomly-accessed memory in which M linked lists have to be managed. The memory control logic has to synchronize and **enqueue** in the requested queues up to K incoming packets, and retrieve from the memory and transmit to the proper output ports M outgoing packets per slot.

The buffer requirements are fairly modest in the input controllers under any traffic condition of interest, as shown in more detail in the following section. On the contrary, since the MSM achieves output buffering, if the switch is designed to sustain bursty traffic, the local buffer requirements in the output components are large, thus becoming an important concern.

Finally, the objective of maintaining packet sequence poses an additional limitation on the number of lines served by input and output components, since the sequential scanning of all the K banyans must be completed within a slot duration T in order to maintain FIFO operation of the input buffers. Therefore, the maximum number of banyans that can be placed in parallel is:

$$K_{\text{max}} = T / T_s = \frac{T_s + T_t}{T_s} \tag{1}$$

where  $T_s$  is the duration of the set-up phase and  $T_t$  is the duration of the transmission phase in a banyan. Thus, the limitation on  $K_{\text{max}}$  comes from the achievable clock rate during the set-up phase.

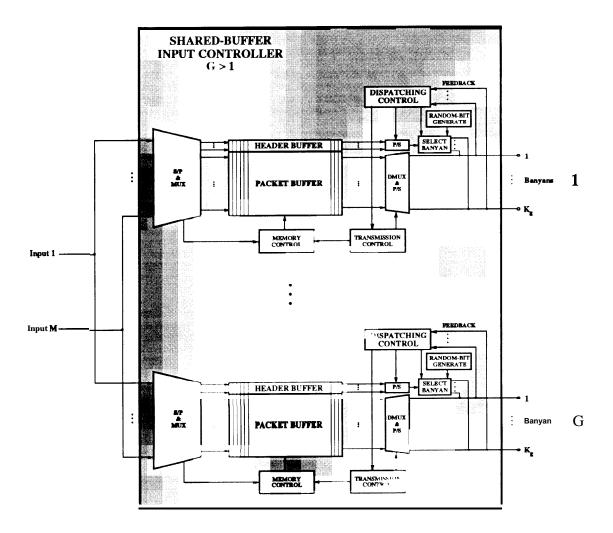

Fig. 5. The MSM switching fabric: general configuration, M/R = G > 1.

This discussion suggests that, as far as the limitations on bandwidth, functionality and buffer requirements are concerned, the achievable number of input lines  $\mathbf{M}$  in a controller may be larger than the achievable number of output lines  $\mathbf{R}$  in an output buffer. In the configuration of Fig. 3, however, for a given  $\mathbf{N}$ , the more stringent limitations on  $\mathbf{R}$  would determine the achievable switch size; furthermore, in this configuration, we note that, since  $\mathbf{K}$  is a function of  $\mathbf{M}$ , the limitation on  $\mathbf{K}$  imposed by the requirement to complete the dispatching to all the banyans within a time slot directly translates into a limitation on  $\mathbf{M}$  (and on  $\mathbf{R}$ ).

To further increase the maximum achievable switch size, we have therefore proposed the general configuration for the MSM, shown in Fig. 5. In this configuration, each input controller receives M input lines and is connected to G groups of  $K_g$  banyans each (the total number of banyans is still defined as  $K = GK_g$ ). In each group, each of the corresponding output buffers has R output ports, where R = M/G. With G > 1, the input controller first selects the desired output group to which each of the packet is destined

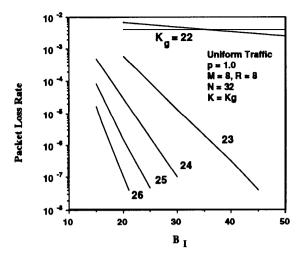

(specified by the first log, G bits in the address field of the local switching header) and enqueues the packet in the corresponding input queue. Then the operation proceeds as described above, by applying the dispatching algorithm to each of the G groups of  $K_g$  banyans. Packets are routed to their requested output shared buffer, and then switched to the requested output port selected among the R ports served by the buffer. In this general case, as a rule of thumb, in each group, 3 banyans for each of the R output ports connected to an output shared buffer are necessary to achieve low packet loss rates in the input buffers with small buffer sizes. In general, for increasing values of G, with constant total number of banyans K, the required input buffer size to achieve a desired packet loss rate increases slightly; alternatively, more banyans have to be used. For example, the packet loss rate in the input buffers of the 256 x 256 switch with M = 8 and N = 32, described above for R = 1, is depicted in Fig. 6 for different R. With R = 4, for  $K = 2K_g = 24$  banyans (i.e., with two groups of  $K_g = 12$  banyans each), 44 packet buffers are needed to guarantee a  $10^{-7}$  packet loss rate (rather than 30 buffers in the case with R = 1). (More detailed simulation results are reported in [Chi93].)

In the general configuration, the bandwidth of the output shared memories is reduced to  $(K_g + R)V$ . The output components have only R output ports, thus reducing the complexity of the memory management and the local buffer requirements in each component. In the input controllers, the shared memory accommodating the G input queues has still bandwidth (M + K)V (it can be reduced to (2M + G)V with no observable degradation in performance [Chi93]). If the bandwidth is not manageable, completely partitioned memories for each group can be used, each with bandwidth  $(M + K_g)V$  (which can be limited to (M + R + 1)V); it is shown in [Chi93] that, by using partitioned memories, the increase in total required input buffer size is not significant. Also the limitation on the number of banyans in parallel coming from the requirement to complete the scanning of all the banyans within a time slot is significantly ameliorated since, given

Fig. 6. Packet loss rate in the input buffers of a 256  $\times$  256 MSM switch, G > 1, under uniform traffic conditions,  $\mathbf{p} = 1$ , N = 32; a) M = 8, R = 4; b) M = 8, R = 2; c) M = 8, R = 1 (obtained by simulation).

that the dispatching algorithm is performed on each group in parallel, only  $K_g$  set-up phases (as opposed to K set-up phases as in the previous configuration) have to be completed in a time slot. With this configuration, therefore, we can individually adjust the design parameters M, R, N, G,  $K_g$ ,  $B_I$  and  $B_O$  to accommodate the technology constraints and achieve the desired size and performance.

### b) Correlated Traffic Patterns

Since the throughput of a banyan network is very sensitive to the input traffic pattern, one possible cause of concern in the MSM switching fabric is the fact that the packets, during their sequential scanning of the banyans, enter every banyan in the sequence from the same input. Under traffic patterns exhibiting correlation among packets, either in the space domain (e.g., *communities-of-interest* traffic pattern [Tur88,Tob91,Chi93]) or in the time domain (e.g., bursty traffic pattern), this may lead to recurrent conflicts between the same packets maintained over consecutive banyans and/or several slots, and cause degradation in throughput. Consequently, more banyans may have to be provided to achieve low packet loss rates [Chi93].

Providing more banyan, although possible, is not desirable. In fact, as mentioned above, there is a limit on the number of banyans that can be used in parallel with FCFS operation of the input buffers (*i.e.*, maintaining the sequence of the packets); thus, a larger number of banyans translates into a stricter limitation on *M*, and consequently on the switch size (of course, providing more banyans also increases the required amount of resources and complicates the control of the banyans).

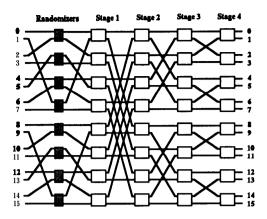

An effective solution to overcome the throughput degradation under correlated traffic patterns is to randomize the input patterns of different banyans, so as to reduce the likelihood of persistent "bad patterns" and recurrent conflicts. One possibility is to provide a *full randomization network* in front of each banyan, which provides randomization over

Fig. '7. Example of a banyan networks augmented with randomizers by pairs, N = 16.

all inputs of the banyan [Tur88]. The complexity of the resulting concatenation of the randomization network and the banyan network is twice the complexity of the banyan network [Chi93]. In particular, the number of stages is doubled; consequently, in the MSM, the duration of the route set-up phase  $T_s$  in each routing network is also doubled. Since the limitation on the maximum number of banyan networks that can be placed in parallel is  $K_{max} = T / T_s$ , doubling  $T_s$  halves  $K_{max}$ , and again translates into a stricter limitation on M.

In [Chi93], we show that most of the benefits of a full randomization network are obtained with minimum additional hardware complexity by using a **single-stage** randomization network which randomizes packets only between properly selected pairs of inputs. Since such a network consists of a single stage, the impact on  $T_s$  (and consequently on  $K_{max}$ ) resulting from its addition is minimal. Furthermore, we note that in practice, given the typical aspect ratios of VLSI designs of banyan networks, such additional stage can be usually fitted rather easily on the same chip of the banyan network (thus, the additional hardware complexity resulting from the use of a single-stage randomization network is negligible). A procedure to construct the single-stage randomization network (also referred to as *randomizers* by *pairs*) is presented in [Chi93]. An example of the configuration resulting from the addition of the randomizers by pairs

in front of a banyan network is shown in Fig. 7, for N = 16. Under correlated traffic patterns, the addition of randomizers by pairs in front of the banyans effectively breaks the correlation among packets by distributing the traffic in the networks, and eliminates throughput degradation [Chi93]. From a practical point of view, the single-stage randomization network can be simply implemented by adding, in front of each banyan network, an extra stage of switching elements with the activity-bit-resetting capability disabled, and by providing an additional randomly-generated bit in the address field of the headers to control them.

### c) The MSM Output Buffers

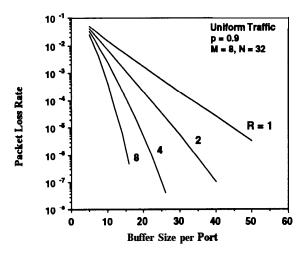

Packet loss in the MSM occurs also in the output buffers. For a given switch size, the number of packets lost in the output buffers is a function of the output buffer size  $B_O$  (in packets) and the traffic pattern. The output-buffer requirements are also highly dependent on the degree of memory sharing in the buffers.

The output-buffer requirements in an output buffer switch under uniform traffic conditions have been extensively studied by several authors [Hlu87,Hlu88,Eck88], for both completely-partitioned and shared memories. Under these traffic conditions, the required buffer sizes are relatively small. For example, at loads as high as 0.95, 110 packet buffers per port are sufficient to guarantee packet loss rates lower than  $10^{-6}$ . Assuming 53-byte ATM cells, this translates in memory sizes of less than 50 Kbit. The buffer requirements decrease rapidly as the load decreases. At 0.9 load, 5 1 packet buffers are **necessary** to achieve  $10^{-6}$  loss rate; at 0.8 load, 28 buffers are required for the same loss rate.

With R > 1, each output buffer is shared among R ports. The required buffer size per port decreases significantly as the memory is shared among more and more ports [Hlu87,Hlu88]. For example, the buffer requirements per output port in a 256  $\times$ 256

Fig. 8. Packet loss rate in the output buffers of a 256  $\times$  256 MSM, M = 8, under uniform traffic conditions, for different R, p = 0.9 (obtained by simulation).

MSM with  $\mathbf{M} = 8$  and  $\mathbf{N} = 32$ , obtained by simulation, are shown in Fig. 8 for  $\mathbf{R}$  ranging from 1 to 8, at load  $\mathbf{p} = 0.9$ ; 56 packet buffers are necessary to achieve a packet loss rate below  $\mathbf{10^{-6}}$  with completely-partitioned buffers  $(\mathbf{R} = 1)$ ; a substantial reduction in buffer size per port is attained for  $\mathbf{R} = 2$ ; in this case, 35 buffers per port suffice for the same packet loss rate. The reduction continues for larger  $\mathbf{R}$ , albeit it is progressively of a lesser extent; for  $\mathbf{R} = 4$ , 23 packet buffers per port, and for  $\mathbf{R} = 8$ , 15 buffers per port are required for a loss rate below 10". In general, in each output buffer component, the buffer requirements to accommodate uniform traffic are fairly small, for both completely-partitioned and shared buffers. Assuming ATM cells, with  $\mathbf{R} = 1$ , a memory of less than 25 Kbit is required in each single-port output buffer to sustain a 0.9 load; for  $\mathbf{R} = 8$ , a total memory of 50 Kbit in each 8-port output buffer component is necessary at the same load.

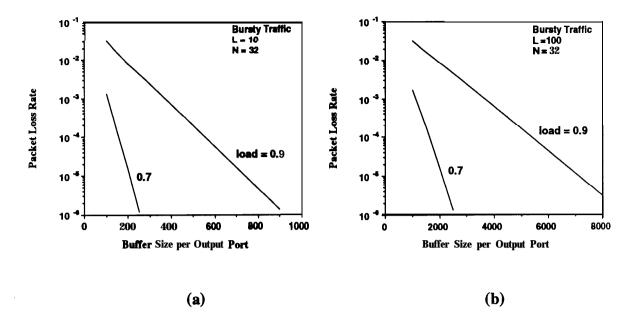

In a switch achieving output buffering, under bursty traffic, the size of the output buffers required to guarantee a desired packet loss rate is substantially larger than that needed under uniform traffic conditions [End90,Lie90,Chi93]. For example, considering a bursty traffic model in which each input generates geometrically distributed bursts of average length L (within a burst, packets destined to the same output arrive continuously

Fig. 9. Packet loss rate in the output buffers of an MSM, under bursty traffic, for 0.9 and 0.7 load, N = 32; a) L = 10; b) L = 100 (obtained by simulation).

in consecutive time slot), with the output requests of the bursts uniformly distributed over all destinations, the packet loss rate in the output buffers of a 32  $\times$  32 MSM with M = R = 1, at 0.9 and 0.7 load, obtained by simulation, is shown in Fig. 9.(a) and Fig. 9.(b), for average burst lengths L = 10 and L = 100, respectively. At 0.9 load, for L = 10, more than 920 packet buffers per port are necessary to achieve a loss rate below  $10^{-6}$ ; the increase in buffer size is quite dramatic respect to the 51 packet buffers required under uniform traffic conditions at the same load. The required buffer size for a desired packet loss rate increases approximately linearly with the average burst size. For L = 100, 9000 buffers are necessary for a 10" loss rate. Also under bursty traffic conditions, memory sharing substantially decreases the required output buffer size per port to meet a given packet loss rate. For example, in a 128 ×128 MSM with M = R = 4, with L = 10, at 0.9 load, 440 packet buffers per port suffice for  $10^{-7}$  loss rate [Chi93]. The increase in buffer requirements with the burst size is still approximately linear; with L = 100, 4600 buffers per port are necessary for the same packet loss rate. In each output-buffer component, the local buffer requirements to sustain bursty traffic conditions are clearly quite large. With

ATM cells, in the 32  $\times$  32 switch, the required memory size in each single-port output-buffer component is approximately 4 Mbit, to accommodate bursts with average size of 100 packets at 0.9 load. In the 128  $\times$  128 switch, each four-port output component requires a memory of about 8 Mbit to sustain the same traffic.

# 3. Implementation of the Memory/Space/Memory Switching Fabric

As described in the previous section, the MSM switching fabric consists of several instances of three basic components: the banyan-network component, the input-controller component, and the output-buffer component. In the following, for each of these components, we:

- i) describe its functionality;

- ii) identify implementation objectives and issues pertaining to the component;

- iii) describe our implementation;

- iv) estimate the achievable size of the component with current VLSI technologies.

We then address how such components can be synchronized together in order to build the complete switching system, and describe the circuitry that must be added to each component in order to make system synchronization possible.

### 3.1. The Banyan Network Component

### 3.1.1. Functionality

The functionality and operation of the banyan network has been described in Section 2.1 above. We recall that, in every slot, the operation is divided in two phases:

i) a route set-up phase, in which the header portions of the packets are routed through the banyan, establishing the paths in the interconnection network; at the end of this phase, a feedback signal consisting of the activity bit of the headers once they reach the outputs of the network is sent back to each controller at the input; and

ii) a transmission phase, in which the packets corresponding to successful headers are transmitted to the output buffers through the paths that have been set-up.

It is important to note that in the MSM the operation of the banyan during the route set-up phase is fully synchronous; namely, in order to perform the switching algorithm, all headers are bit-synchronized and aligned (i.e., their starting times are synchronized) with one another at the input of the network, and their synchronization and alignment maintained at each stage in the network. In contrast, during the transmission phase, the paths have already been set-up, bit streams can flow "freely" to the outputs, and therefore alignment of the packets is not necessary. (Internally to the network, even bit-synchronization of the streams is not required.) However, synchronization between connected pairs of inputs and outputs in the banyan must be maintained.

From an implementation point of view, the two-phase operation of the banyans brings two important benefits at the chip-design level.

i)

The two-phase operation implies that different clock rates may be used in each phase. During the route set-up phase, the logic in charge of the switching algorithm and the requirement of keeping the header synchronized and aligned impose the critical constraints on the clock rate. On the contrary, during the packet transmission phase, no logic is involved and synchronization is looser. This means that the hardware constraints during different phases may differ substantially, and the maximum achievable clock rate in the route set-up phase may be lower than the maximum achievable clock rate in the transmission phase (for example, circuit simulations show that, using state-of-the-art CMOS or BiCMOS technology [ElD89], the sustainable clock rate in the route set-up phase may be four times lower than the clock rate in the transmission phase). Using different clock rates is useful in two respects: a) it allows to support the 622.08 Mb/s data rate; in fact, even with advanced BiCMOS technology it would not be possible to achieve a 622 MHz clock rate during the route set-up

phase (while clock rates as high as 800 MHz can be achieved in the transmission phase); and b) at lower data rates (*i.e.*, 155.52 Mb/s) it allows to simplify the switching element and reduce its area; in fact, by using a lower clock rate in the route set-up phase, the synchronization of clock and data signals both within the switching elements and from stage to stage is simpler, and can be achieved just by matching the signals' delays, (rather than by using circuitry to preserve synchronization), thus translating into a smaller design.

ii) With the two-phase operation, the state of the switching elements is set prior to the transmission of the packets. Thus, within each switching element, the path followed by the packets does not include the storage elements occupied by the control bits needed to perform the switching algorithm. This reduces considerably dynamic power dissipation internally to the chip.

Finally, we recall that **randomizer** by pairs (consisting of a single stage of switching elements whose state is randomly set) are added (on the same chip) in front of the banyan networks. Therefore, the routing network (*i.e.*, randomizers plus banyan network) comprises three different types of switching elements: a) switching elements to be used in all but the last stage of the banyan network; b) switching elements to be used in the last stage of the banyan network, capable of generating and transmitting back the feedback signal; and c) switching elements to be used in the single-stage randomizers. In the following, we show that all these switching elements can actually be obtained by simple variations of a single basic design.

### 3.1.2. Implementation Objectives and Issues

The objectives in the implementation of the banyan network component are four:

i) to implement a routing network of the largest size possible on a single chip;

- ii) to support the desired operating data rates (155.52 Mb/s and 622.08 Mb/s);

- iii) to limit power dissipation; and

- iv) to perform the switching algorithm during the route set-up phase incurring a small latency per switching element.

The last objective is motivated by the fact that, as noted in Section 2.2 above, the number of banyans in parallel Kg that is used in a group must satisfy:

$$K_g \le T / T_s = \frac{T_s + T_t}{T_s} \tag{1}$$

where T is the duration of the time slot,  $T_s$  the duration of the set-up phase and  $T_t$  the duration of the transmission phase; from condition (1),  $T_s \leq T/K_g$ ; thus, given a certain number of banyans  $K_g$  that have to be used in parallel to provide the required routing capacity, a small latency per switching element translates into a lower required clock rate in the route set-up phase; in fact, in general,  $T_s$  is given by:

$$T_{s} = (n + 1) \cdot \frac{l_{s}}{R_{s}} + (f + a_{s}) \frac{1}{R_{s}}$$

(2)

where n + 1 is the number of stages ( $n = \log$ , N stages in the banyan, plus one stage for the randomizers),  $l_s$  is the latency per stage (in bits) incurred to perform the switching algorithm,  $R_s$  is the clock rate during the route set-up phase, f is the duration (in bits) of the feedback phase, and a, is the duration of any additional period of time that may be necessary for signal synchronization and for changing the flow of signals from forward direction (i.e., from inputs to outputs, during set-up) to reverse direction (i.e., from outputs to inputs, during feedback), as explained in more detail below.

Conversely, we note that, for a given latency per switching element, the required clock rates during set-up and transmission phases depend on the number of banyans Kg that have to be scanned in a slot. In fact, from condition (1), the larger the number of

banyans that have to be scanned in a slot is, the smaller  $T_s$  is, and the higher the required clock rate during the set-up phase is. (Similarly, note that the smaller  $T_s$  is, the larger  $T_t$  is, and the lower the required clock rate during the transmission phase is; the duration  $T_t$  of the transmission phase is:

$$T_{t} = (424 + r + 1 + a_{t}) \frac{1}{R_{t}}$$

(3)

where 424 is the number of bits in an ATM cell,  $r = \log_t R =$

From a design point of view, since the number of banyans that have to be scanned in a slot, for a given **M**, depends on the choice of the design parameter G, by properly choosing G we can impose required clock rates in the two phases of operations that are achievable with the available technology.

As a practical example of how the choice of G can be made taking into account the technology constraints on the achievable clock rates in the banyans, we consider our realization of the banyan network for a  $1024 \times 1024$  MSM switch (M = 16, N = 64) for both 155.52 Mb/s and 620.08 Mb/s data rates.

At 149.76 Mb/s data rate (corresponding to the 155.52 Mb/s raw ATM data rate), the slot duration T is 2.83  $\mu$ s. Assuming f = 2 bits and f = 4 bits, from equation (2) we have f = 13 / f = 13 / f = 13 / f = 13 we also assume f = 13 high and f = 13

In reality, f, a,, and a, depend on the clock rate, as explained below; thus, these assumptions should be verified once the clock rates have been derived, and the procedure iterated.

| G | $K_{g}$   | $T_s$          | $R_s$       | $R_t$       |

|---|-----------|----------------|-------------|-------------|

| 1 | <b>50</b> | <b>56.6</b> ns | 229.58 Mb/s | 155.34 Mb/s |

| 2 | 26        | 108.9 ns       | 119.38 Mb/s | 157.95 Mb/s |

| 4 | 13        | 217.8 ns       | 59.69 Mb/s  | 164.15 Mb/s |

It is evident from these examples that the clock rate in the set-up phase is highly dependent on G; thus, indeed, by properly choosing G, we can adjust the required clock rates so that they can be achieved with the available technology. In our realization, although the clock rate required with G = 1 is within the limits of the **BiCMOS** technology adopted, we have preferred a more conservative approach, and chosen G = 2. The lower clock rate required in the set-up phase with G = 2 has allowed us to relax the specifications of the logic design and achieve synchronization more easily, leading to simpler and more robust design. We also note that the clock rates required with G = 4 are comfortably achievable even by conventional CMOS technology.

At 599.04 Mb/s data rate (corresponding to the 622.08 Mb/s raw ATM data rate), the slot duration T is 0.7 1  $\mu$ s. Assuming f = 2 and  $a_s = 7$ , we obtain  $T_s = 16 / R_s$ . We also assume  $a_s = 8$  bits. In this case, for different G, the minimum required clock rates in the two phases of operation are:

| G | $K_g$     | $T_s$          | $R_s$              | $R_t$              |

|---|-----------|----------------|--------------------|--------------------|

| 1 | <b>50</b> | 14.2 ns        | 1130.26 Mb/s       | 630.0 1 Mb/s       |

| 2 | 26        | 27.2 ns        | <b>587.74</b> Mb/s | <b>640.63</b> Mb/s |

| 4 | 13        | <b>54.4</b> ns | 293.87 Mb/s        | 665.79 Mb/s        |

| 8 | 8         | <b>88.4</b> ns | 180.84 Mb/s        | 700.76 Mb/s        |

The clock rates in the set-up phase required with G = 1 and G = 2 are not achievable with our technology. The clock rate required with G = 4 is at the edge of what can be obtained with the technology. Given the experimental nature of our realization, we have chosen G

= 4 and adopted an aggressive design approach to meet the speed requirements. However, as noted below, the design tolerances that we were able to achieve would not be sufficient in a design destined to in-field use. A more conservative and robust choice would be G = 8, leading to less strict synchronization requirements and wider tolerances in the design.

### 3.1.3. Chip Design

We have designed a chip realizing a  $64 \times 64$  banyan network augmented with randomizers by pairs. Two versions of this chip have been designed and simulated, one for the 155.52 Mb/s ATM data rate and the other for the 622.08 Mb/s ATM data rate. They differ in that the design for the lower data rate has been kept simple and compact, while the design for the higher data rate is slightly larger and more complex, since it requires some additional circuitry in order to meet the tighter circuit specification.

### a) 155.52 Mb/s Design — Chip Layout and Global Signals

The chip layout of the version for the 155.52 Mb/s fits on a 3.7 lmm x 4.95mm silicon area. The chip receives four external control signals: SYST\_CLK, providing the system clock, SYST-SLOT, defining the system slot boundaries, RESET, used to force switching elements and synchronization circuits into a know state at the beginning of operation, and ENABLE, used to enable the operation of the component. The chip also receives a low-speed clock LCLK (119.38 Mb/s) and a high-speed clock HCLK (157.95 Mb/s), to be used in set-up and transmission phases, respectively. From the external signal SYST-SLOT, an internal global signal CLKFRM is generated and used to define the local slot boundaries throughout the chip. Similarly, from RESET, an internal global signal CLR\_STATUS is generated. From CLKFRM and the clock information, a global signal FWD is generated to control the direction of the data flow on chip (i.e., FWD = 1, forward direction, data flow from inputs to outputs during path-establishment and

transmission phase; FWD = 0, reverse direction, data flow from outputs to inputs during feedback phase).

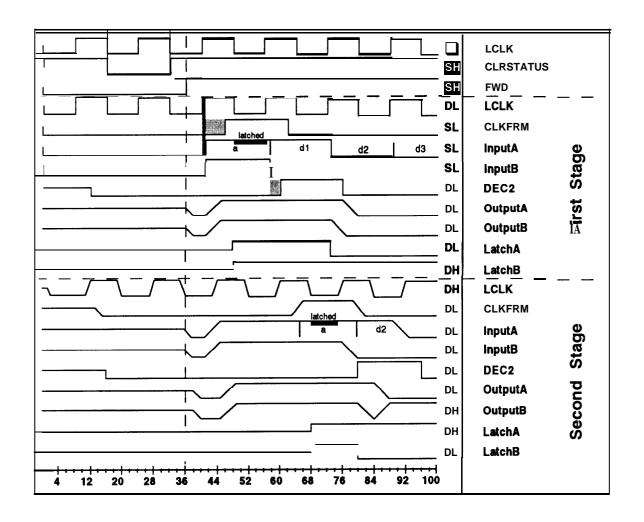

Here, we describe the banyan network circuit assuming that, at the beginning of the route set-up phase, headers are synchronized and aligned with one another. In Section 3.4 below, we discuss how synchronization and alignment of the headers is achieved (in the banyan-network component) during an alignment phase immediately preceding the route set-up phase.

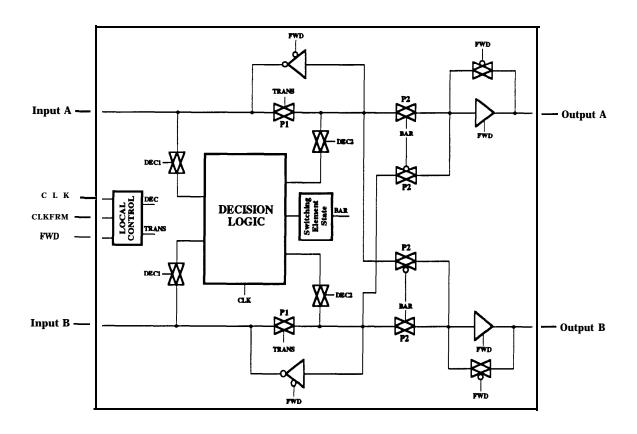

### b) 155.52 Mb/s Design — $2 \times 2$ Switching Element

The objective of achieving a 1-bit latency (i.e., the minimum possible latency) per stage in performing the switching algorithm imposes that the logic in each switching element must be capable of processing the address bit  $d_s$ , decide the state of the switching element and transmit the activity bit to the following stage in a single bit duration (resulting in the time diagram illustrated in Fig. 10). In order to achieve this objective, the decision logic must be streamlined. A block diagram of the  $2 \times 2$  switching element is depicted in Fig. 11. The area of the switching element is  $340 \mu m \times 130 \mu m$ .

A detailed time diagram of the signal behavior in two 2 x 2 switching elements in consecutive stages is shown in Fig. 12. In the first of the switching elements, at the beginning of the route set-up phase, the activity bits a of the headers arrive at the two inputs of the switching element (denoted as **InputA** and **InputB** in the figure). As CLKFRM goes high (the rising edge of CLKFRM is guaranteed to arrive after the activity bits, but before the latching edge of LCLK), the local counter is activated, to time the decision process. The internal signal **DEC1** goes high, so that the activity bits can proceed to the DECISION LOGIC, where they are latched; the internal signal TRANS goes low, separating the inputs of the switching element from the outputs; note that the internal signal DEC2 is low, and the output of the pass transistor **P1** is not actively driven, but

Fig. 10. Time **diagram** of the internal operation of the banyan network.

Fig. 11. Block diagram of a 2 x 2 switching element in the MSM banyan chip.

Fig. 12. Signal behavior during the decision process in a 2 x 2 switching element.

remains charged at the value it had before the falling edge of TRANS. During the following bit duration, the address bits  $d_s$  in the headers arrive at the switch and, since DEC1 is high, proceed to the DECISION LOGIC (in the case of Fig. 12, the header arriving at input A requests to be routed to output B, and the header arriving at input B requests to be routed to output A). The state of the switching element is decided, based on the activity bits and on the address bits, and latched in a storage element for the whole slot duration; the signal BAR is set accordingly (BAR = 1 for bar state, BAR = 0 for cross state), and the signal DEC2 goes high, enabling the activity bits to reach the outputs of the switching element and be transmitted to the following stage. Clearly, given the latency involved from the arrival of the address bit until the decision is completed, the activity bit does not occupy the whole bit duration. The requirement, however, is that the activity bit reaches the following stage before the latching edge of LCLK in that stage (it should be noted that LCLK is distributed by each switching element to the corresponding switching element in the following stage, and is also delayed while it traverses the switching element, thus making this requirement easier to meet).

In case of contention between two headers, conflict resolution is performed in order to select a winner, which is then properly routed; the activity bit of the loosing header is reset, and the header is misrouted. Note that a random selection of the winner would require the inclusion of pseudo-random-number generator circuits at each switching element (an addition which proves to be costly). Instead, in our realization of the banyan network, we set the state of the switching element to be the complement of the state assumed in the previous slot. Computer simulation has shown that this procedure is performance-wise equivalent to a random conflict-resolution algorithm for all traffic patterns of interest.

As the transmission of the activity bit is completed, DEC1 and DEC2 go low, disabling the decision logic, and TRANS goes high, allowing the remaining bits in the

header to pass through the switching element. CLKFRM is delayed by one bit and transmitted to the following stage to time the decision process in that stage. During the transmission of the feedback signal, FWD goes down, enabling the reverse path in the switching element. Finally, during the transmission phase, TRANS and FWD are high, enabling forward transmission of the data over the path that has been set-up.

The basic design of the switching element has to be slightly modified to realize the switching element to be used in the last stage of the banyan network. Specifically, the drivers in charge of the reverse path must be directly controlled by the latches in the decision logic where the activity bits (which have to be transmitted back to the input controllers) are stored. The switching element to be used in the randomization stage is also easily obtained from the basic design by removing the capability of resetting the activity bits in case of conflict. The randomization stage is operated by appending a randomly-generated bit in front of the destination address in the headers (this is done in the input controllers, as described in the following section).

We observe that in the MSM, the local switching address does not need to be conserved within the banyans (i.e., an address bit, once used in a switching element, can be dropped), since it is available in the input controllers. In contrast, in the Tandem Banyan Switching Fabric (TBSF) [Tob90b,Tob91], which uses a series rather than a parallel arrangement of the banyans, the switching address has to be cyclically shifted in each switching element, since it has to be used by every banyan in the series. In addition, the switching algorithm in the MSM is simpler than in the TBSF, since the conflict bit is not needed. These two factors translate into considerable area reduction (about 60%) in the switching element in the MSM, with respect to the switching element in the TBSF, implemented in the same technology [Chi9 1 ,Tob9 1]. The complexity of the switching element in the MSM is comparable to that of a switching element in the banyan network of the Batcher-Banyan switch [Mar90], although the latter does not necessitate feedback

or conflict-resolution circuitry (specifically, the switching element in the MSM banyan network, designed on our experimental, area-inefficient **0.8-µm BiCMOS** gate array, shows only a 30% area penalty compared with a custom-designed, on a **1.2-µm** CMOS technology, switching element in the Batcher-Banyan).

### c) 155.52 Mb/s Design — Banyan Network and Circuit-Simulation Results

Interconnections between switching elements at different stages are bidirectionally driven by **tri-state** drivers, since route set-up, feedback, and transmission are "half-duplexed" on the same interconnection lines (the connections between banyans and input controllers are also bidirectionally driven).

Since the on-chip data flow has a preferred direction from left to right (and from right to left during feedback), skews between clock and data signals can be minimized by accurately laying out the clock lines, so that they closely follow the data paths. The low-speed clock, used during the routing phase, is distributed to each row of switching elements, and the delay that it incurs while traversing a switching element is matched as closely as possible with the delay incurred by the data signals. Clearly, with the sea-of-gates approach used, matching data and clock has required a cell library specifically designed for this chip. The high-speed clock, used during the transmission phase, is distributed only to the driver circuits at the inputs and outputs of the banyan. This significantly reduces the capacitive load on the clock lines and facilitates the distribution of the high-speed clock. As far as power distribution is concerned, a mesh topology is used, as necessary to accommodate the dynamic power requirements at high data rates.

To further illustrate the operation of the banyan network, we consider a specific example in which three headers are dispatched to the banyan network chip. The signal behavior at the input of the banyan network and at two specific switching elements in the banyan is illustrated in Fig. 13. Three headers are dispatched to the banyan: *banyan*[1]

Fig. 13. Example of the signal behavior at the input of the banyan chip and at various switching element in the banyan network.

arrives at input 1 of the banyan and is destined to output 43; <code>banyan[16]</code> arrives at input 16 and is destined to output 46; <code>banyan[32]</code> arrives at input 32 and is destined to output 56. Headers are routed through the banyan. As shown in the figure, <code>banyan[1]</code> and <code>banyan[32]</code> reach the same switching element in the second stage of the banyan network, and are successfully routed to output A and output B of the switching element, respectively. At a switching element in the following stage, <code>banyan[1]</code> collides with <code>banyan[16]</code>. The former is properly routed to output B of the switching element, the latter is misrouted and its activity bit reset to 0. Then the headers proceed to the output of the banyan. During the feedback phase, the outcome of the routing phase (i.e., the activity bits of the headers at the end of the route set-up phase) are transmitted back to the input controllers.

Given the relatively low complexity of our design, we were able to simulate the whole 64 x 64 banyan network chip both at the behavioral and at the circuit level, at the speeds of interest, using ADEPT. Furthermore, we were able to extract the whole layout, and use SPICE to simulate the operation of the whole chip in a selected number of critical cases (in fact, given the structure of the banyan network, by submitting properly selected subsets of headers, critical paths and worst-case combinations of events in the circuit can be easily isolated). The maximum simulated operating speed, at nominal conditions, were 220 MHz during the route set-up phase, and more than 600 MHz during the transmission phase. Such maximum speeds well above the required operating speeds ensure wide design tolerances to accommodate variations in temperature and process parameters. However, these operating speeds are not adequate for the design for the 622.08 Mb/s.

#### d) 622.08 Mb/s Design

In the design for the 622.08 Mb/s, to achieve the required operating speeds of 293.87 MHz during the route set-up phase and 665.80 MHz during the transmission

phase, the following two modifications must be introduced in the design of the 2 x 2 switching element.

- i) Referring to the design of Fig. 11, the objective of implementing the feedback path in a way that is very simple and compact has led to the use of the series connection of pass transistors **P1** an P2. This solution, although perfectly adequate for the design for the 155.52 data rate, obviously degrades the voltage level on the node between the two transistors, since such node is not actively driven, and limits the achievable clock rate during transmission. To solve this problem, an active driver must be introduced between **P1** and P2; such driver must be tristate, in order not to interfere during the feedback phase.

- ii) In the design for the lower data rate, it was possible to control the skews of clock and data signals simply by matching their delays. Clearly, such a solution is only adequate up to a certain clock rate. To achieve higher clock rates in the route set-up phase, clock and data must be re-synchronized at each stage.

With these modifications, the maximum simulated operating speeds (at nominal conditions) were 310 MHz during the route set-up phase, and more than 800 MHz during the transmission phase. As mentioned above, in this case the design tolerances for the set-up phase are rather narrow, and a choice of G=8 (with corresponding clock rates of 180.84 Mb/s and 700.76 Mb/s during set-up and transmission phase, respectively) would allow a more robust design. Both these modifications increase the area of the switching element. As a result, the area of the switching element for the 622.08 Mb/s data rate is  $490\mu m \times 130\mu m$ , a 40% increase with respect to the switching element for the lower data rate.

## 3.1.4. Achievable Size with Current VLSI Technologies

At the high operating speeds of interest, in order to achieve stage-to-stage synchronization without complex re-synchronization of the signals, it is certainly highly desirable that the banyan network is implemented on a single chip. Here, we estimate the maximum size N of the banyan network that is achievable using current VLSI technology. The constraints on the achievable size are determined by area and pin limitations, and by the synchronization requirements at the operating speeds of interest (*i.e.*, stage-to-stage synchronization internally to the banyan, and synchronization of the banyan network with N input components and N output components).

We have described the implementation of a 64 x 64 banyan network on a single chip for both 155.52 Mb/s and 622.08 Mb/s data rates using a high-performance, yet relatively area-inefficient gate-array on a rather small silicon area. From this experience, as far as area is concerned, we estimate that a full-custom 128 x 128 network is certainly implementable on a single chip using current submicron technologies. At the high operating speeds of interest, the limitation on pins stems from power dissipation in the I/O's (which may be CMOS or ECL at 155.52 Mb/s, and are ECL at 622.08 Mb/s), rather than from the number of pins that can be accommodated on a chip. At 155.52 Mb/s, we estimate that the power dissipation in the I/O's of a 128 x 128 network is comfortably manageable (especially given that CMOS I/O's may be used). In contrast, at 622.08 Mb/s, the power dissipation in the ECL I/O's would be prohibitive. As far as synchronization is concerned, based on our experience, we estimate that at 155.52 Mb/s synchronization of a 128 x 128 network can be achieved; it is our opinion, however, that synchronization of a 256 x 256 network would be problematic. Note that, at 622.08 Mb/s, not only power dissipation on the I/O's would prevent the realization of a 128 x 128 network, but also synchronization in such a network would be difficult. In conclusion, we estimate that the maximum sizes

of banyan networks achievable with current technology are 128 x 128 at 155.52 Mb/s and **64** x **64** at 622.08 Mb/s.

## **3.2. The Input Controller Component**

# 3.2.1. Functionality and Design Issues

We recall from Section 2.2 above that, in a input controller with G = 1 receiving M input lines and controlling K banyans, the required functionality includes multiplexing up to M incoming packets per slot into the common memory, performing the dispatching algorithm, and retrieving and transmitting to the banyans up to K packets per slot (however, we have shown in [Chi93] that the number of packets transmitted to the banyans per slot can be limited to M+1 without visible degradation in performance). With input lines of bandwidth V, the required memory bandwidth is  $(M+K) \cdot V$  (again, it has been shown in [Chi93] that it can be reduced to  $(2M+1) \cdot V$  without noticeable effect on performance).

In a input controller with G > 1, the functionality must also include switching of each incoming packet into its requested group queue.

a)

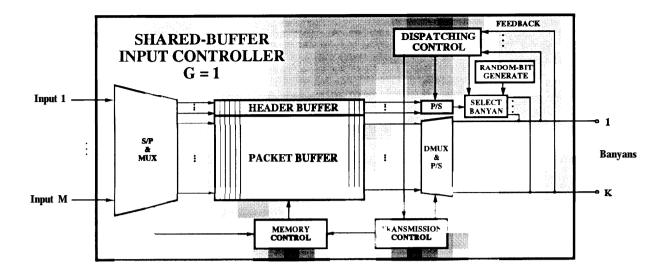

$$G = I$$

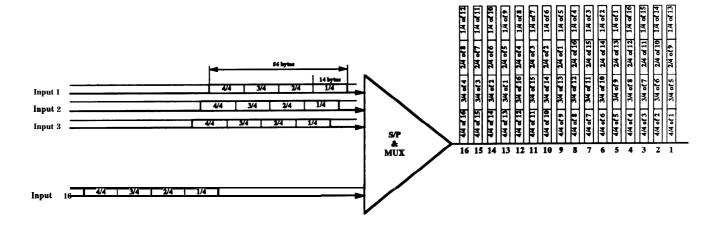

A block diagram of an input controller for G = 1, with M input lines, and controlling K banyans, is shown in Fig. 14. In order to achieve the required memory bandwidth, serial-to-parallel (S/P) conversion of the bit streams is necessary to multiplex incoming packets into the common memory. (Similarly, parallel-to-serial (P/S) conversion is required to retrieve packets from the memory.) At the beginning of each slot, the local switching header at the top of the input queue is retrieved from the memory; if no header is available, a dummy header with activity bit a = 0 is generated. The *select-banyan* circuit selects the first banyan in the sequence, and the header is dispatched to the

Fig. 14. Block diagram of the input component for G = 1.

banyan; during dispatching, a randomly-generated bit is appended in front of the destination address to be used to control the randomizers by pairs in front of the banyan network. Upon reception of the feedback signal (i.e., the value of the activity bit of the header after the path-establishment phase in the banyan has been completed), the **dispatching-control** circuit determines whether the header has been properly routed or not in the banyan. If the header has been misrouted, the dispatching-control circuit signals to the select-banyan circuit to dispatch the header to the following banyan. If the last banyan in the sequence has been attempted, the header is submitted to the first banyan at the beginning of the following slot. If the header has been successful, the dispatching-control circuit signals the successful dispatching to the select-banyan circuit, so that the following header in the queue, which has meanwhile been retrieved from the memory and prepared in serial form, is submitted to the following banyan; the dispatching control circuit also signals the successful dispatching to the *transmission-control* circuit, which is thereafter in charge of the transmission of the packet corresponding to the successful header. The **transmission-**

control circuit manages the demultiplexing from the memory, P/S conversion, and transmission to the banyans of up to K successful packets per slot.

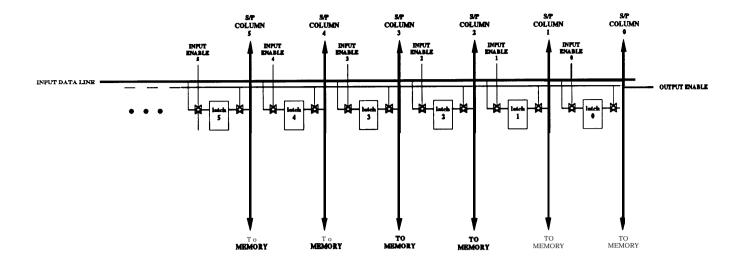

As discussed in detail in the following, the major design issues in the input controller are: i) the design of the S/P converters and multiplexing of the packets into the memory, and ii) the design of the P/S converters and demultiplexing of the packets from the memory.

The common memory is sequentially accessed, given the FIFO operation of the input queue; thus, memory control simply requires two pointers, sequentially incremented (and eventually cyclically rounded) after each memory access, to store the current write and read memory addresses. The two pointers are compared in order to detect a buffer overflow. If the buffer is full, the write operation of the packets into the memory is not performed, and packets are discarded. In this way, packets in the memory are given priority over incoming packets; of course, the reverse could be easily implemented as well. If there is no incoming packet on an input line in a given slot, the write operation corresponding to that line is not performed.

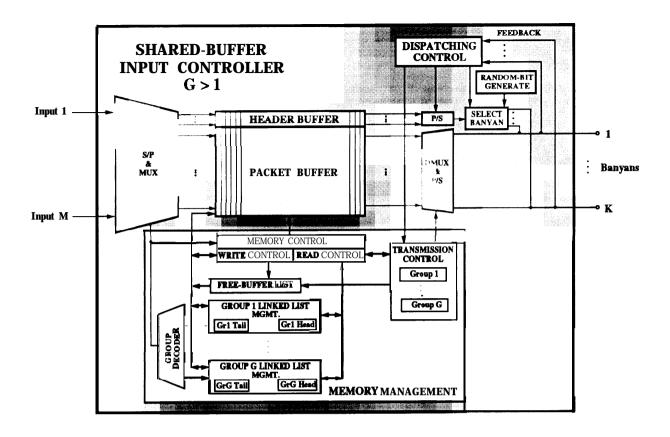

#### b) G > 1

With G > 1, the main design issue is whether the queues corresponding to each of the G groups of banyans share a common memory, or are accommodated in separate memories.

In the former case, the memory is randomly accessed and G linked lists of packets, one per each group queue, must be maintained within the memory, making memory management considerably more complex than in the case of sequentially-accessed memory. The required memory bandwidth is  $(M + \mathbf{K}) \cdot \mathbf{V}$ , as in the case of G = 1. A block diagram of the input component with group queues sharing a common memory is depicted in Fig. 15. The linked lists are formed by keeping the address of the packets at the head and at

Fig. 15. Block diagram of the input component for G > 1, with group queues sharing a common memory.

the tail of the lists in the **memory-management** circuit, and by storing, together with each packet, a pointer to the next packet in its list. For each incoming packet, the **group decoder** selects the linked list in which the packet has to be inserted, specified by the first log, G bits in the destination address of the packets. The address of an idle memory location is retrieved from the **free-buffer list**, and the packet is stored in that location by the **memory-control** circuit. Simultaneously, in order to append the new packet at the tail of the desired linked list, the corresponding **linked-list-management** circuit updates the address chain by having the pointer of the packet currently at the tail of the linked list point to the new packet, and by storing the address of the new packet as the new tail of the list. To read packets from the queue, the address of the packet at the head of each group queue is fed to the memory-control circuit, which controls demultiplexing and P/S

Fig. 16. Block diagram of the input component for G > 1, with group queues accommodated in separate memories.

conversion of the selected packets. Then, dispatching and transmission is performed in parallel for each group. If a packet is successfully dispatched, the corresponding linked list is updated and the next packet in the list is read from the queue. Once the transmission of a packet is completed, the address of its memory location is returned to the free-buffer list.

Alternatively, the G queues can be accommodated in separate memories; in this case, the circuitry described for G=1 is simply replicated for each of the G groups, as depicted in Fig. 16. Each group handles  $K_g$  banyan networks. Packets arriving at the M

inputs are broadcast to all G queues; then, in each S/P converter, it is assessed whether or not each incoming packet has to be written into the corresponding memory. With separate memories for each queue, each memory is sequentially accessed; thus, the memory control is simple. Furthermore, the required memory bandwidth in each memory is reduced to  $(M + K_g)$ . V. Finally, this organization is very convenient in case the component has to be partitioned into several chips, since controllers for different groups can be placed on separate chips, with no interaction between chips other than the broadcasting of the packets.

From this discussion, it is evident that separate memories for each of the group queues are, in general, a more convenient design choice than a single memory shared among all queues. In fact, given the relatively small values of G that are of practical interest, and given that the required buffer sixes in the input components are rather small with both shared and partitioned memories [Chi93], the simpler operation, reduced memory bandwidth, and ease of partitioning of the latter clearly outweighs the advantage in buffer requirements of the former.

## 3.2.2. Chip Design

We have designed the critical circuit components of an input controller with  $\mathbf{M} = 16$  input lines, to be used in a 1024 x 1024 MSM switch. Circuits for both the 155.52 Mb/s and the 622.08 Mb/s data rates have been designed.

Since our objective in this implementation exercise was to demonstrate the feasibility of the input controller, we have used for this design the same 0.8-µm BiCMOS sea-of-gates adopted for the banyan network chip. This experimental sea-of-gates features a small die-size and quite limited dimensions of the cell array (namely, 218 x 140 cells), so that the buffer memory and the required circuitry for multiplexing and demultiplexing packets cannot be fitted in an actual chip. In addition, the sea-of-gates approach is not a

suitable design choice for the type of circuitry necessary in the input component. For example, an SRAM memory cell implemented with this sea-of-gates has an area about 7 times larger than a comparable memory cell implemented on a custom 0.8-µm CMOS technology used in a shared-memory switch [Koz91]. Furthermore, given the constraints imposed by the sea-of-gates, matching the pitches of S/P and P/S converters with those of memory, sensing and decoding is problematic, and leads to inefficient area utilization. Despite these limitations of the adopted technology, we have nevertheless used it to design and simulate at the desired speeds the critical circuitries of the input component (namely, the multiplexing and S/P conversion of **M** lines, the memory and its control, and the P/S conversion and demultiplexing to handle  $K_g$  banyans). In fact, in terms of electrical behavior, the severe area penalty incurred with respect to a more suitable custom design approach makes this design a worst-case scenario; thus, such an implementation exercise is a good indication of the feasibility of the component. In order to estimate the silicon area and the number of chips required to realize an actual input component, we have analyzed the specifications of currently available custom technologies that have been used in shared-memory switches (which require similar types of functionalities) [Koz9 1,Sho91]; specifically, we estimate that the input component for M = 16 can be accommodated on a single chip.

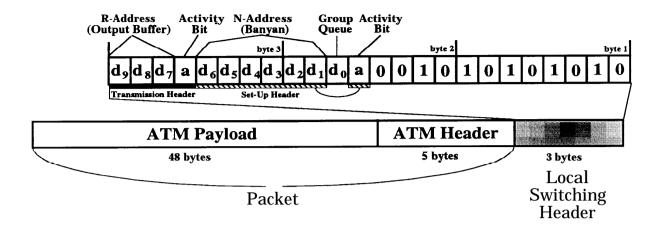

Prior to enter the input controller, each packet is processed by a header-conversion circuit which, based on the virtual circuit information in the ATM header, generates a local switching header and appends it in front of the packet. In order to deal with "easy numbers3" in the input controller, a 3-byte local header is actually appended to the 53-byte ATM cell.

It is common practice, in the design of this kind of circuits, to avoid to choose values of the design parameters that are prime numbers. Whenever possible, values that are powers of 2, or that form simple ratios with one another are preferred. Indeed, these small adjustments of the values of the design parameters often lead to simpler design of the multiplexing and demultiplexing circuits and simpler organization of the memory, as it will become evident in the sequel.

Fig. 17. Local switching header format for the 155.52 Mb/s design.

## a) 155.52 Mb/s Design — Chip Organization and Floorplan

In the design for the 155.52 Mb/s data rate, as depicted in Fig. 17, the local header comprises 1 address bit (*i.e.*, log, G, where G = 2, as derived in the previous section) to select the desired group queue, a 7-bit (*i.e.*, log, N address bits + 1 activity bit) header that is used to set-up the paths in the banyans, and a 4-bit header that is sent in the transmission phase through the banyan, consisting of 3 address bits that are used once the desired output buffer is reached to select among the  $\mathbf{R} = 8$  ports served by the buffer, plus 1 activity bit. All the remaining bits in the header are padded with a sequence of zeroes and ones, to facilitate slot synchronization. Due to the addition of the local switching header, the rate of the input lines is 158.24 Mb/s (=  $(56 \ \text{/} 53) \times 149.76 \text{Mb/s}$ ).

In our design for the 155.52 Mb/s ATM data rate, we have used G = 2, partitioned memories to accommodate the two group queues, and  $K_g = 26$  banyans per group; with these parameters, the required buffer size to achieve a packet loss rate in the input buffer below 10" under bursty traffic with L = 100, at 0.9 load, is 90 packet buffers per queue. Maximum parallelism in the memory access, equal to 448 (= 56 x 8) is used. Again, to deal

with "easy numbers" in the design, although there are only 26 banyans per group, we perform 28 memory read operations per slot, each 448-bit wide (indeed, note that  $56 \times 8 / 28 = 16$  is a simple ratio). Since 16 write operations (note:  $56 \times 8 / 16 = 28$ ) are also necessary, a 64.3-ns cycle-time memory is required (=  $448 / ((16 + 28) \times 158.24 \times 10^6))$ ). With the adopted BiCMOS sea-of-gates, for the relatively small memory sizes of interest, we have actually designed a 25-ns cycle-time memory (which is indeed required to meet the specifications of the design for the 622.08 Mb/s, as described below). With such memory, which is considerably faster than what needed in this design, a lower degree of parallelism in the memory access could be used. Given our purpose of investigating the feasibility of the component, however, we have kept maximum parallelism in the memory access, and used this memory at 64-ns cycle time.

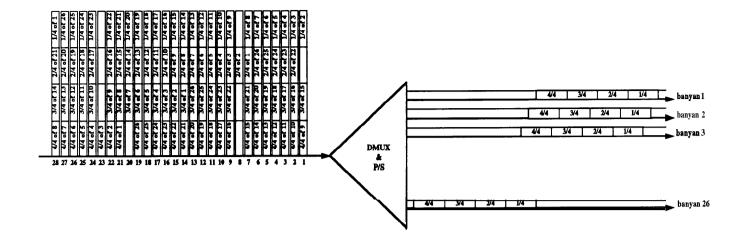

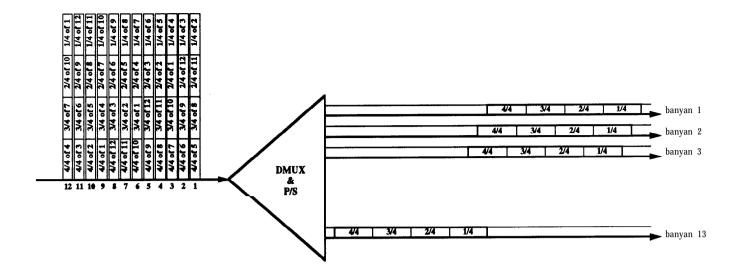

The floor-plan that we have used for the input-controller chip is depicted in Fig. 18. In this case, no circuitry is shared between the two group queues. For each queue, the memory has been arranged, as often done, in four banks of  $L/4 \times B$  cells, where L = 448 is the length of a packet plus the local header, and B is the buffer size per queue, which has been chosen equal to 128 (an "easy number" larger than 90). Each memory bank stores 14 bytes (i.e., one quarter of a packet plus local header, as indicated in Fig. 18) and consists of 7 blocks of 128Word x 16bit RAM. The memory uses a conventional 6-transistor CMOS SRAM cell, realized in one sea-of-gates cell. BiNMOS logic, because of its superior driving capabilities, is used in row decoding and in the drivers of row and column lines. Actually, with the available memory cell and BiNMOS logic to drive row and column lines, larger memory blocks could be used in the design for the 155.52 Mb/s data rate, thus reducing the area overhead in the memory. However, our intention to reuse the same memory organization in the design for the 622.08 Mb/s data rate made us arrange the memory to meet the specifications of that data rate, resulting in smaller memory blocks than strictly necessary.